| Citation: |

Yanan Lu, Leibo Liu, Jianfeng Zhu, Shouyi Yin, Shaojun Wei. Architecture, challenges and applications of dynamic reconfigurable computing[J]. Journal of Semiconductors, 2020, 41(2): 021401. doi: 10.1088/1674-4926/41/2/021401

Y N Lu, L B Liu, J F Zhu, S Y Yin, S J Wei, Architecture, challenges and applications of dynamic reconfigurable computing[J]. J. Semicond., 2020, 41(2): 021401. doi: 10.1088/1674-4926/41/2/021401.

Export: BibTex EndNote

|

Architecture, challenges and applications of dynamic reconfigurable computing

doi: 10.1088/1674-4926/41/2/021401

More Information-

Abstract

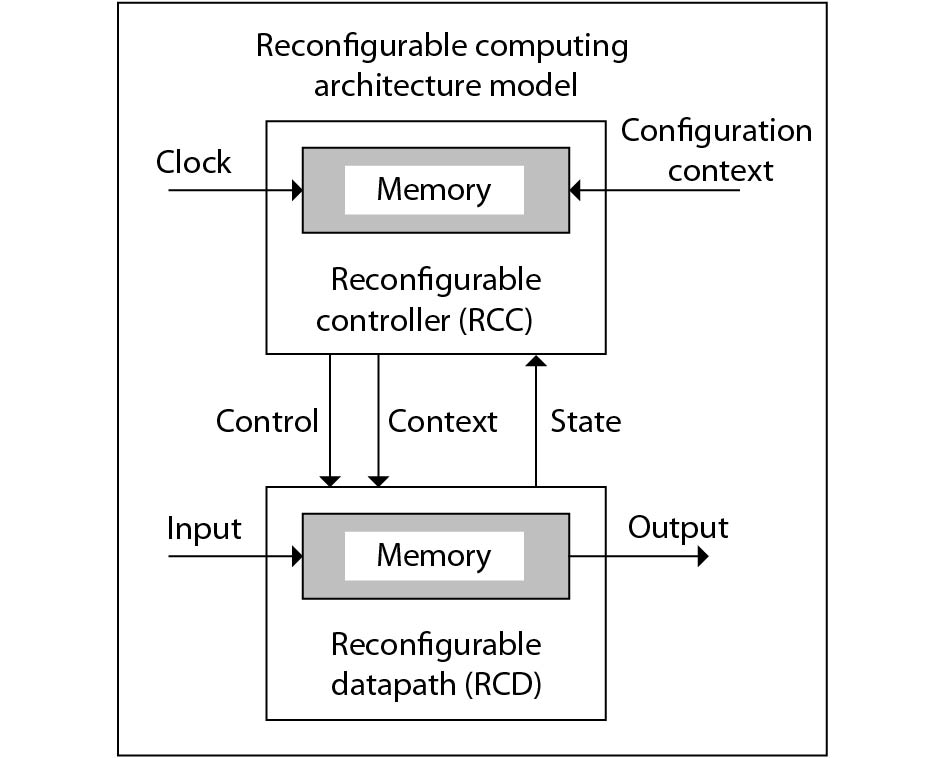

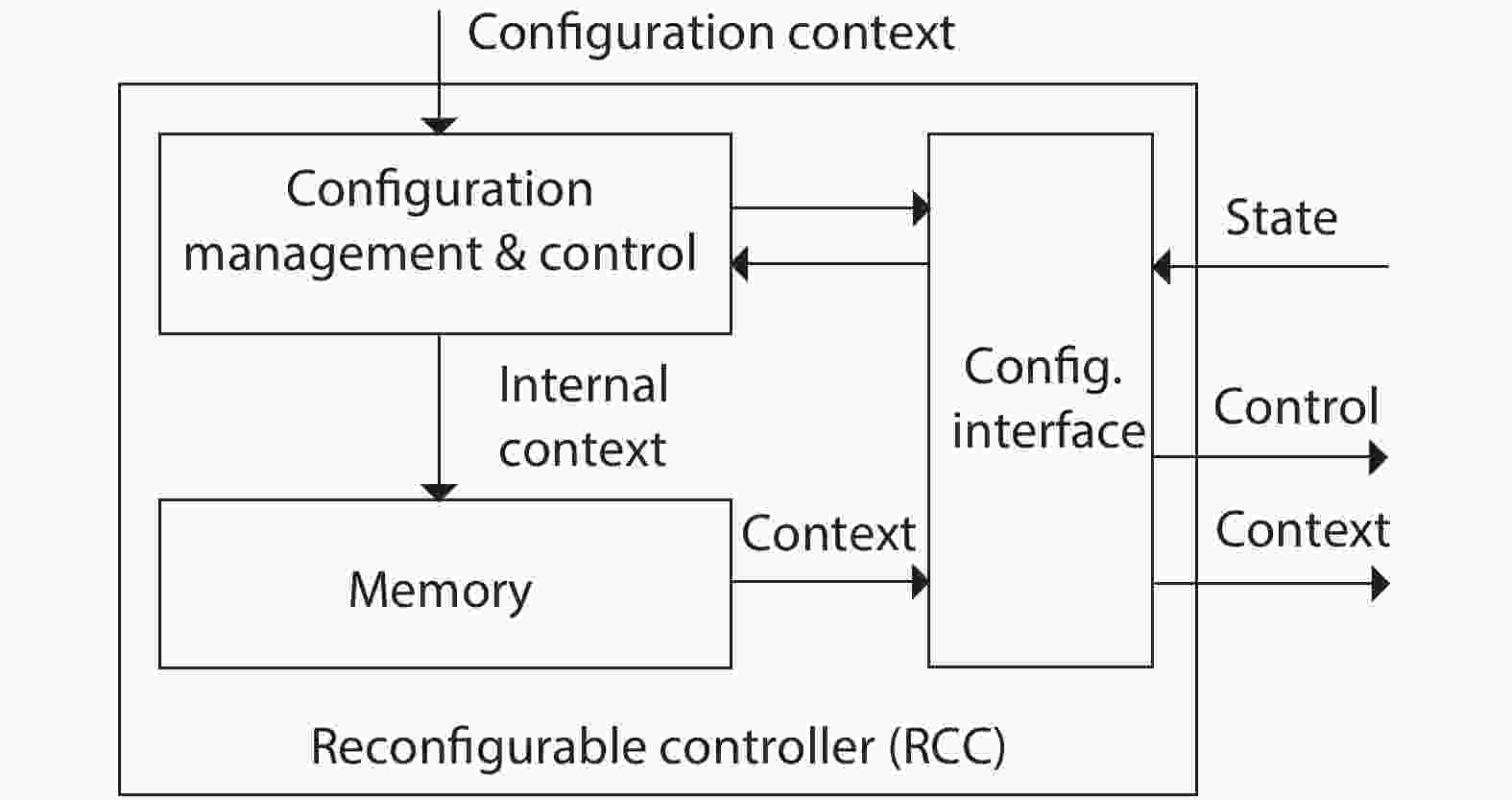

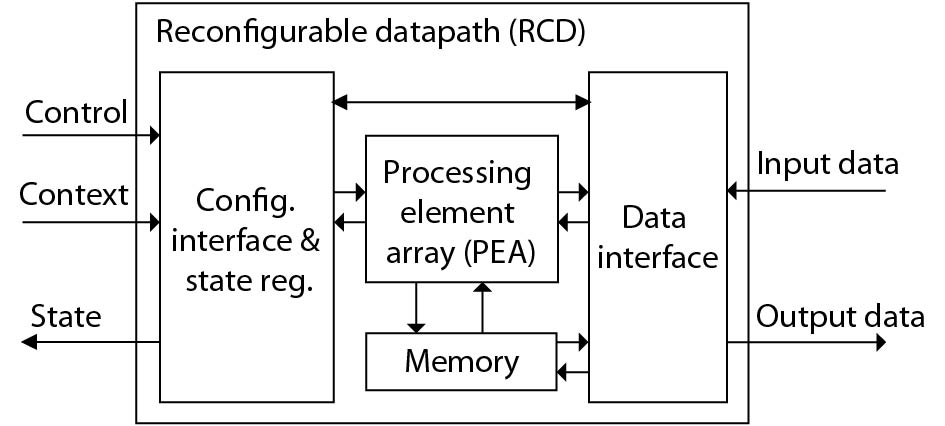

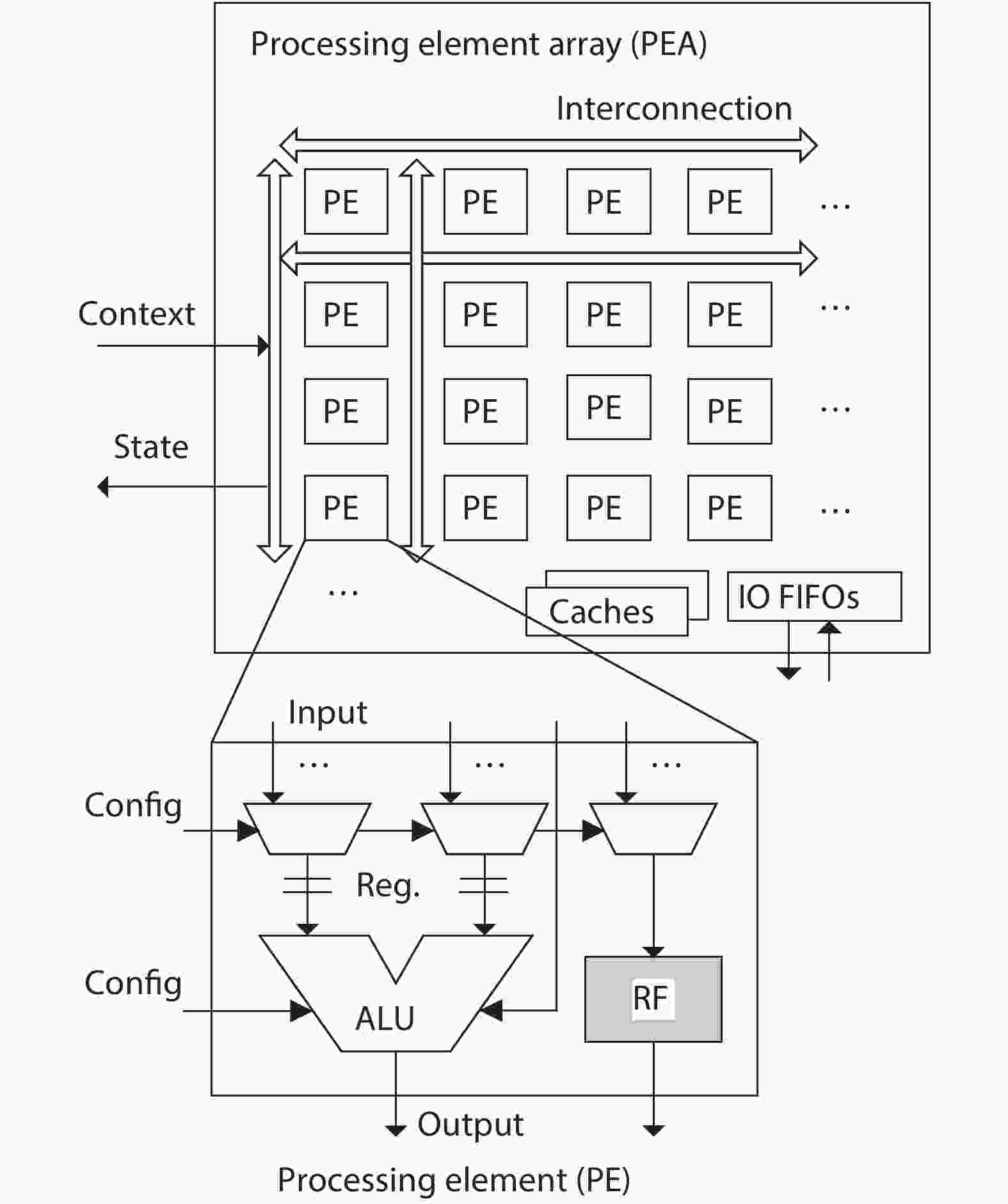

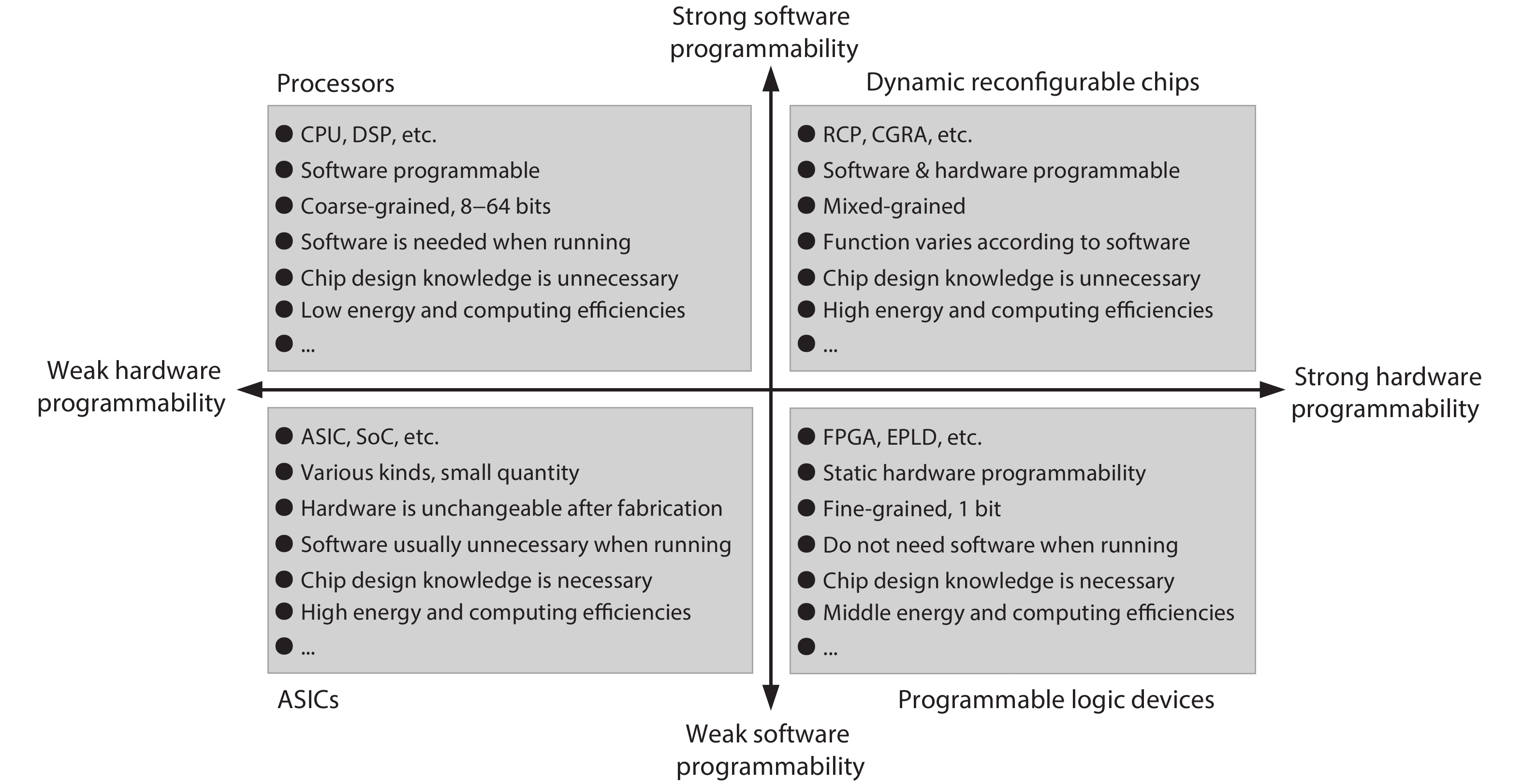

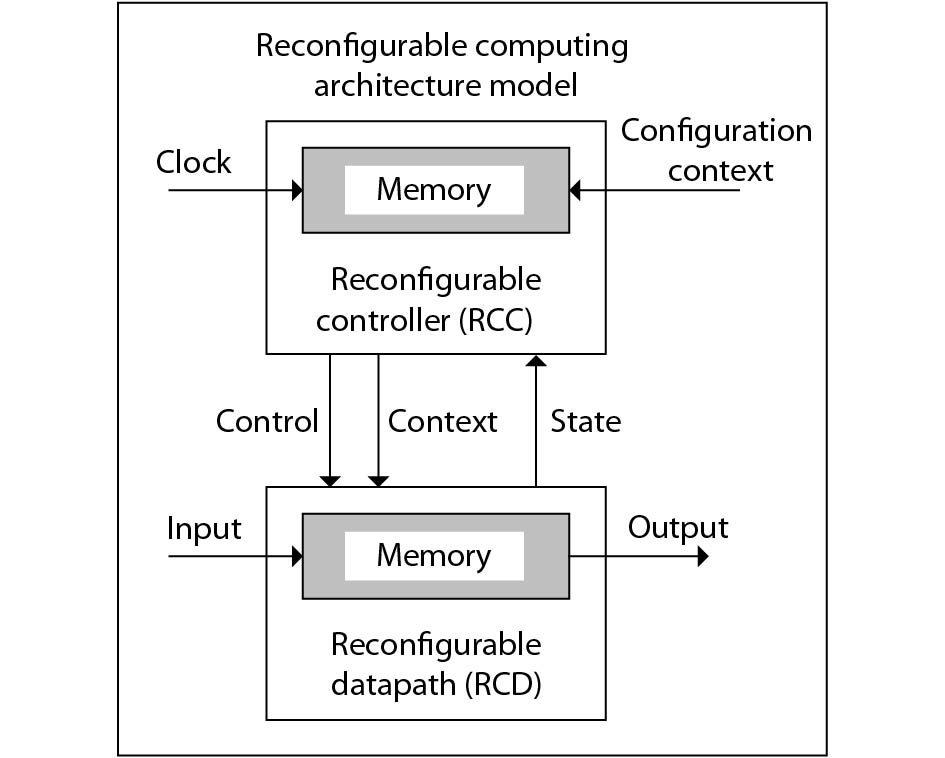

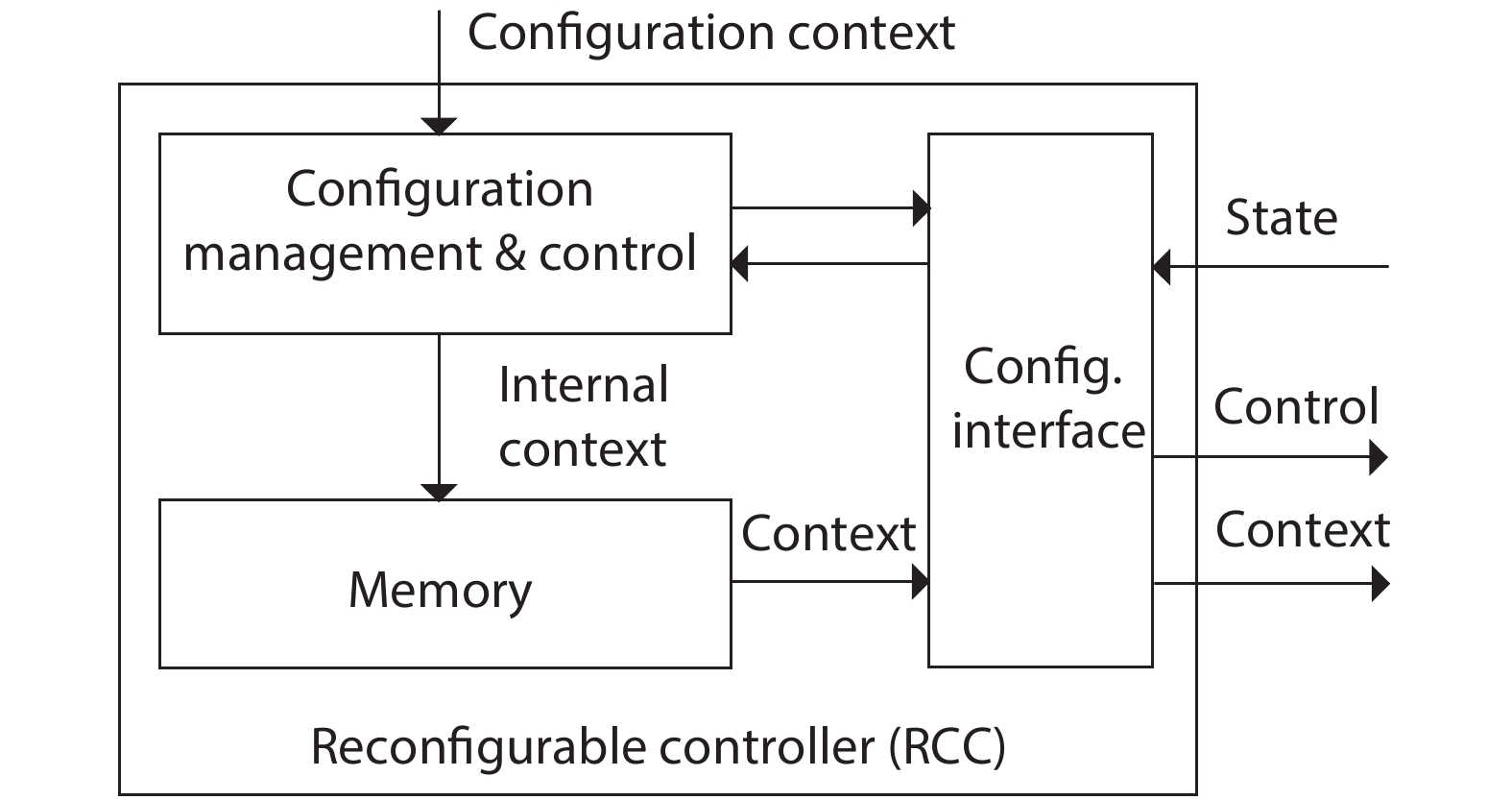

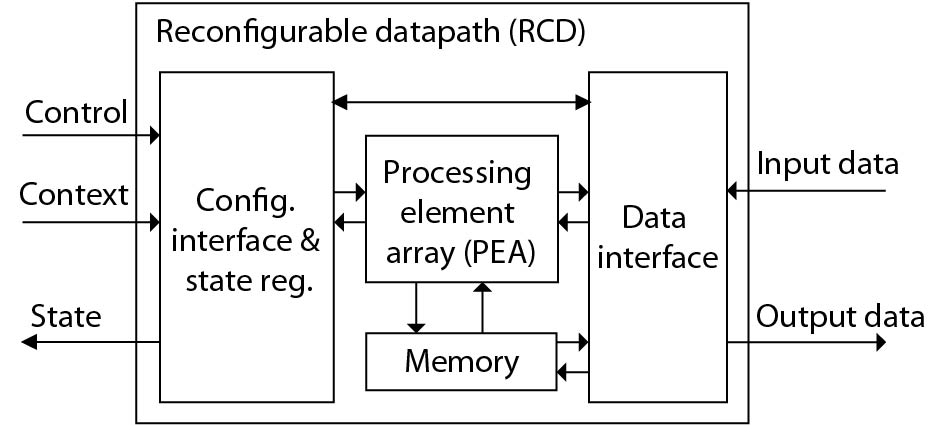

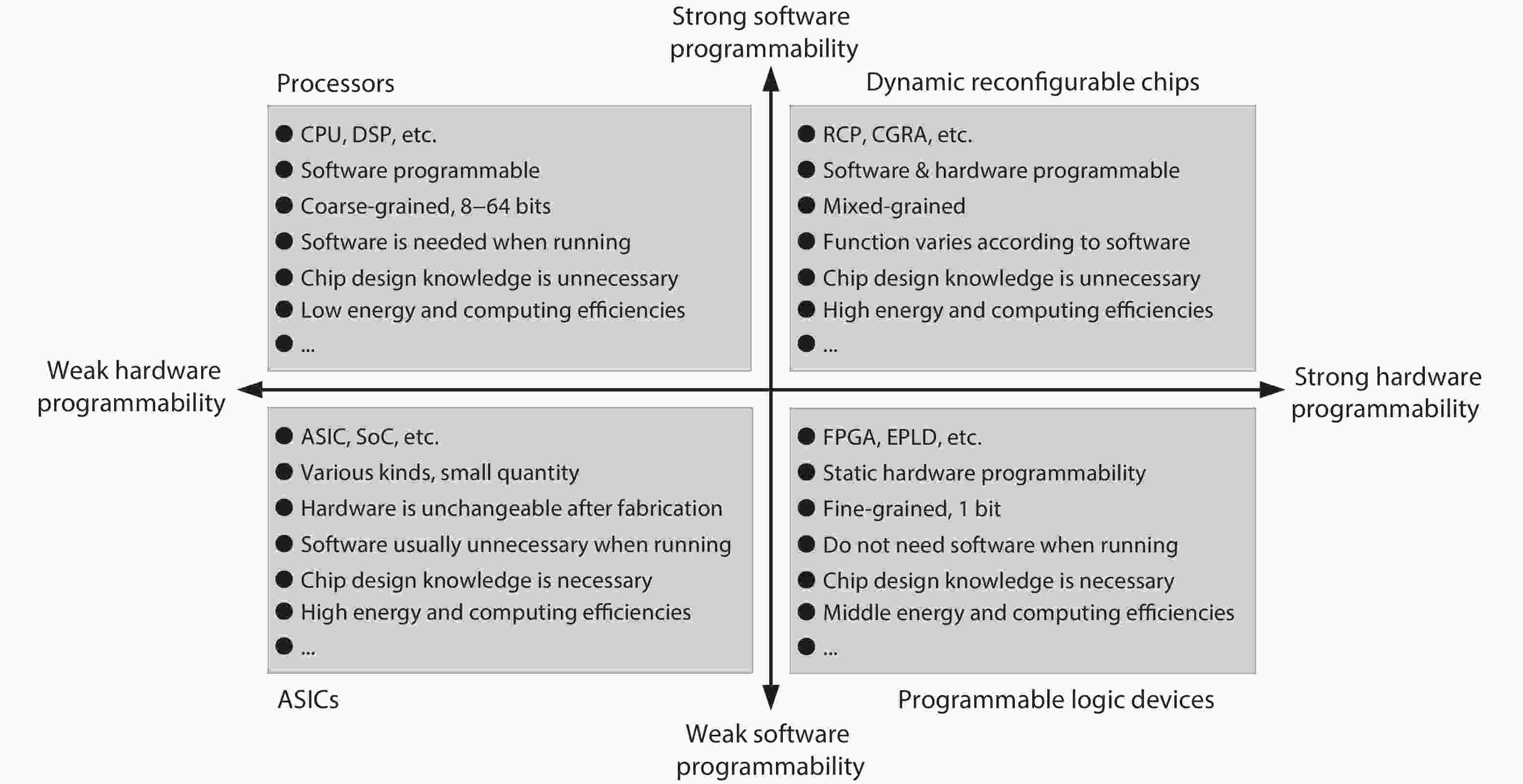

As a computing paradigm that combines temporal and spatial computations, dynamic reconfigurable computing provides superiorities of flexibility, energy efficiency and area efficiency, attracting interest from both academia and industry. However, dynamic reconfigurable computing is not yet mature because of several unsolved problems. This work introduces the concept, architecture, and compilation techniques of dynamic reconfigurable computing. It also discusses the existing major challenges and points out its potential applications.-

Keywords:

- reconfigurable computing,

- architecture,

- challenge,

- application

-

References

[1] Prabhakar R, Zhang Y, Koeplinger D, et al. Plasticine: a reconfigurable architecture for parallel paterns. ACM/IEEE International Symposium on Computer Architecture, 2017, 389[2] Nowatzki T, Gangadhar V, Ardalani N, et al. Stream-dataflow acceleration. ACM/IEEE International Symposium on Computer Architecture, 2017, 416[3] Nicol C. A coarse grain reconfigurable array (CGRA) for statically scheduled data flow computing. Wave Computing White Paper, 2017[4] [5] Kim S, Park Y H, Kim J, et al. Flexible video processing platform for 8K UHD TV. Hot Chips 27 Symposium, 2016, 1[6] [7] PACT. http://www.pactxpp.com/[8] [9] Suzuki M, Hasegawa Y, Yamada Y, et al. Stream applications on the dynamically reconfigurable processor. IEEE International Conference on Field-Programmable Technology, 2004, 137[10] Sato T, Watanabe H, Shiba K. Implementation of dynamically reconfigurable processor DAPDNA-2. IEEE VLSI-TSA International Symposium on VLSI Design, Automation and Test (VLSI-TSA-DAT), 2005, 323[11] Horowitz M. Computing's energy problem (and what we can do about it). IEEE International Solid-state Circuits Conference (ISSCC), 2014, 10[12] Tessier R, Pocek K L, Dehon A. Reconfigurable computing architectures. Proc IEEE, 2015, 103(3), 332 doi: 10.1109/JPROC.2014.2386883[13] Wijtvliet M, Waeijen L, Corporaal H. Coarse grained reconfigurable architectures in the past 25 years: Overview and classification. 2016 International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation (SAMOS), 2016, 235[14] Nowatzki T, Gangadhar V, Sankaralingam K, et al. Pushing the limits of accelerator efficiency while retaining programmability. IEEE International Symposium on High Performance Computer Architecture (HPCA), 2016, 27[15] Duranton M, Bosschere K D, Gamrat C, et al. The HiPEAC vision. European Network of Excellence on High Performance and Embedded Architecture and Compilation, 2017, 12[16] Estrin G. Organization of computer systems—the fixed plus variable structure computer. Proceeding of Western Joint Computer Conference, 1960, 33[17] Hartenstein R W, Hirschbiel A G, Riedmuller M, et al. A novel ASIC design approach based on a new machine paradigm. IEEE J Solid-State Circuits, 1991, 26(7), 975 doi: 10.1109/4.92017[18] Chen D C, Rabaey J M. A reconfigurable multiprocessor IC for rapid prototyping of algorithmic-specific high-speed DSP data paths. IEEE J Solid-State Circuits, 1994, 27(12), 1895 doi: 10.1109/4.173120[19] DeHon A, Wawrzynek J. Reconfigurable computing: what, why and implications for design automation. Proceeding of 36th ACM/IEEE Conference on Design Automation, 1999, 610[20] Xilinx Inc. All Programmable FPGAs [EB/OL]. http://www.xilinx.com/products/silicondevice/fpga/index.html [2014-7-7][21] [22] Wingbermuehle J G, Cytron R K, Chamberlain R D. Superoptimized memory subsystems for streaming applications. International Symposium on Field-Programmable Gate Arrays, 2015[23] Putnam A, Jan G, Michael G, et al. A reconfigurable fabric for accelerating large-scale datacenter services. IEEE Micro, 2015, 35(3), 10 doi: 10.1109/MM.2015.42[24] Goren S, Turk Y, Ozkurt O, et al. Achieving modular dynamic partial reconfiguration with a difference- based flow. Proceeding of the ACM/SIGDA International Symposium on Field Programmable Gate Arrays, 2013, 270[25] Coole J, G Stitt G. Intermediate fabrics: Virtual architectures for circuit portability and fast placement and routing. The eighth IEEE/ACM/IFIP international conference on Hardware/software codesign and system synthesis, 2010[26] Singh H, Lee M, Lu G, et al. MorphoSys: an integrated reconfigurable system for data-parallel and computation-intensive applications. IEEE Trans Comput, 2000, 49(5), 465 doi: 10.1109/12.859540[27] Mei B, Vernalde S, Verkest D, et al. ADRES: an architecture with tightly coupled VLIW processor and coarse-grained reconfigurable matrix. International Conference on Field Programmable Logic and Application (FPL), 2003, 61[28] Baumgarte V, Ehlers G, May F, et al. PACT XPP—A self-reconfigurable data processing architecture. J Supercomput, 2003, 26(2), 167 doi: 10.1023/A:1024499601571[29] Liu L, Deng C, Wang D, et al. An energy-efficient coarse-grained dynamically reconfigurable fabric for multiple-standard video decoding applications. IEEE Custom Integrated Circuits Conference, 2013, 1[30] Chin S A, Sakamoto N, Rui A, et al. CGRA-ME: A unified framework for CGRA modelling and exploration. IEEE 28th International Conference on Application-specific Systems, Architectures and Processors (ASAP), 2017, 184[31] Akbari O, Kamal M, Afzali-Kusha A, et al. PX-CGRA: Polymorphic approximate coarse-grained reconfigurable architecture. Design, Automation & Test in Europe Conference & Exhibition (DATE), 2018, 413[32] Duch L, Basu S, Pe O M, et al. i-DPs CGRA: an interleaved-datapaths reconfigurable accelerator for embedded bio-signal processing. IEEE Embed Syst Lett, 2019, 11, 50 doi: 10.1109/LES.2018.2849267[33] Voitsechov D, Port O, Etsion Y. Inter-thread communication in multithreaded, reconfigurable coarse-grain arrays. IEEE/ACM International Symposium on Microarchitecture (MICRO), 2018, 42[34] Amano H. A survey on dynamically reconfigurable processors. IEICE Trans Commun, 2006, 89(12), 3179[35] Zain-ul-Abdin, Svensson B. Evolution in architectures and programming methodologies of coarse-grained reconfigurable computing. Microprocess Microsyst, 2009, 22(3), 161 doi: urn:nbn:se:hh:diva-15050[36] Dehon A. Fundamental underpinnings of reconfigurable computing architectures. Proc IEEE, 2015, 103(3), 355 doi: 10.1109/JPROC.2014.2387696[37] Chattopadhyay A. Ingredients of adaptability: a survey of reconfigurable processors. VLSI Design, 2013, 10[38] Wang Y, Liu L, Yin S, et al. Hierarchical representation of on-chip context to reduce reconfiguration time and implementation area for coarse-grained reconfigurable architecture. Sci Chin Inform Sci, 2013, 56(11), 1 doi: 10.1007/s11432-013-4842-5[39] Liu L, Li Z, Yang C, et al. HReA: an energy-efficient embedded dynamically reconfigurable fabric for 13-dwarfs processing. IEEE Trans Circuits Syst II, 2017, 65(3), 381 doi: 10.1109/TCSII.2017.2728814[40] Asanovic K, Bodik R, Catanzaro B C, et al. The landscape of parallel computing research: A view from Berkeley. Technical report, Technical Report UCB/EECS-2006-183, EECS Department, University of California, Berkeley, 2006[41] Yin C Y, Yin S Y, Liu L B, et al. Front end design of task compiler for reconfigurable multimedia processor. J Beijing Univ Posts Telecommun, 2011, 34, 108[42] Li Y, Callahan T, Darnell E, et al. Hardware-software co-design of embedded reconfigurable architectures. Proceedings of Design Automation Conference, 2000, 507[43] So B, Hall M W. Increasing the applicability of scalar replacement. Proceedings of the ACM Symposium on Compiler Construction, 2004, 185[44] Beletska A, Bielecki W, Cohen A, et al. Coarse-grained loop parallelization: iteration space slicing vs affine transformations. Paral Comput, 2011, 37, 479 doi: 10.1016/j.parco.2010.12.005[45] Jiang Y C, Wang J F. Temporal Partitioning data flow graph for dynamically reconfigurable computing. IEEE Trans VLSI Syst, 2007, 15, 1351 doi: 10.1109/TVLSI.2007.909806[46] Yin C, Yin S, Liu L, et al. Temporal partitioning algorithm for a coarse-grained reconfigurable computing architecture. International Symposium of Integrated Circuit, 2009, 659[47] Aslam N, Milward M, Erdogan A, et al. Code compression and decompression for coarse-grain reconfigurable architectures. IEEE Trans VLSI Syst, 2008, 16, 1596 doi: 10.1109/TVLSI.2008.2001562[48] Yin S, Yin C, Liu L, et al. Configuration context reduction for coarse-grained reconfigurable architecture. IEICE Trans Inform Syst, 2012, E95-D, 335 doi: 10.1587/transinf.E95.D.335[49] Li Z, Liu L, Deng Y, et al. Aggressive pipelining of irregular applications on reconfigurable hardware. ACM/IEEE 44th Annual International Symposium on Computer Architecture (ISCA), 2017, 575[50] Liu D, Yin S, Liu L, et al. Polyhedral model based mapping optimization of loop nests for CGRAs. 50th ACM/EDAC/IEEE Design Automation Conference, 2013, 1[51] Zhu J, Liu L, Yin S, et al. A hybrid reconfigurable architecture and design methods aiming at control-intensive kernels. IEEE Trans VLSI Syst, 2015, 23(9), 1700 doi: 10.1109/TVLSI.2014.2349652[52] Liu L, Wang J, Zhu J, et al. TLIA: Efficient reconfigurable architecture for control-intensive kernels with triggered-long-instructions. IEEE Trans Paral Distrib Syst, 2016, 27(7), 1 doi: 10.1109/TPDS.2015.2477841[53] Wang Y, Liu L, Yin S, et al. On-chip memory hierarchy in one coarse-grained reconfigurable architecture to compress memory space and to reduce reconfiguration time and data-reference time. IEEE Trans VLSI Syst, 2014, 22(5), 983 doi: 10.1109/TVLSI.2013.2263155[54] Yang C, Liu L, Luo K, et al. CIACP: a correlation-and iteration-aware cache partitioning mechanism to improve performance of multiple coarse-grained reconfigurable arrays. IEEE Trans Paral Distrib Syst, 2016, 27(99), 1 doi: 10.1109/TPDS.2016.2554278[55] Chen Y H, Krishna T, Emer J S, et al. Eyeriss: an energy-efficient reconfigurable accelerator for deep convolutional neural networks. IEEE J Solid-State Circuits, 2017, 52(1), 127 doi: 10.1109/JSSC.2016.2616357[56] Farabet C, Martini B, Corda B, et al. NeuFlow: A runtime reconfigurable dataflow processor for vision. Computer Vision and Pattern Recognition Workshops, 2011, 109[57] Yin S, Ouyang P, Tang S, et al. 0.6-to-5.09 TOPS/W reconfigurable hybrid-neural-network processor for deep learning applications. Symposium on VLSI Circuits, 2017, C26[58] Fronte D, Perez A, Payrat E. Celator: a multi-algorithm cryptographic Co-processor. International Conference on Reconfigurable Computing and FPGAs, 2008, 438[59] Sayilar G, Chiou D. Cryptoraptor: High throughput reconfigurable cryptographic processor. IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2014, 155[60] Mei B, VeredaS F J, Masschelein B. Mapping an H.264/AVC decoder onto the ADRES reconfigurable architecture. International Conference on Field Programmable Logic and Applications, 2005, 622[61] Hartmann M, Pantazis V, Aa T V, et al. Still image processing on coarse-grained reconfigurable array architectures. J Sign Proces Syst, 2010, 60(2), 225 doi: 10.1007/s11265-008-0309-0[62] Ganesan M K A, Singh S, May F, et al. H.264 decoder at HD resolution on a coarse grain dynamically reconfigurable architecture. International Conference on Field Programmable Logic and Applications, 2007, 467[63] Kim S, Park Y H, Kim J, et al. Flexible video processing platform for 8K UHD TV. Hot Chips 27 Symposium, 2016, 1-1[64] Novo D, Moffat W, Derudder V, et al. Mapping a multiple antenna SDM-OFDM receiver on the ADRES coarse-grained reconfigurable processor. IEEE Workshop on Signal Processing Systems Design and Implementation, 2005, 473[65] Palkovic M, Cappelle H, Glassee M, et al. Mapping of 40 MHz MIMO SDM-OFDM baseband processing on multi-processor SDR platform. IEEE Workshop on Design and Diagnostics of Electronic Circuits and Systems, 2008, 1[66] Chen X, Minwegen A, Hassan Y, et al. FLEXDET: flexible, efficient multi-mode mimo detection using reconfigurable ASIP. IEEE International Symposium on Field-Programmable Custom Computing Machines, 2012, 69 -

Proportional views

DownLoad:

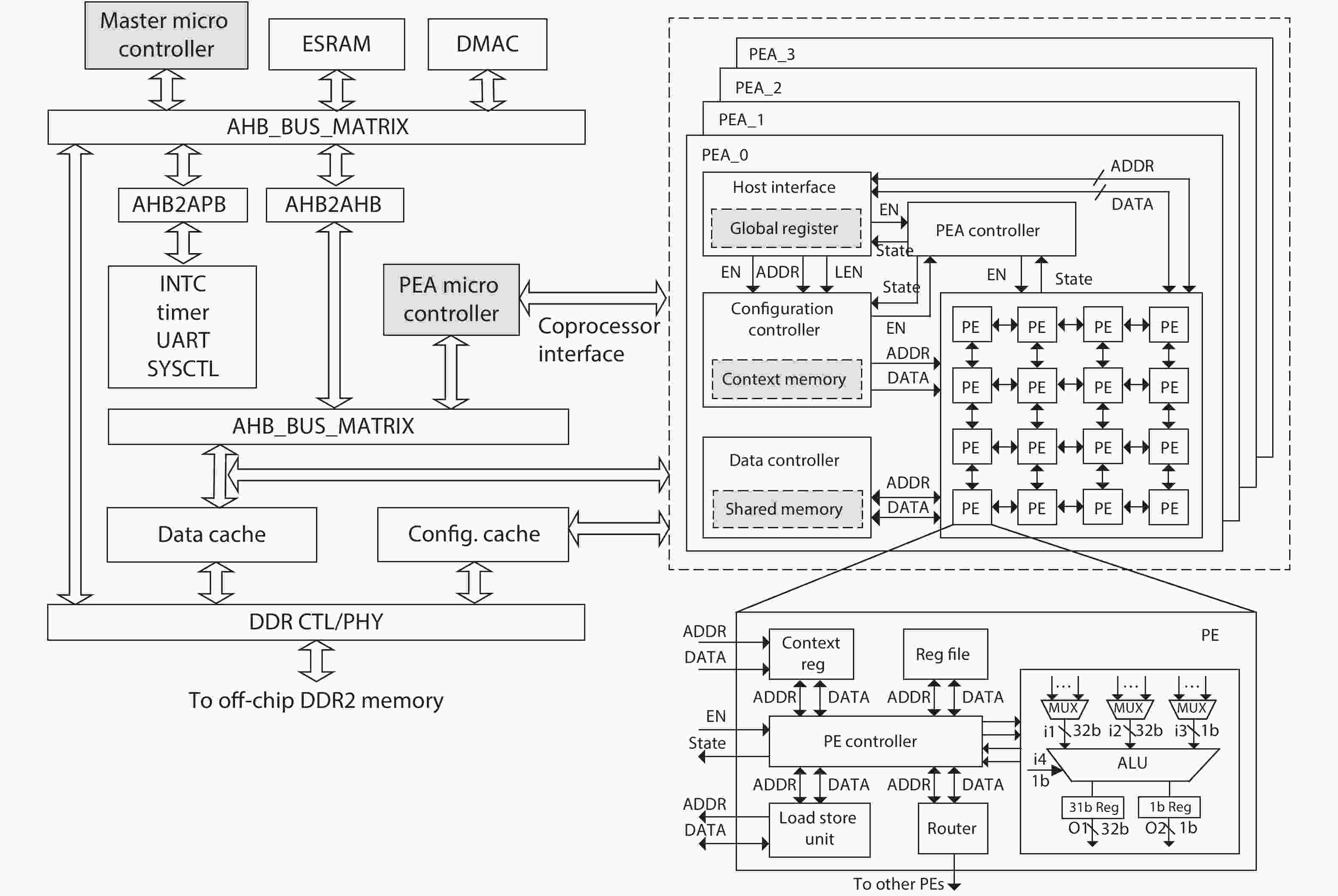

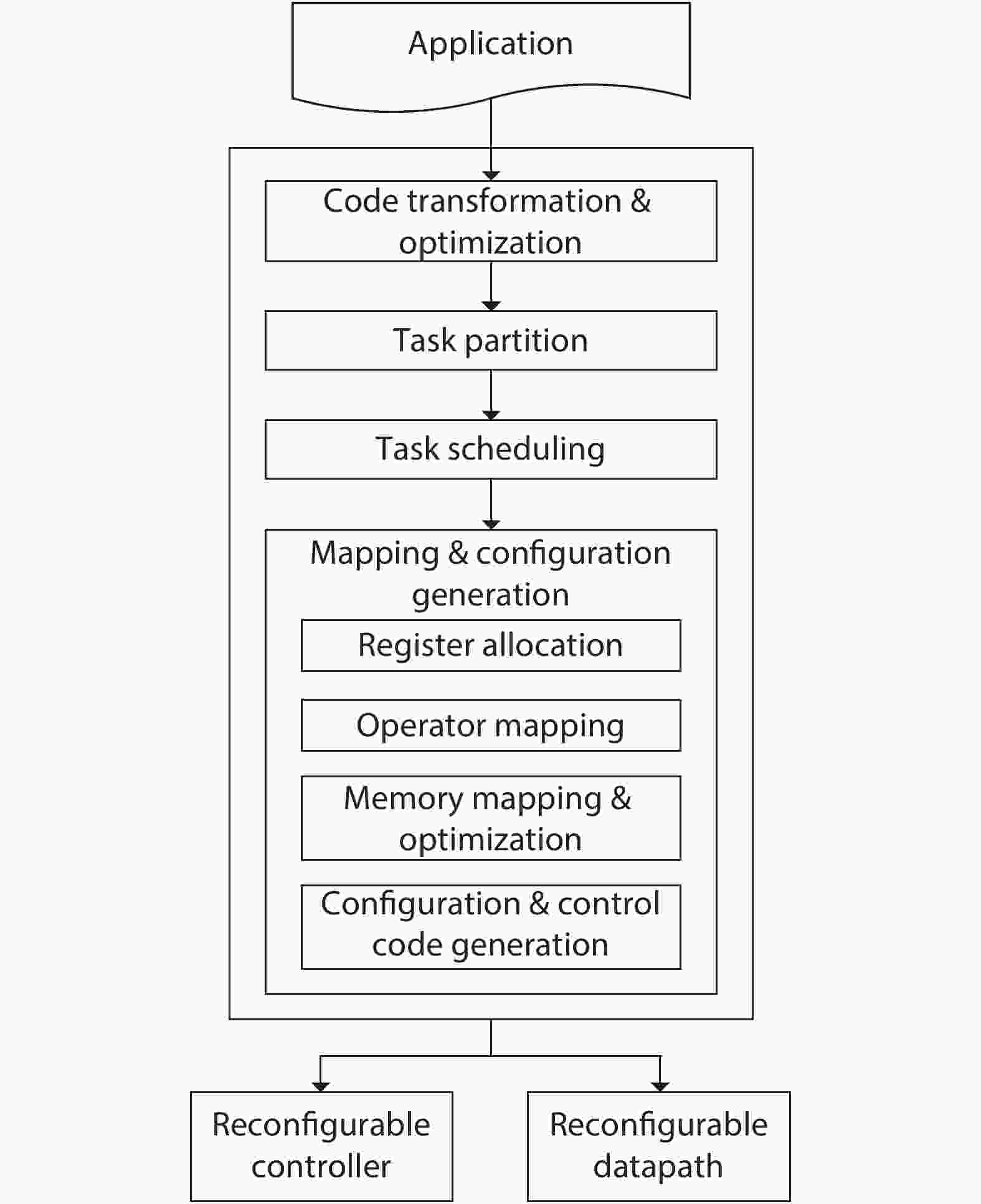

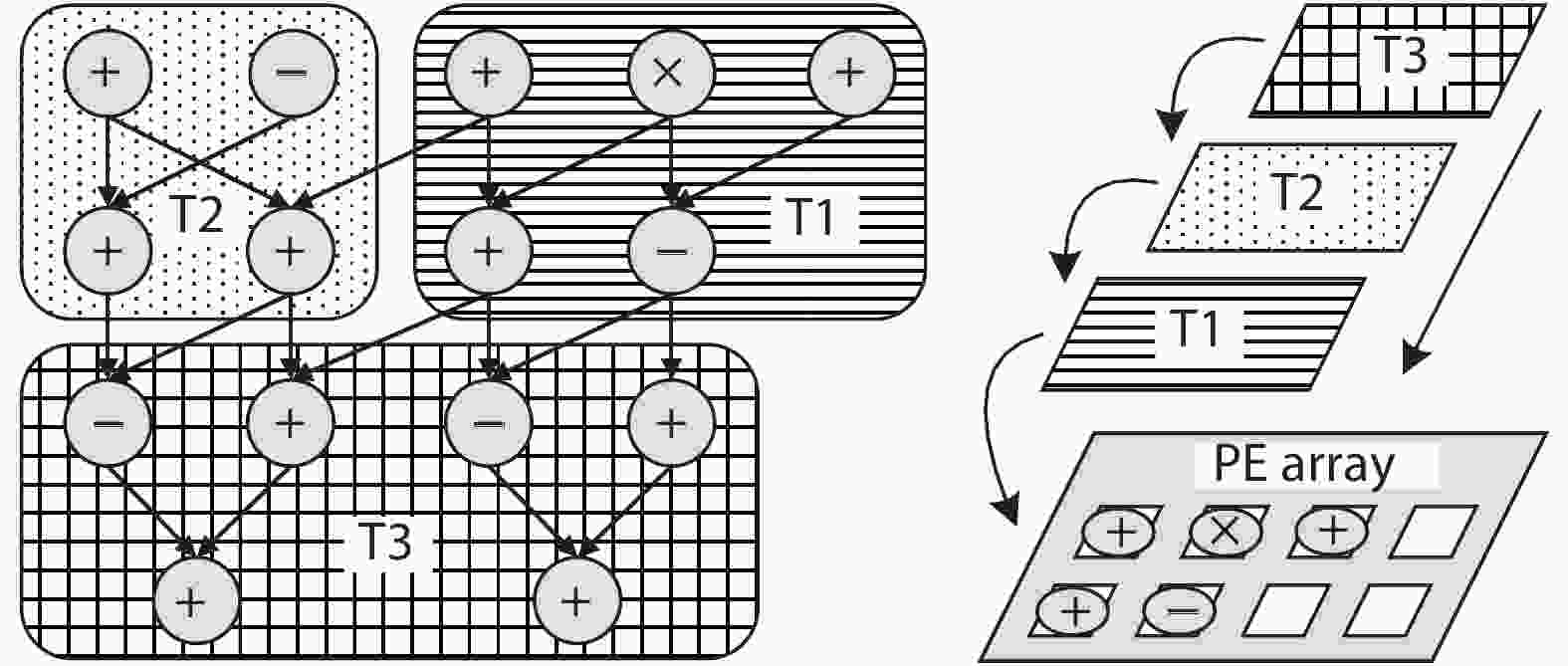

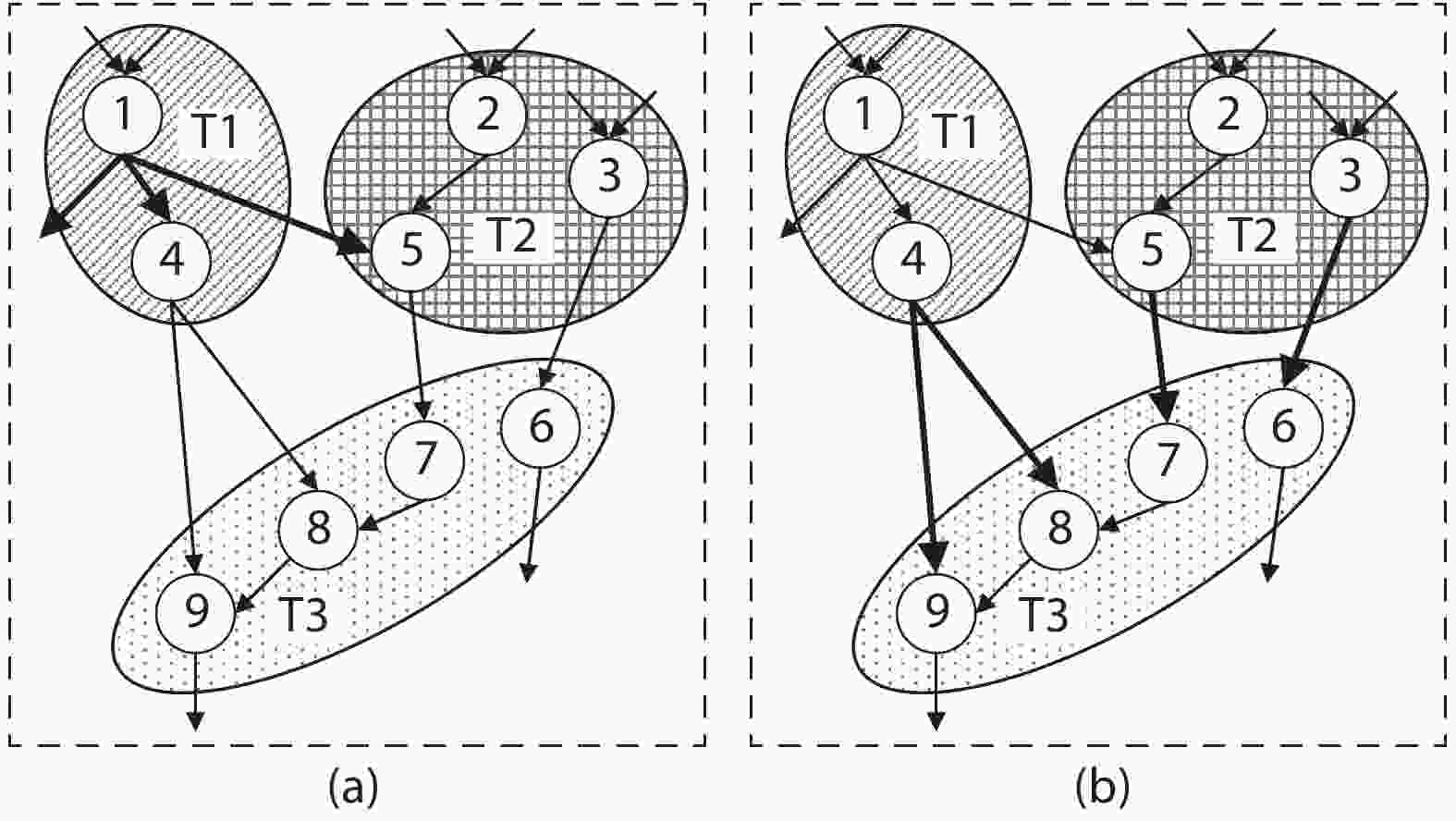

DownLoad: