# A General Method in the Synthesis of Ternary Double Pass Transistor Circuits

# Hang Guoqiang<sup>†</sup>

(Department of Information & Electronic Engineering, Zhejiang University, Hangzhou 310027, China)

Abstract: A general method for designing ternary circuits using double pass-transistor logic is investigated. The logical relation of each MOS transistor is formulated by using the transmission operation in order to make effective and practical use of the circuits. A way to generate ternary complementary and dual circuits by applying the complementarity and duality principles is presented. This new static ternary double pass-transistor logic scheme has some favorable properties: the use of standard CMOS process without any modification of the thresholds, a perfectly symmetrical structure, a full logic swing, the maximum possible noise margins, a less complex structure, and no static power consumption. HSPICE simulations using TSMC 0. 25µm CMOS technology and a 3V power supply demonstrate the effectiveness of the proposed design.

Key words: switching circuit theory; multiple-valued logic; logic synthesis; double pass-transistor logic

**EEACC:** 1100; 1265A; 2570D

**CLC number:** TN432 **Document code:** A **Article ID:** 0253-4177 (2006) 09-1566-06

## 1 Introduction

The need for multiple-valued logic (MVL) has been pointed out by researchers. Implementation of MVL using CMOS technology follows two major lines:current-mode and voltage-mode circuits. Although the current-mode approach has some benefits, it also has the obvious disadvantage of high power consumption due to the constant current flow. Voltage-mode MVL circuits have the advantage of low power consumption, but at the expense of complex fabrication and high cost[1~5]. Ternary logic has received more attention than the other types of MVL because of its low interconnection cost estimation and simple electronic circuit implementation method<sup>[6]</sup>. Several static<sup>[1,3,4]</sup> and dynamic<sup>[7~9]</sup> voltage-mode CMOS circuits for ternary logic have been proposed in recent years, but possible circuit realizations are still under investigation because the many schemes proposed are, for various reasons, far from optimum<sup>[9]</sup>. Static MVL circuit schemes require a complex process to obtain both depletion and enhancement devices[1~3] or multi-threshold voltages<sup>[4,5]</sup>. The dynamic MVL circuit proposed by Wu et al. [7] has a simple structure. However, it has a low noise margin, uses four power supplies, and also requires a complex process technology to obtain threshold-adjusted devices. The dynamic approach proposed by Herrfeld et al. [8] uses standard CMOS technology and has a high noise margin. However, the circuits are quite complex and must be buffered between two successive stages to avoid incorrect discharging in the evaluation phase. The last reported dynamic ternary circuit was developed by Toto et al. [9], which allows the realization of ternary circuits with a standard CMOS process, three supply voltages, and high noise margins. However, the floating output affects the circuit performance when the input is at logic '1'. While the dynamic approaches have some benefits, they also have known problems such as clock race and charge redistribution.

Double pass-transistor logic (DPL)<sup>[10]</sup> has a balanced input capacitance. This reduces the dependence of the delay on the input data. The symmetrical circuit configuration results in high logic functionality. The DPL is used to attain a full rail-to-rail swing, and is very attractive for high speed and low power applications<sup>[11]</sup>. In Ref. [12], a Karnaugh map-based method for synthesizing binary DPL circuits is developed. The DPL is first intro-

<sup>\*</sup> Project supported by the Natural Science Foundation of Zhejiang Province (No. Y105124)

<sup>†</sup>Corresponding author. Email: hanggq@mail. hz.zj.cn

duced to design MVL circuits by Hang[13] and Park et al. [14]. In Ref. [14], a neuron-MOS transistor is used to design literal functions.

In this paper, a new static voltage-mode CMOS circuit scheme using DPL to realize ternary logic and a general method for synthesizing ternary logic gates are proposed. Guided by the theory of transmission switches, the logical relation of each MOS transistor is formulated by using the transmission operation. A way to generate ternary complementary and dual circuits by applying the complementarity and duality principles is presented. It is simple and intuitive and can be extended to generate larger logic functions. The circuit scheme consists of complementary inputs/outputs and is thus a dual rail ternary logic. The most significant features are the use of standard CMOS processes without any modification of the thresholds, and a less complex structure. The ease of fabrication also makes MVL circuits more practical.

## Theory of transmission switches for a double pass-transistor

Based on the theory of transmission switches[4], the following two kinds of variables are introduced in multiple-valued circuits using a double pass-transistor.

- (1) Assume that , , ... are switching variables. Their values are taken to be T or F, only representing two states of MOS transistors, ON and OFF. The basic operations related to switching variables are AND ( ·), OR (+), and NOT(~), which are expressed as · , + , and , respectively, and are used to describe three physical situations: connections of element in serial, parallel, and switching state inverse.

- (2) Assume that  $x, y, \dots$  are signal variables. Taking a ternary signal as an example ,its logic value is taken as 0,1, and 2, which correspond to three different voltage signals, such as 0, 1.5, and 3V. They have a clear meaning of magnitude and can be identified by comparing their magnitude with a detection threshold t,  $t \in \{0, 5, 1, 5\}$ . For example, the two corresponding detection threshold voltages may be 0. 75 and 2. 25V, respectively. The basic operations related to signal variables are minimum ( ), maximum ( ), complement ( - ), literal  $(^{i}x^{i})$  operations, etc.

In order to describe the interaction between the on-off states of switching elements and signals, the following four basic operations can be introduced.

Low-threshold comparison operation:

$$x^{t} \stackrel{\triangle}{=} T, \quad x < t \\ F, \quad x > t$$

(1)

These two equations represent the low-acting switching characteristic of a pMOS transistor and the high-acting switching characteristic of an nMOS transistor, respectively.

Transmission operation:

$$s \triangleright \stackrel{\triangle}{=} \begin{cases} s, & = T \\ \phi, & = F \end{cases}$$

(3)

Here s is the transmitted source signal, and presents the switching state of a transmission switch network. If = T, the signal s is transmitted to the output. If = F, the switch network is off and its output is in the high-impedance state, which is denoted by the symbol  $\phi$ . To express the joining of the outputs of two (or more) transmission branches, the following operation can be further defined:

on operation:

$$s_1 \triangleright \# s_2 \triangleright \qquad \underbrace{ \begin{cases} s_1 \triangleright , & = F \\ s_2 \triangleright , & = F \end{cases}}_{}$$

(4)

In Eq. (4) ,the transmission operation ▷ takes priority over the union operation # . Also , if  $s_1$   $s_2$ and = T, a voltage conflict arises between sources  $s_1$  and  $s_2$ . This condition is not allowed.

Based on Eqs. (1) and (2) ,the following properties can be easily derived:

$$\begin{cases} x^{t} = \overline{x} \\ x = \overline{x} \end{cases}$$

$$(5)$$

Equation (5) indicates that the two threshold comparison operations can be transformed by complementing the signal variable.

The above theory of transmission switches lays a foundation for realizing the design technique of multiple-valued circuits using a double passtransistor at the switch level.

### 3 Circuit design of ternary unary **functions**

A literal circuit is the fundamental element in

MVL circuits. Taking ternary logic as an example, the truth table of ternary literals is shown in Table 1, and the following transmission operations can be obtained.

$${}^{0}x^{0} = x \triangleright x^{0.5} \# 0 \triangleright {}^{0.5}x = (6)$$

$${}^{2}x^{2} = 0 \triangleright x^{1.5} \# x \triangleright {}^{1.5}x = 0 \triangleright {}^{0.5}x \# x \triangleright x^{0.5}$$

(7)

Table 1 Truth table of the ternary literal functions

| There is the terminal internal remetions |                  |                  |            |      |

|------------------------------------------|------------------|------------------|------------|------|

| X                                        | 0 x <sup>0</sup> | 0 x <sup>0</sup> | $^2$ $x^2$ | 2 x2 |

| 0                                        | 2                | 0                | 0          | 2    |

| 1                                        | 0                | 2                | 0          | 2    |

| 2                                        | 0                | 2                | 2          | 0    |

To attain a full logic swing ,a source voltage of 0 and a high level must be transmitted by nMOS and pMOS transistors, respectively. By using Eq. (5), the last item of  $^2\,x^2$  can be easily derived. In the above two equations, low-threshold operation is realized by pMOS, while the high-threshold operation is realized by nMOS. Using the complementarity principle, the complementary logic function in ternary double-pass logic can be generated after the following modifications are made to the true function:

- (1) Swap pMOS and nMOS transistors;

- (2) Invert all pass and gate signals.

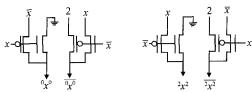

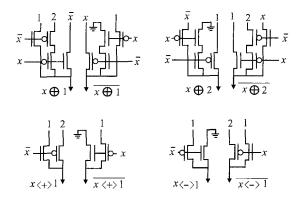

According to the above transmission operations and following the complementarity principle, the ternary literal gates can be designed as shown in Fig. 1. Their behavior is straightforward. The circuit realization of  ${}^{0}x^{0}$  is also called a negative ternary inverter (NTI) ,and the circuit realization of  ${}^{2}x^{2}$  is also called a positive ternary inverter (PTI)  ${}^{[1.7]}$ .

Fig. 1 Circuit realizations of ternary literal functions

Table 2 gives some ternary unary functions, where  $x \oplus 1$  and  $x \oplus 2$  are called the ternary cycling function and the inverse cycling function respectively, and x + 1 and x - 1 are called the operations of ternary truncated sum 1 and truncated difference 1, respectively. Their transmission functions are expressed as:

$$x \oplus 1 = 1 \triangleright x^{0.5} \# 2 \triangleright_{-}^{0.5} x \cdot x^{1.5} \# x \triangleright_{-}^{1.5} x

= 1 \triangleright_{-}^{1.5} x \# 2 \triangleright_{-}^{0.5} x \cdot x^{1.5} \# x \triangleright_{-}^{1.5} x (8)

x \oplus 2 = x \triangleright_{-}^{0.5} \# 0 \triangleright_{-}^{0.5} x \cdot x^{1.5} \# 1 \triangleright_{-}^{1.5} x

= x \triangleright_{-}^{0.5} \# 0 \triangleright_{-}^{0.5} x \cdot x^{1.5} \# 1 \triangleright_{-}^{1.5} x

= x \triangleright_{-}^{0.5} \# 2 \triangleright_{-}^{0.5} x = 1 \triangleright_{-}^{1.5} x \# 2 \triangleright_{-}^{0.5} (9)

x + 1 = 1 \triangleright_{-} x^{0.5} \# 2 \triangleright_{-}^{0.5} x = 1 \triangleright_{-}^{1.5} x \# 2 \triangleright_{-}^{1.5} (10)

x - 1 = 0 \triangleright_{-} x^{1.5} \# 1 \triangleright_{-}^{1.5} x = 0 \triangleright_{-}^{0.5} x \# 1 \triangleright_{-}^{0.5} (11)$$

Table 2 Truth table of the ternary unary functions

x  $x \oplus 1$   $x \oplus 2$  x + 1 x - 1

0

1

2

1

0

1

2

0

2

0

2

0

1

2

1

The last item in every expression is derived by using Eq. (5) to meet the demand that the low level 0 and the high level 2 must be transmitted by nMOS and pMOS transistors, respectively. Notice that the mediate source 1 may be transmitted by nMOS or pMOS transistors; thus the conflict between two sources 0 and 1 or 1 and 2 should be avoided. From Eqs. (8) and (9), it can be seen that the connections of two pMOS in serial and two nMOS in serial are used to transmit 2 and 0, respectively. Their complementary logic functions can be realized by the complementarity principle. The circuit realizations corresponding to the above equations and their complementary functions are shown in Fig. 2.

Fig. 2 Circuit realizations of ternary unary functions

# 4 Circuit design of ternary two-variable functions

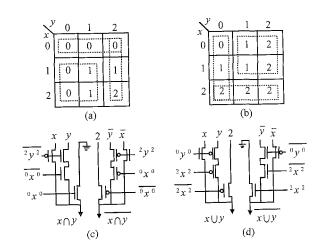

The above proposed ternary unary gates can be used to construct complex gates. For example, Figures 3(a) and (b) show the Karnaugh map for a 2-variable ternary AND function and OR function, respectively. According to the coverage shown in Figs. 3(a) and (b), the following transmission operations can be obtained:

In Eq. (12)  $,0

ightharpoonup^{1.5} \overline{x}$  means that the nMOS turns on and the source signal  $\underline{0}$  is transmitted to the output only when  $\underline{x} = 0$  (i. e.  $\underline{x} = 2$ ). Thus ,it can be rewritten as  $0

ightharpoonup^{1.5} \underline{x} = 0

ightharpoonup^{1.5} ({}^{0} x^{0}) = 0

ightharpoonup^{0.5} ({}^{0} x^{0})$ . Similarly , $x|_{x=1,2}

ightharpoonup^{0.5}$  means that the pMOS is on and x=1 or 2 is transmitted to the output only when y=2 (i. e. y=0). Thus , $x|_{x=1,2}

ightharpoonup^{0.5} = x$  |  $x=1,2

ightharpoonup^{0.5} \underline{y}$  on  $x=1,2

ightharpoonup^{0.5} \underline{y}$  on  $x=1,2

ightharpoonup^{0.5} \underline{y}$  stands for the connection of two nMOS transistors in serial to transmit signal y=0 or x=1 only when x=1 or x=1

$$x y = 0 \triangleright^{0.5} {\binom{0}{x^{0}}} # x \mid_{\frac{x=1,2}{2}} \triangleright (\overline{\frac{y^{2}}{y^{2}}})^{0.5} # y \mid_{y=0,1} \triangleright [\overline{\frac{0.5}{2}} (\overline{\frac{y^{2}}{y^{2}}}) \cdot \overline{\frac{0.5}{2}} (\overline{\frac{y^{2}}{x^{0}}})]$$

(14)

In the same way, Equation (13) can be rewritten as follows:

$$x y = 2 \triangleright (\overline{{}^{2} x^{2}})^{0.5} \# x \mid_{x=0,1} \triangleright^{0.5} ({}^{0} y^{0})$$

$$\# y \mid_{y=1,2} \triangleright [({}^{2} x^{2})^{0.5} \cdot ({}^{0} y^{0})^{0.5}]$$

(15)

The circuit realizations corresponding to the above two equations are shown in Figs. 3(c) and (d) respectively, where some input literal signals are produced from the circuits shown in Fig. 1, and the ternary NAND and NOR gates are generated from their true functions by the complementarity principle. As can be seen from Fig. 3, it is perfectly symmetrical. This results in a balanced input capacitance and reduces the dependence of the delay time on data. It is also worth noting that only two external supply voltages ( $V_{\rm DD}$  and GND) are needed, while the proposed circuit only acts as a middle block in the ternary system. The symmetrical structure makes it easy to realize other ternary complex functions.

In fact, because AND-OR is the dual logic function, ternary OR circuits can be formed from

Fig. 3 (a) K-map for ternary AND operation; (b) K-map for ternary OR operation; (c) Ternary AND/NAND gate; (d) Ternary OR/NOR gate

ternary AND circuits by using the duality principle. The dual logic function in ternary double-pass logic can be generated after the following modifications:

- (1) Swap pMOS and nMOS transistors;

- (2) Swap logic 2 and logic 0, while logic 1 remains unchanged;

(3) Swap

$$x^i$$

and  $x^i$  and  $x^i$   $(x^i)$ ,  $y^i$  and  $x^i$   $(x^i)$ ,

The above duality principle can also be used to verify the circuit realizations of ternary unary functions shown in Fig. 2. For example,  $x \oplus 1$  and  $x \oplus 2$ , x + 1 and x - 1 are dual logic functions.

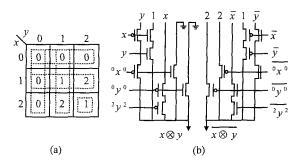

From the above discussion, it can be seen that the synthesis efficiency is enhanced by the complementarity and duality principles. Using these principles, for example starting from the realization of a ternary AND circuit with simple transformations, one can obtain complementary and dual functions (ternary NAND, OR/NOR) using the same circuit structure, improving the library versatility. As another example, Figure 4 (a) gives the Karnaugh map for ternary mod-3 multiplication. According to the coverage shown in Fig. 4 (a), the following transmission operations can be obtained:

$$x \otimes y = 0 \triangleright [^{0.5}(^{0}y^{0}) + ^{0.5}(^{0}x^{0})] \# x |_{x=1,2} \triangleright [(^{0}y^{0})^{0.5} \cdot (^{2}y^{2})^{0.5}] \# y |_{y=2} \triangleright [(^{0}x^{0})^{0.5} \cdot x^{1.5}] \# 1 \triangleright (^{1.5}x \cdot ^{1.5}y)$$

(16)

Based on Eq. (16), the logic function  $x \otimes y$  is first mapped into circuit realization. Then, using the

same circuit structure, swapping pMOS and nMOS transistors, and inverting all <u>pass</u> and gate signals, its complementary function  $x \odot y$  can be easily obtained as shown in Fig. 4(b).

Fig. 4 (a) K-map for ternary mod-3 multiplication; (b) Circuit realization of ternary mod-3 multiplication

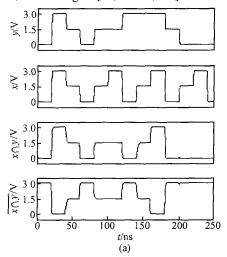

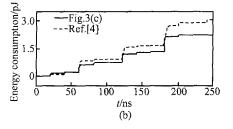

The proposed circuits have been simulated using HSPICE and the model parameters of a TSMC 0. 25µm CMOS process. Taking the ternary AND/NAND gate shown in Fig. 3 (c) as an example, the transient simulation results with a 0. 1pF load at each output node, are given in Fig. 5 (a). In the simulation, the voltages [0,1.5V,3V] are taken to

Fig. 5 (a) Simulated transient characteristics of ternary AND/ NAND gate; (b) Energy consumption curve

represent the logic values [0,1,2]. The simulation results demonstrate that the full logic swing and the maximum possible noise margins are attained due to the usage of both pMOS and nMOS pass transistors. The energy dissipation curve is given in Fig. 5 (b). For contrast, the energy dissipation curve of the ternary NAND gate reported in Ref. [4] is also given in Fig. 5(b) under the same simulation conditions except for modified thresholds. A detailed comparison between the proposed ternary AND/NAND gate here and the ternary NAND gate reported by Wu et al. [4] is summarized in Table 3. It can be concluded that the proposed circuits dissipate less power and they are improved, when both the transistor counts and the operation rates are considered. Moreover, a significant feature of the proposed circuits is the use of a standard CMOS process without any modification of the thresholds, while in the circuits proposed in Ref. [4] two pairs of transistors with modified thresholds are needed.

Table 3 Comparisons between Fig. 3 (c) and ternary NAND gate<sup>[4]</sup>

| Subject for comparison             | Proposed AND/ NAND         | NAND <sup>[4]</sup> |

|------------------------------------|----------------------------|---------------------|

| Transistor count                   | 16 (includes AND and NAND) | 16                  |

| Number of V <sub>th</sub>          | 1                          | 2                   |

| Propagation delay/ ns (worst case) | 1.91/1.45<br>0.1pF load    | 2.36<br>0.1pF load  |

| Power consumption/µW               | 8.9                        | 12.1                |

## 5 Conclusion

Based on the theory of transmission switches, a new kind of static circuit scheme for ternary logic and a general method for synthesizing ternary logic gates have been developed. A way to generate complementary and dual circuits was presented. By using the complementarity and duality principles, the versatility of circuits is enhanced. In the proposed circuit scheme, literal functions are also realized by using traditional MOS transistors, while in Ref. [14], they are designed using neuron-MOS transistors. As compared to some reported static ternary circuits, this new scheme uses a standard CMOS process. Furthermore, it has a perfectly symmetrical structure and attains the full logic swing and the maximum possible noise margins. As compared to some dynamic ternary circuits, it does not suffer from known problems such as clock race

and charge redistribution. In binary DPL, for any input combination, there are always two current paths driving the output, while in TDPL, this characteristic does not always exist. The circuit verification of these proposed ternary logic circuits are verified by HSPICE simulation with a TSMC 0. 25µm CMOS device parameter. Furthermore, the proposed method can be extended to generate larger ternary logic functions and to synthesize quaternary logic circuits.

#### References

- [1] Heung A ,Mouftah H T. Depletion/enhancement CMOS for a low power family of three-valued logic circuits. IEEE J Solid-State Circuits, 1985, 20(2):609

- [2] Thoidis I, Soudris D, Fernandez J, et al. The circuit design of multiple-valued logic voltage-mode adders. Proc of ISCAS, 2001: IV-162

- [3] Babu H, Islam M, Ali A, et al. A technique for logic design of voltage-mode pass transistor based multi-valued multiple-output logic circuits. Proc of ISMVL, 2003:111

- [4] Wu X, Prosser F. CMOS ternary logic circuits. IEE Proceedings, 1990, 137-G(1):21

- [5] Philippe J M, Pillement S, Sentieys O. A low-power and highspeed quaternary interconnection link using efficient convert-

- ers. Proc of ISCAS, 2005:4689

- [6] Hurst S L. Multiple-valued logic-its status and its future. IEEE Trans Computers, 1984, C-33(12):1160

- [7] Wu C, Huang H. Design and application of pipelined dynamic CMOS ternary logic and simple ternary differential logic. IEEE J Solid-State Circuits, 1993, 28(8):895

- [8] Herrfeld A, Hentschke S. CMOS ternary dynamic differential logic. Electron Lett, 1994, 30(10):762

- [ 9 ] Toto F, Saletti R. CMOS dynamic ternary circuit with full logic swing and zero-static power consumption. Electron Lett, 1998, 34(11):1083

- [10] Suzuki M, Ohkubo N, Shinbo T, et al. A 1. 5-ns 32-b CMOS ALU in double pass-transistor logic. IEEE J Solid-State Circuits, 1993, 28(11):1145

- [11] Gu R X, Sharaf K M, Elmasry M I. High-performance digital VLSI circuit design. Boston: Kluwer Academic Publishers, 1996

- [12] Markovic D ,Nikolic B ,Oklobdzija V G. A general method in synthesis of pass-transistor circuits. Microelectronics Journal , 2000 ,31(11/12):991

- [13] Hang Guoqiang. Low power CMOS dynamic ternary circuit using double pass transistor logic. Journal of Zhejiang University (Eng Sci),2005,39(6):882(in Chinese)[杭国强. 低功耗 CMOS 三值动态双传输管逻辑电路. 浙江大学学报(工学版),2005,39(6):882]

- [14] Park S J, Yoon B H, Yoon K S, et al. Design of quaternary logic gate using double pass-transistor logic with neuron MOS down literal circuit. Proc of ISMVL, 2004:198

## 三值双传输管电路的通用综合方法\*

### 杭国强†

(浙江大学信息与电子工程学系,杭州 310027)

摘要:提出采用双传管逻辑设计三值电路的方法,对每个 MOS 管的逻辑功能均采用传输运算予以表示以实现有效综合.建立了三值双传输管电路的反演法则和对偶法则.新提出的三值双传输管逻辑电路具有完全基于标准 CMOS 工艺,无需对 MOS 管作任何阈值调整,结构简单、规则,输入信号负载对称性好,逻辑摆幅完整以及无直流功耗等特点.采用 TSMC 0. 25µm 工艺参数和最高电压为 3V 的 HSPICE 模拟结果验证了所提出综合方法的正确性

关键词: 开关电路理论; 多值逻辑; 逻辑综合; 双传输管逻辑

**EEACC:** 1100; 1265A; 2570D

中图分类号: TN432 文献标识码: A 文章编号: 0253-4177(2006)09-1566-06

<sup>\*</sup>浙江省自然科学基金资助项目(批准号: Y105124)

<sup>†</sup>通信作者. Email:hanggq@mail.hz.zj.cn