#### CHINESE JOURNAL OF SEMICONDUCTORS

# 新型槽栅 MOSFETs 的特性\*

曹艳荣"马晓华 郝 跃 于 磊

(西安电子科技大学微电子学院 宽禁带半导体材料与器件教育部重点实验室, 西安 710071)

摘要:采用 SIVALCO 软件对槽栅与平面器件进行了仿真对比分析,结果表明槽栅器件能够有效地抑制短沟道及热载流子效应,而拐角效应是槽栅器件优于平面器件特性更加稳定的原因.对自对准工艺下成功投片所得沟道长度为 140nm 的槽栅器件进行测量,结果有力地证明了槽栅器件较平面器件的优越性.

关键词: 自对准; 槽栅器件; 短沟道效应; 热载流子效应; 拐角效应

**EEACC:** 0170N; 2560R

中图分类号: TN386.1 文献标识码: A 文章编号: 0253-4177(2006)11-1994-06

### 1 引言

随着集成电路的迅速发展,MOSFET 的尺寸不断减小.在 MOS 器件结构尺寸等比缩小的同时,器件工作电压未能随之等比减小.进入深亚微米,传统的平面器件遇到了各种小尺寸效应和可靠性问题,一些影响器件特性的效应如 SCH(短沟效应)、DIBL(漏致势垒降低效应)、HCE(热载流子效应)、TDDB(氧化层的经时击穿)等更加明显.为此,人们提出了埋沟器件、外延硅器件、FIN-FET、Tri-FET<sup>[1,2]</sup>等多种器件结构和制备工艺.但这些器件结构和工艺都有各自的技术瓶颈限制其发展与应用,因此,槽栅器件作为一种极具应用前景的 MOS 器件被提了出来<sup>[3,4]</sup>.

国外槽栅器件研究近期主要集中在美国 IBM Appenzeller 等人基于 SOI V 型槽栅器件的研究<sup>[5]</sup>.他们采用了 KOH 自停止腐蚀 Si 技术,制作出了 36nm 的 nMOS 器件,但由于 KOH 自停止腐蚀 无法完成 pMOS 器件的工艺制作,同时 KOH 对工艺线的污染严重,所以,这种工艺的局限性较大.对此,我们提出了基于自对准的槽栅工艺并且流片成功,工艺过程中采用 RIE(反应离子刻蚀)干法刻蚀得到器件凹槽,并利用牺牲层改善刻蚀表面,保证栅氧质量,所得器件不仅提高了器件的性能,而且最大限度地采用了目前生产线上的成熟工艺.

本文对槽栅器件的制作流程进行了描述,采用新型软件 SIVALCO 对相同尺寸槽栅和平面器件进行了工艺与器件仿真,对槽栅器件特性作了进一

步的分析研究,并对实际投片得到的器件进行了测量.

## 2 槽栅工艺

制备槽栅器件的难点在于如何形成凹入的槽, 并形成质量良好的薄氧化层[6]. 最关键的是不应引 入太多附加工艺,尽量减少工艺复杂度和降低成本. 在仿真基础上,我们提出了槽栅自对准工艺.在此工 艺下制备槽栅器件,首先进行衬底预处理,包括腐 蚀、清洗、氧化.其次是阱注入,注入 B 形成 p 阱,注 入 P 形成 n 阱. 不同于常规平面器件的是,完成了 推阱工艺后,接下来是源漏的注入,注入 As 得到 p 阱 n 型源漏,注入 BF<sub>2</sub> 得到 n 阱 p 型源漏.此时源 漏区连接在一起.源漏区的最后形成是在刻槽工艺 完成之后,这步工艺也是整个工艺流程的关键.该步 骤掩模板可以采用常规工艺中的刻蚀多晶硅的掩模 板,光刻胶与其相反.刻蚀深度要大于源漏区深度, 以便形成负结.这一步确定了栅与源漏区域的位置, 是槽栅器件自对准工艺的一部分. 接下来是栅氧化 层的生长,这是槽栅工艺中的一个难点,同时也是影 响器件特性的重要因素.在槽栅工艺中,与平面器件 不同的是,影响栅氧化层质量的有两个方面:一方面 由于栅介质生长在刻蚀过的凹槽的两内侧和底部, 所以凹槽表面特性会影响栅介质的质量;另一方面, 凹槽的两个侧面是源漏区,其载流子浓度较高,所以 在热氧化过程中,很容易出现杂质向氧化层中扩散, 形成栅氧化层的穿通. 因此,在栅氧前,先在凹槽内 生长一层 SiO<sub>2</sub> 作为牺牲层,注入 As 或 B 进行阈值 调节.这一步可以防止阈值调节注入对凹槽表面的

<sup>\*</sup> 国家自然科学基金(批准号:60376024)和国家高技术研究发展计划(批准号:2003AA1Z1630)资助项目

<sup>†</sup>通信作者.Email:yrcao200@163.com

损伤,改善表面质量. 去掉牺牲层后,再采用低温氧化后  $N_2O_2$  退火,得到栅氧层,至此栅氧生长完毕. 之后淀积多晶硅,并对多晶硅进行  $N^+$  注入. 利用 CMP(化学机械抛光) 技术将氧化层上的多晶硅去掉,留下凹槽中的多晶硅作为栅,这一步完成了槽栅器件的自对准工艺. 最后形成接触电极. 图 1 为 SIVALCO 软件工艺仿真工具 Athena 对槽栅器件主要工艺的仿真流程图.

图 1 帽伽希什工乙烷程 Fig. 1 Process of groove-gate MOSFET

凹槽角度对器件特性的影响曾经是人们研究的重点<sup>[7]</sup>,但在实际的工艺过程中,该角度很难控制,对于非常短的沟道,其凹槽近似为 U 型或 V 型,沟道的有效长度近似为凹槽底部长度加上二倍的负结深度.

# 3 仿真分析

为了更好地分析槽栅器件的性能特征,用 SIVALCO软件通过工艺仿真生成一系列结构参数 相同的槽栅和平面器件,继而对两者电学特性进行 仿真比较分析.

仿真过程中采用了能量平衡传输模型. 传统的

漂移-扩散模型不能完全适合超深亚微米器件仿真的数值模型,它忽略了非局部的传输效应如速度过冲、与载流子温度相关的扩散及碰撞电离速率与载流子能量分布的关系等.能量平衡传输模型将这些因素都考虑在内,除了基本的载流子连续性方程、Poisson方程外,还包括了能流密度方程及能量平衡方程:

$$S_{n} = -K_{n} \nabla T_{n} - \left(\frac{k \delta_{n}}{q}\right) J_{n} T_{n}$$

(1)

$$\operatorname{div} \mathbf{S}_{n} = \frac{1}{q} \mathbf{J}_{n} \mathbf{E} - W_{n} \frac{3k}{2} \times \frac{\partial}{\partial t} (\lambda_{n}^{*} n T_{n}) \quad (2)$$

可使 SIVALCO 精确仿真.

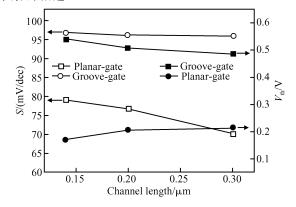

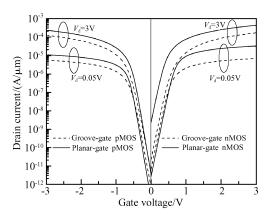

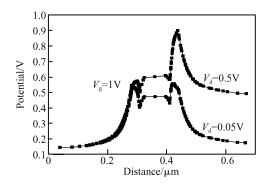

图 2 为槽栅与平面器件阈值电压与亚域摆幅随 沟道长度变化的曲线,器件沟道长度分别为 0.14, 0.2 和 0.3μm. 从图中可以很明显地看出,平面器件 的阈值电压随沟道长度的减小迅速降低,槽栅器件 的阈值电压随器件沟道长度的减小不但没有降低, 相反还略有提高,完全抑制了小尺寸所带来的阈值 电压的漂移. 槽栅器件和平面器件的亚阈摆幅都随 沟道长度的减小而增大,因而亚阈特性随沟道长度 的减小退化.槽栅器件亚阈摆幅比平面器件要高,但 随着沟道长度的减小,其亚阈特性的退化要比平面 器件弱得多. 平面器件由沟道长度为 0.3 μm 时的 70. 2mV/dec 到 0. 14μm 时的 79. 1mV/dec,退化了 12.7%; 而槽栅器件相应的由 96mV/dec 到 96.8mV/dec,退化了 0.83%,沟道减小所导致的亚 阈特性退化几乎没有给槽栅器件带来影响.图3为 不同漏压下槽栅和平面器件的转移特性. 从图中可 以看出,槽栅器件的开启电压随漏压的增大变化较 小,而平面器件的开启电压则变化明显,随漏压的增 大迅速减小. 出现这样的结果, 与它们内部的电场分 布紧密相连.

图 2 不同沟道长度槽栅与平面器件阈值电压与亚阈摆幅 Fig. 2  $V_{\rm th}$  and S of groove and planar-gate MOSFETs with different channel lengths

平面器件阈值电压的漂移主要是由 DIBL(漏致势垒降低)效应所导致. 当  $V_{ds}=0$  时,在短沟情况

图 3 槽栅与平面器件转移特性

Fig. 3  $I_{\rm d}$ - $V_{\rm g}$  characteristics of groove and planar-gate MOS-FETs

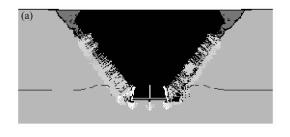

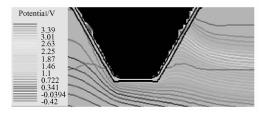

下,源漏扩散区相互靠近,导致势垒单一峰值和势垒下降;当 | V<sub>d</sub> | > 0 时,漏区发出的场强线一部分穿透到源区,漏区增加的电荷不仅对靠近漏区的沟道及耗尽区有影响,而且对整个栅极下面半导体内的表面电荷都有影响,这使势垒变得更低.而槽栅器件之所以能够抑制阈值漂移,是因为其器件结构的变化引起了沟道内部电场分布的变化.槽栅器件下沉的栅穿透源漏区,在源漏各有一物理拐角.根据电场理论,拐角凹面处的电力线呈收敛状,电力线的密度大,拐角处电场变化大于其他位置,从而形成槽栅器件独特的两拐角势垒,如图 4 所示.与平面器件中漏极电压强烈扭曲沟道内电场从而减弱甚至消除沟道区内唯一势垒相对,槽栅器件中近漏区拐角势垒即使受漏极偏压影响有所减弱,近源端拐角势垒仍然

图 4 槽栅器件拐角电场分布及拐角势垒

Fig. 4 Corner field of groove-gate MOSFET and corner barrier

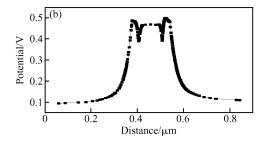

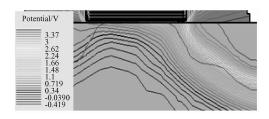

存在,从而抑制了 DIBL 效应.图 5 为高漏压下槽栅与平面器件沟道电势分布图,图 6 为不同漏压下槽栅器件的拐角势垒.从理论上讲,凹槽拐角越小,电力线越密集,拐角势垒越高,对 DIBL 效应的抑制能力就越强<sup>[7]</sup>.但也正是拐角势垒的存在,使得槽栅器件的栅对沟道控制能力变弱,因此,槽栅器件亚阈摆幅较平面器件大,亚阈特性较差.在实际工艺中,凹槽拐角很难控制,所以若想通过控制凹槽拐角来得到较为合适的拐角势垒还不太现实,希望在工艺条件进一步提高的将来能够实现这一目标.

图 5 槽栅与平面器件沟道电势分布

Fig. 5 Distributing of channel barrier of groove and planar-gate MOSFETs

图 6 槽栅器件不同漏压下的拐角势垒

Fig. 6 Corner barrier of groove-gate MOSFET with different  $V_{\rm d}$

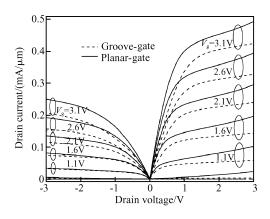

图 7 给出沟道长度为  $0.14\mu m$  时,槽栅器件和平面器件的输出特性曲线.与平面器件相比较,槽栅器件的漏极驱动能力相对较弱,但输出饱和特性明显优于平面器件.平面器件在短沟道情况下,漏端电压达到饱和后,随  $V_{ds}$ 的增大,有效沟道长度缩短,而饱和漏电流计算公式为下式:

$$I_{dsat} = \mu_n C_{ox} W(V_{gs} - V_{th})^2 / 2L$$

(3)

因此  $I_{dsat}$  随  $V_{ds}$  的增大而增大,另外在衬底低掺

图 7 槽栅和平面器件的输出特性

Fig. 7  $I_d$ - $V_d$  characteristics of groove and planargate MOSFETs

杂短沟道情况下,器件漏区和沟道之间将出现明显 的静电耦合,随  $V_{\alpha}$ 的增加反型层内电子数量增加, 导致电阻减小,电流随之增大,从而出现短沟道情况 下漏极输出曲线饱和电流不饱和的现象.而由于槽 栅器件拐角势垒的存在,抑制了漏端高电场向源端 的扩展,保证了有效沟道长度基本不变,减弱了漏区 和沟道之间的静电耦合,从而使输出曲线平坦,特性 良好.另外,槽栅器件的拐角势垒在改进输出曲线饱 和特性的同时,它也有着负面的影响.拐角势垒的存 在,使载流子从源端到达漏端必须翻越势垒,减弱了 载流子的定向运动,从而使输出电流较平面器件的 要小.因此可以得出,槽栅器件较平面器件有着较好 的饱和特性和较低的漏极驱动能力.对槽栅器件饱 和电流值较小这一问题,可以从其他方面着手改进. 由于槽栅器件的拐角势垒抑制了短沟道情况下阈值 电压的下降,所以不必像平面器件那样通过对衬底 沟道进行重掺杂来调整阈值电压,因此槽栅器件可 以通过减少衬底和沟道掺杂浓度来提高漏电流.

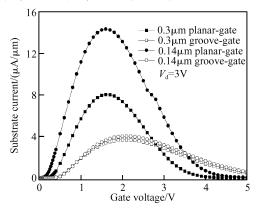

图 8 为沟道长度分别为 0. 14 和 0. 3µm 时,槽栅与平面器件的衬底电流.从图中可以很明显地看出,槽栅器件的衬底电流远远低于平面器件.在沟道长度为 0. 3µm 时,槽栅器件的衬底电流为平面器件的 45. 87%;当沟道长度缩小到 0. 14µm 时,槽栅器件的衬底电流为平面器件的 28. 03%,可见在相同条件下,槽栅器件抗热载流子效应要优于平面器件.随着沟道长度的缩短,两种器件热载流子效应均增大,但增大程度不同.平面器件沟道长度由 0. 3 减小到 0. 14µm,最大衬底电流增大了 78. 37%,而槽栅器件相应增大仅为 8. 99%,因此,与平面器件相比,在短沟道情况下,槽栅器件能够更好地抑制热载流子效应.这也要归因于槽栅器件拐角势垒的存在.载流子从源端到达漏端,既需改变方向,又要跨越势垒<sup>[8]</sup>,且拐角势垒抑制了漏端高电场的扩展,使沟道

电场较平面器件低,从而使得载流子碰撞离化率减小,衬底电流减小.另外,从图中还可以看出,槽栅器件衬底电流达到峰值时的栅源电压要高于平面器件.这是因为在短沟道情况下,在相同的电压作用下,平面器件内部电场高于槽栅器件,热电子所得到的加速能量更高,导致在较低栅压下衬底电流已达到最大值,这也是平面器件短沟效应的一个反映.

图 8 不同沟道长度槽栅与平面器件衬底电流 Fig. 8  $I_{\text{sub}}$  of groove and planar-gate MOSFETs with different channel lengths

从仿真结果可以看出,槽栅器件抑制了短沟道情况下阈值电压的减小,亚阈摆幅增大但随沟道的减小退化较小,输出电流较小但饱和特性较好,大大改善了热载流子效应.

# 4 投片测量结果

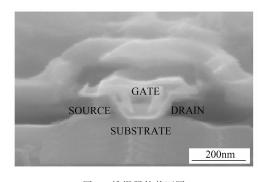

在仿真基础上,基于自对准工艺,我们在中国科学院微电子研究所对槽栅器件进行投片并获得成功,图 9 为槽栅器件的截面图. 利用测试仪器 HP4156B,对实际投片得到的沟道长度为  $0.14\mu m$  (凹槽底部约为 100nm,负结深度约为 20nm)的槽栅器件进行测试,得到了一系列的结果.表 1 列出了槽栅器件及相同结构尺寸平面器件的特征参数.

图 9 槽栅器件截面图

Fig. 9 Cross section of groove-gate MOSFET

表 1 槽栅与平面器件特征参数比较

Table 1 Comparison of characteristic parameters of groove and planar-gate MOSFETs

| 参数                                            | 槽栅器件                    |                            | 平面器件                       |                         |

|-----------------------------------------------|-------------------------|----------------------------|----------------------------|-------------------------|

|                                               | nMOS                    | pMOS                       | nMOS                       | pMOS                    |

| $V_{\mathrm{th}}/\mathrm{V}$                  | 1. 24                   | 1. 45                      | 0. 465                     | 0. 618                  |

| $I_{\rm dsat}/({\rm A}/\mu{\rm m})$           | 2. $337 \times 10^{-4}$ | 8. $430 \times 10^{-5}$    | 5. 180 × 10 <sup>- 4</sup> | 1. 565×10 <sup>-4</sup> |

| $\overline{\text{DIBL}/(\text{mV}/\text{V})}$ | 60                      | 53                         | 280                        | 208                     |

| S/(mV/dec)                                    | 88                      | 70                         | 80                         | 75                      |

| $I_{\text{subpeak}}/(A/\mu m)$                | 1. $732 \times 10^{-6}$ | 5. 621 × 10 <sup>- 7</sup> | 8. 632 × 10 <sup>- 5</sup> | 1. 552×10 <sup>-5</sup> |

| $G_{ m mmax}/{ m S}$                          | 2.840×10 <sup>-5</sup>  | 8. 085 × 10 <sup>- 6</sup> | 6. 050 × 10 <sup>- 5</sup> | 1. 522×10 <sup>-5</sup> |

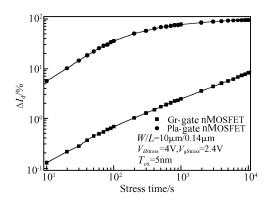

从表中可以看出,投片所得槽栅器件阈值电压比较高,相比较而言,nMOS 器件的开启电压要比pMOS的小,输出特性较好,饱和电流约为pMOS的3倍,这与仿真结果完全类似.对阈值电压的调整,可以通过减小栅氧厚度,调节阈值注入浓度等方法得到较小的值.槽栅器件很好地抑制了DIBL效应,衬底电流较平面器件小了将近两个数量级.通过HCI(热载流子注入)应力测试,我们可以很清楚地看到,槽栅较平面器件对热载流子效应的抑制作用,如图 10 所示.

图 10 槽栅与平面器件 HCI 应力测试结果 Fig. 10 Results of groove and planar gate MOSFETs HCI stress

实际测量结果和仿真结果基本相同,所得各种特性趋势一致,但在某些细节上还有一定的差异.改进仿真模型优化工艺条件,可以使仿真结果更准确,从而实现对实际器件更好的指导作用.另外,毕竟是首次投片,槽栅工艺尚未完全成熟,尤其刻槽工艺引入了大量的表面损伤,虽然经过牺牲层技术处理,但对器件特性仍有一定的影响.在后面的投片中,我们

将侧重于器件电学参数的调整,同时进一步改进刻槽工艺以得到更好性能的器件.槽栅器件特性及理论分析都有了一定的发展,但还有很多现象不为我们所理解,有待于更深一步的探索和研究.

### 5 结论

通过 SIVALCO 软件仿真,将槽栅与平面器件电学特性及内部电特性作了比较分析后发现,在短沟道情况下,由于拐角势垒的存在,与平面器件相比,槽栅器件阈值电压增大且可控,亚阈摆幅较大但随沟道减小退化很小,输出电流较小但饱和特性得到改善,抗热载流子性能大大增强.基于仿真基础,提出自对准槽栅工艺并成功投片.对所得器件的测量表明,槽栅器件有效地抑制了短沟道与热载流子效应,使器件特性更加稳定,在未来 VLSI 的发展与应用具有一定的优势.

### 参考文献

- [1] Fried D M, Duster J S, Kornegay K T. Improved independent gate n-type Fin FET fabrication and characterization. IEEE Electron Device Lett, 2003, 24:592

- [2] Doyle B. S. Datta S. Doczy M. et al. High performance fully-depleted tri-gate CMOS transistors. IEEE Electron Device Lett, 2003, 24:263

- [3] Lyu J, Park B G, Chun K, et al. A novel 0.1µm MOSFET structure with inverted sidewall and recessed channel. IEEE Electron Device Lett.1996.17(4):157

- [4] Bricout P H, Dubois E. Short-channel effect immunity and current capability of sub 0.1-micron MOSFETs using a recessed channel. IEEE Trans Electron Devices, 1996, 43(8): 1251

- [5] Appenzeller J, Martel R, Avouris P, et al. Sub-40 nm SOI V-groove n-MOSFETs. IEEE Electron Device Lett, 2002, 23: 101

- [6] Ma Xiaohua, Hao Yue, Sun Baogang, et al. Fabrication and characterization of groove-gate MOSFETs based on a self-aligned CMOS process. Chinese Physics, 2006, 15(1):195

- [7] Ren Hongxia, Hao Yue. Influence of variation of negative junction depth on characteristics of deep-sub-micron pMOS-FET. Chinese Journal of Semiconductors, 2001, 22(5): 622 (in Chinese) [任红霞,郝跃. 凹槽深度与槽栅 pMOSFET 特性.半导体学报,2001,22(5):622]

- [8] Ren Hongxia, Hao Yue, Xu Donggang. Study on hot-carrier-effect for grooved-gate n-channel metal-oxide-semiconductor field-effect-transistor. Acta Physica Sinica, 2000, 49(7):1241 (in Chinese) [任红霞,郝跃,许冬岗.n 型槽栅金属-氧化物-半导体场效应晶体管抗热载流子效应的研究.物理学报, 2000, 49(7):1241]

### Characteristics of Groove-Gate MOSFETs\*

Cao Yanrong<sup>†</sup>, Ma Xiaohua, Hao Yue, and Yu Lei

(Key Laboratory of the Ministry of Education for Wide Band-Gap Semiconductor Materials and Devices, School of Microelectronics, Xidian University, Xi'an 710071, China)

Abstract: The groove- and planar-gate MOSFETs are compared and analyzed through simulation with the software SIVAL-CO, and the results show that the groove-gate MOSFETs can suppress short channel and hot carries effects. From the analysis of the field, we find that due to the corner effect, the performance of groove-gate MOSFETs is better than that of the planar. The groove-gate MOSFETs with 140nm channel length fabricated with a self-aligned process are tested, and the results effectively show the superiority of the groove-gate MOSFETs over the planar.

Key words: self-aligned; groove-gate MOSFETs; short channel effects; hot carries effects; corner effect

EEACC: 0170N; 2560R

**Article ID:** 0253-4177(2006)11-1994-06

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (No. 60376024) and the National High Technology Research and Development Program of China (No. 2003AA1Z1630)

<sup>†</sup> Corresponding author. Email: yrcao200@163.com