## Off-State Breakdown Characteristics of PDSOI nMOSFETs

Bi Jinshun<sup>†</sup> and Hai Chaohe

(Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China)

**Abstract:** Partially-depleted silicon-on-insulator(PDSOI) floating-body(FB) nMOSFETs and H-gate type body-contacted(BC) nMOSFETs are fabricated with different back channel implantation dosages. The off-state breakdown characteristics of these devices are presented. The off-state breakdown voltages of the FB nMOSFETs increase from 5. 2 to 6. 7V, and those of the H-gate type BC nMOSFETs decrease from 11. 9 to 9V as the back channel implantation dosages increase from  $1.0 \times 10^{13}$  to  $1.3 \times 10^{13}$  cm<sup>-2</sup>. By measuring the parasitic bipolar transistor static gain and the breakdown characteristics of the pn junction between the drain and the body, the differences between the breakdown mechanisms of the FB and H-gate type BC nMOSFETs are analyzed and explained qualitatively.

Key words: PDSOI; breakdown; back channel implantation

**EEACC:** 2560

#### 1 Introduction

SOI technology has been regarded as one of the most promising CMOS technologies because of its excellent subthreshold slope[1], high speed operation<sup>[2]</sup>, and improved drivability<sup>[3]</sup>. In addition, SOI circuits have an inherent resistance to harsh environmental conditions such as radiation<sup>[4]</sup> and high temperature<sup>[5]</sup>. PDSOI devices, due to their ease of manufacture by decoupling the threshold voltage from the SOI film thickness, have been a favored choice [6]. PDSOI floating body devices are preferred for digital circuits for speed considerations, but in analog circuits and I/Os, in which history effects are not tolerable, body contacts must be added to the devices in order to fix the body potential to a certain value<sup>[7]</sup>. The H-gate is one popular type of body contact scheme.

Off-state breakdown voltage is among the key parameters of PDSOI FB and BC devices. In PDSOI device fabrication, a two-step channel implantation is conventionally implemented to avoid the leakage of the back channel and to adjust the threshold voltage of the front channel. In this paper, we investigate the off-state breakdown characteristics of PDSOI FB and H-gate type BC nMOSFETs with respect to their back channel im-

plantation dosages.

### 2 Device fabrication

The 0.8 µm gate length FB and H-gate type BC nMOSFETs were fabricated on 150mm separation by implanted oxygen (SIMOX) wafers from Simgui Corp under the same process, with the following material parameters: p (100),  $10 \sim 20$  $\Omega \cdot cm$ , 500nm silicon film, and a 375nm BOX (buried oxide) layer. First, the thickness of the silicon film was reduced to 400nm by growing and stripping a sacrificial oxide layer. Then two-step local oxidation of silicon (LOCOS) isolation technology was used to isolate the devices after field implantation of boron ions. Back channel implantation of B<sup>+</sup> ions and front channel implantation of BF<sub>2</sub><sup>+</sup> ions were performed to avoid the leakage of the back channel and to adjust the threshold voltage of the front channel. The dosages of back channel implantation were  $1.0 \times 10^{13}$ ,  $1.1 \times 10^{13}$ , and  $1.3 \times 10^{13} \, \text{cm}^{-2}$ , respectively, while the dosages of front channel implantation were the same for all the devices in this study. After an 18nm gate oxide was thermally grown, 420nm n<sup>+</sup> heavily doped polysilicon was deposited. Then  $0.8\mu m$ length gate lines were patterned and etched, followed by lightly doped drain(LDD)implantation. After the gate spacer formation, arsenic and phos-

<sup>†</sup> Corresponding author. Email: bravehawk@126.com

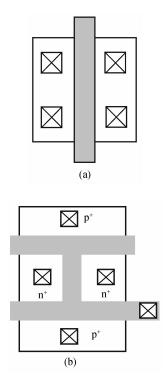

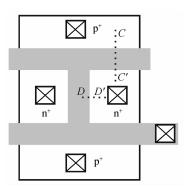

phorus ions were implanted to form the n<sup>+</sup> source/drain. In order to activate the impurities implanted in the silicon film, rapid thermal processing (RTP) at 1000°C was performed. After the salicidation, the devices were metallized using a typical backend flow. Figure 1 shows the layouts of the FB and H-gate type BC nMOSFETs in this study.

Fig. 1 Layouts of FB (a) and H-gate type BC (b) nMOSFETs

### 3 Results and discussion

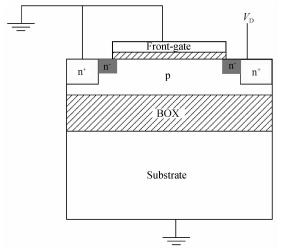

After the formation of the  $8\mu\text{m}/0.8\mu\text{m}$  FB and H-gate type BC nMOSFETs, we measured the off-state breakdown curves with a Keithley 4200SCS semiconductor characteristics system. In this test, the source, the substrate, and the gate terminals were all grounded, as shown in Fig. 2. A drain current of  $1\times10^{-5}\text{A}$  is defined as the breakdown point.

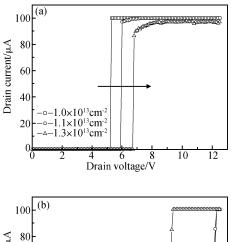

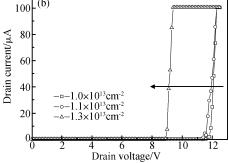

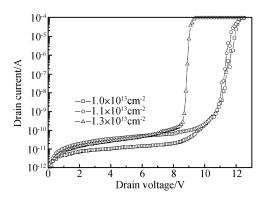

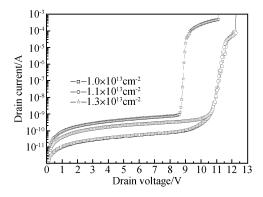

Figure 3 shows the off-state breakdown characteristics of the FB and H-gate type BC nMOS-FETs with back-channel implantation dosages of  $1.0\times10^{13}$ ,  $1.1\times10^{13}$ , and  $1.3\times10^{13}$  cm<sup>-2</sup>. Table 1 gives the breakdown points of these devices. The breakdown voltage of the FB nMOSFETs is much lower than that of the H-gate type BC nMOSFETs. This is because there is a parasitic bipolar

Fig. 2 Cross sectional view of SOI nMOSFETs

transistor (PBT) with floating base in the FB nMOSFETs. From bipolar transistor theory  $^{[8]}$ , the collector (drain) breakdown voltage with open base  $BV_{\text{CE0}}$  is smaller than when the base is grounded,  $BV_{\text{CB0}}$ . Both breakdown voltages are related as

$$BV_{CE0} = \frac{BV_{CB0}}{\sqrt[n]{\beta}}$$

(1)

Table 1 Breakdown points of FB and H-gate type BC nMOSFETs

| Back channel implant dosage            | FB nMOSFETs | H-gate type BC nMOSFETs |

|----------------------------------------|-------------|-------------------------|

| 1. $0 \times 10^{13}$ cm $^{-2}$       | 5. 2V       | 11. 9V                  |

| 1. 1×10 <sup>13</sup> cm <sup>-2</sup> | 5. 6V       | 11. 5V                  |

| 1. 3×10 <sup>13</sup> cm <sup>-2</sup> | 6. 7V       | 9V                      |

where  $\beta$  is the gain of the bipolar device, and n typically ranges from 3 to 6. The body contacts in H-gate type BC nMOSFETs are always grounded. They can elicit redundant holes from the body region and thus decrease the body potential, drain current, and impact ionization rate. Thus the parasitic bipolar transistor is inhibited from functioning.

From Fig. 3 and Table 1, we can clearly see that the breakdown voltages of the FB and H-gate type BC nMOSFETs show different trends as the back channel implantation dosages increase from  $1.0\times10^{13}$  to  $1.3\times10^{13}\,\mathrm{cm^{-2}}$ . The off-state breakdown voltages of the FB nMOSFETs increase, while those of the H-gate type BC nMOSFETs decrease with the increase in back channel implantation. This is due to the different breakdown mechanisms in the two devices.

Fig. 3 Off-state breakdown characteristics of FB (a) and H-gate type BC (b) nMOSFETs

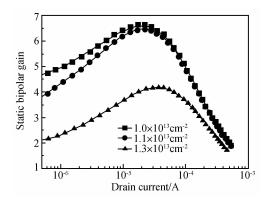

Figure 4 illustrates the relationship between the parasitic bipolar transistor static gain and the drain current in SOI nMOSFETs at different back channel implantation dosages. It is obvious that bipolar static gain decreases with increased back channel implantation dosage. In FBSOI nMOSFETs, the parasitic bipolar transistor with floating base is the main breakdown mechanism. According to Eq. (1), increasing the back channel implantation dosage means doping the base (body) more heavily, which decreases the static bipolar

Fig. 4 Parasitic bipolar transistor static gain in SOI nMOSFETs with respect to drain current at different back channel implantation dosages

gain  $\beta$ . Thus the off-state breakdown voltages of the FB nMOSFETs are improved with increased back channel implantation dosage.

Generally, the breakdown mechanism of bulk nMOSFETs with channel length less than  $2\mu m$  is source/drain junction punch-through [9,10]. However, the devices in this study are different. First, the breakdown characteristics of the H-gate type BC nMOSFETs with gate lengths of 0.8 and  $2\mu m$  fabricated in this study have no obvious difference. Second, the body region is more heavily doped with increased back channel implantation dosages, so it is harder for source/drain junction punch-through to occur, and the punch-through voltage is increased. The phenomena in this study are clearly different.

Converting the y-axis in Fig. 3 from linear to logarithmic scale as shown in Fig. 5 only shows the breakdown characteristics of the H-gate type BC nMOSFETs. In Fig. 6, the breakdown curves of the body and drain junction are shown. The breakdown voltages of the pn junction between

Fig. 5 Breakdown characteristics of H-gate type BC nMOSFETs in log-scale

Fig. 6 Breakdown curves of the body and drain junction

body and drain are 11. 8,11. 5, and 8. 85V, respectively, with the back channel implantation dosages from  $1.0\times10^{13}$  to  $1.3\times10^{13}$  cm $^{-2}$ . Compared with Table 1, the breakdown voltages of the body/drain junction are almost the same as those of the H-gate type BC nMOSFETs. This implies that the breakdown of the body/drain junction is the dominant breakdown mechanism in these devices.

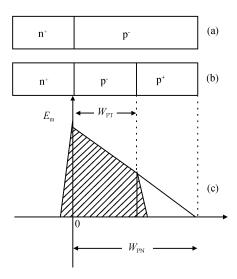

As shown in Fig. 7, there are two types of body/drain junctions. One is a reverse-biased punch-through junction along line CC´ and the other is an abrupt junction along line DD´. The relationship between punch-through junction and abrupt junction, assuming the same doping of the substrate, is given in Fig. 8. From Fig. 8, we neglect the contributions of the  $p^+$  region (body contact region) and the  $n^+$  region (drain region) to breakdown voltage and assume the ratio of  $BV_{PT}$  and  $BV_{PN}$  to be  $\chi$ . According to Ref. [11], we can then get the following equations:

$$E_{\max(PT)} = E_{\max(PN)} \tag{2}$$

$$\frac{BV_{PT}}{BV_{PN}} = \chi, \quad 0 < \chi \leqslant 1$$

(3)

$$\frac{W_{\rm PT}}{W_{\rm PN}} = \eta, \quad 0 < \eta \leqslant 1 \tag{4}$$

$$\frac{\mathrm{BV}_{\mathrm{PT}}}{\mathrm{BV}_{\mathrm{PN}}} = 2\eta - \eta^2 \tag{5}$$

Fig. 7 A reverse-biased punch-through junction along line CC  $\acute{}$  and an abrupt junction along line DD  $\acute{}$

Here,  $E_{\rm max(PN)}$  is the maximum electrical field of the abrupt junction at breakdown, BV<sub>PN</sub> is the breakdown voltage of the abrupt junction,  $W_{\rm PN}$  is the depletion region width of the abrupt junction at breakdown,  $E_{\rm max(PT)}$  is the maximum electrical field of the punch-through junction at punch-through breakdown, BV<sub>PT</sub> is the punch-through breakdown voltage of the punch-through junction, and  $W_{\rm PT}$  is the width of the body region.

Fig. 8 (a)  $n^+/p^-$  abrupt junction assuming the same doping of the substrate along line DD'; (b)  $n^+/p^-/p^+$  punch-through junction along line CC'; (c) Relationship of electrical field and breakdown voltage between abrupt junction and punch-through junction. The shaded region represents the electrical field and breakdown voltage of the  $n^+/p^-/p^+$  punch-through junction.

According to Ref.[11],

$$BV_{PN} = 5.34 \times 10^{13} N^{-\frac{3}{4}}$$

(6)

Combining Eqs. (5) and (6), we can derive BV<sub>PT</sub> = 5.  $34 \times 10^{13} (2\eta - \eta^2) N^{-\frac{3}{4}}$ , where N is the doping concentration of the body region.

From the above discussion, the punch-through breakdown voltage of the drain/body junction along line CC' is lower than the breakdown voltage of the drain/body abrupt junction along line DD'. The punch-through breakdown voltage of the drain/body junction along line CC' is inversely proportional to the doping concentration of the body region, so  $BV_{PT}$  decreases with increasing back channel implantation dosage, which matches the behavior of the H-gate type BC nMOSFETs in this study. This means that the punch-through breakdown of the body/drain junction is the dominant breakdown mechanism in these devices.

#### 4 Conclusion

PDSOI  $8\mu$ m/0.  $8\mu$ m FB and H-gate type BC nMOSFETs were fabricated with back channel dosages of  $1.0\times10^{13}$ ,  $1.1\times10^{13}$ , and  $1.3\times10^{13}$  cm<sup>-2</sup>. The off-state breakdown voltages of the FB nMOSFETs increase, while those of H-gate type

BC nMOSFETs decrease, with increasing back channel implantation dosage. By testing parasitic the bipolar transistor static gain and pn junction breakdown characteristics of the drain and the body, the breakdown mechanisms of these devices are analyzed.

#### References

- [1] Colinge J P. Subthreshold slope of thin-film SOI MOSFET's.

IEEE Electron Device Lett. 1986:244

- [2] Sturm J C. Ultra-high CMOS circuits in thin SIMOX films. IEDM Tech Dig, 1987;829

- [3] Lemnios Z J. Manufacturing technology challenges for low power electronics. Dig Tech Papers of Symp VLSI Technology, 1995:5

- [4] Zhao Hongchen. Studies on radiation hardened SOI CMOS technology. PhD Thesis, Graduate School of the Chinese Academy of Sciences, 2005:2(in Chinese) [赵洪辰. SOI CMOS

- 抗辐照技术研究.中国科学院研究生院博士学位论文,2005:2]

- [5] Groeseneken G, Colinge J P, Maes H E, et al. Temperature dependence of threshold voltage in thin-film SOI MOSFET's. IEEE Electron Device Lett, 1990, 11:329

- [6] Shahidi G G, Ning T H, Chappell T I, et al. SOI for a 1-volt CMOS technology and application to a 512Kb SRAM with 3.5ns access time. IEDM Tech Dig, 1993;813

- [7] Bernstein K, Rohrer N J. SOI circuit design concepts. Kluwer Academic Publishers, 2000;76

- [8] Colinge J P. Silicon-on-insulator technology: materials to VLSI.2nd ed. Kluwer Academic Publishers, 1997:165

- [ 9 ] Sze S M. Physics of semiconductor devices. 2nd ed. John Wiley & Sons, 1981;100

- [10] Cao Peidong. Basis of microelectronics technology-principle of bipolar, field effect transistors. Beijing, Publishing House of Electronics Industry, 2001;245(in Chinese)[曹培栋. 微电子技术基础:双级、场效应晶体管原理. 北京:电子工业出版社, 2001;245]

- [11] He Jin, Wang Xin, Chen Xingbi. Optimum design of epitaxial layers with uniform doping for VDMOS transistor. Chinese Journal of Semiconductors 1999 20:977

# PDSOI nMOSFETs 关态击穿特性

毕津顺\*海潮和

(中国科学院微电子研究所,北京 100029)

摘要:分别采用不同的背栅沟道注入剂量制成了部分耗尽绝缘体上硅浮体和 H 型栅体接触 n 型沟道器件. 对这些器件的关态击穿特性进行了研究. 当背栅沟道注入剂量从  $1.0\times10^{13}$  增加到  $1.3\times10^{13}$  cm  $^{-2}$  ,浮体 n 型沟道器件关态击穿电压由 5.2 升高到 6.7V,而 H 型栅体接触 n 型沟道器件关态击穿电压从 11.9 降低到 9V. 通过测量寄生双极晶体管静态增益和漏体 pn 结击穿电压,对部分耗尽绝缘体上硅浮体和 H 型栅体接触 n 型沟道器件的击穿特性进行了定性解释和分析.

关键词:部分耗尽绝缘体上硅;击穿;背栅沟道注入

**EEACC**: 2560

中图分类号: TN386 文献标识码: A 文章编号: 0253-4177(2007)01-0014-05