# **Dual Material Gate SOI MOSFET with a Single Halo**\*

Li Zunchao<sup>1,†</sup>, Jiang Yaolin<sup>2</sup>, and Wu Jianmin<sup>2</sup>

(1 School of Electronics and Information Engineering, Xi'an Jiaotong University, Xi'an 710049, China)

(2 School of Science, Xi'an Jiaotong University, Xi'an 710049, China)

Abstract: In order to suppress drain-induced barrier lowering in dual material gate SOI MOSFETs, halo doping is used in the channel near the source. Two-dimensional analytical models of surface potential and threshold voltage for the novel SOI MOSFET are developed based on the explicit solution of the two-dimensional Poisson's equation. Its characteristic improvement is investigated. It is concluded that the novel structure exhibits better suppression of drain-induced barrier lowering and higher carrier transport efficiency than conventional dual material gate SOI MOSFETs. Its drain-induced barrier lowering decreases with increasing halo doping concentration but does not change monotonically with halo length. The analytical models agree well with the two-dimensional device simulator MEDICI.

Key words: dual material gate; SOI; threshold voltage; analytical model

EEACC: 2560R; 2560B

### 1 Introduction

Dual material gate (DMG) SOI MOS-FETs<sup>[1~3]</sup> seem to be a very promising option for ultimate scaling of CMOS technology due to their excellent short channel effect (SCE) and hot carrier effect (HCE) suppression and high carrier transport efficiency[4,5]. However, DMG SOI MOSFETs show considerable drain-induced barrier lowering (DIBL) in the sub-100nm regime. Locally raising the channel doping next to the drain or drain/source can improve MOSFET's performance [6~8]. In the past few years, the local high doping concentration in the channel near source/ drain junctions has been implemented via lateral channel engineering, e.g., halo or pocket implantation[9~11]. Single-halo MOSFET structures have been introduced for bulk[12] as well as SOI MOS-FETs[13] to adjust threshold voltage. Halo implantation devices show excellent output characteristics with low DIBL, higher driving capacity and low leakage currents compared to conventional MOSFETs. However, such an attempt has not been reported for DMG SOI MOSFETs. In this paper, for the first time the structure of a DMG SOI MOSFET with a single halo is investigated. Two-dimensional analytical models of potential and threshold voltage for the fully depleted SOI MOSFET are developed based on the explicit solution of the two-dimensional Poisson's equation. The characteristics of the novel SOI MOSFET are compared with the conventional DMG SOI MOSFET and the influence of the halo structures is studied. The models are verified with the two-dimensional device simulator MEDICI.

### 2 Model formulation

### 2.1 Analytical potential

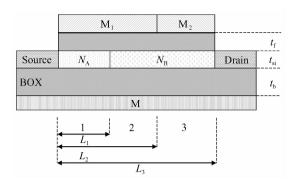

The schematic structure of the DMG SOI MOSFET with a single halo (DMGH) is shown in Fig. 1. The doping concentration  $N_{\rm A}$  near the source region is higher than  $N_{\rm B}$  in the rest of the channel. Considering the gate and doping profile, the channel can be divided into three zones.

Neglecting the effect of the fixed oxide charges on the electrostatics of the channel, the Poisson's equation of the potential distribution in the three silicon film zones before the onset of strong inversion can be written as  $^{[14\sim16]}$

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (No. 60472003) and the State Key Development Program for Basic Research of China (No. 2005CB321701)

<sup>†</sup> Corresponding author. Email: zcli@mail. xjtu. edu. cn

Fig. 1 Schematic structure of DMG with a single halo

$$\frac{\partial^{2} \varphi_{j}(x,y)}{\partial x^{2}} + \frac{\partial^{2} \varphi_{j}(x,y)}{\partial y^{2}} = \frac{qN_{j}}{\varepsilon_{si}},$$

$$L_{j-1} \leqslant x \leqslant L_{j}, 0 \leqslant y \leqslant t_{si}, j = 1,2,3 \quad (1)$$

where  $\varepsilon_{\rm si}$  is the dielectric constant of silicon film,  $N_1=N_{\rm A}$ ,  $N_2=N_{\rm B}$ , and  $N_3=N_{\rm B}$ .

The potential profile in the vertical direction, i.e., the y-dependence of  $\varphi_j(x,y)$  (j=1,2,3), can be approximated by a simple parabolic function for a fully depleted SOI MOSFET as

$$\varphi_j(x,y) = \varphi_{sj}(x) + c_{j1}(x)y + c_{j2}(x)y^2,$$

$$L_{j-1} \leqslant x \leqslant L_j, 0 \leqslant y \leqslant t_{si}, j = 1,2,3 \quad (2)$$

where  $\varphi_{sj}(x)$   $(j = 1,2,3)$  is the front surface potential in zone  $j$  and  $L_0 = 0$ .

According to Eq. (2) and the continuity of electric flux at the front and buried oxide-silicon interfaces, Equation (3) can be obtained.

$$\varphi_{j}(x,y) = \varphi_{sj}(x) + \frac{\varepsilon_{ox}}{\varepsilon_{si}} \times \frac{\varphi_{sj}(x) - V_{gs,f} + V_{FB,fj}}{t_{f}} y + \frac{c_{si}c_{b}(V_{gs,b} - V_{FB,bj}) + c_{f}(c_{si} + c_{b})(V_{gs,f} - V_{FB,fj}) - (c_{si}c_{b} + c_{f}c_{b} + c_{f}c_{si})\varphi_{sj}}{t_{si}^{2}(c_{si}c_{b} + 2c_{si}^{2})} y^{2},$$

$$L_{j-1} \leq x \leq L_{j}, 0 \leq y \leq t_{si}, j = 1,2,3$$

(3)

Here  $c_{si} = \frac{\varepsilon_{si}}{t_{si}}$ ,  $c_f = \frac{\varepsilon_{ox}}{t_f}$ , and  $c_b = \frac{\varepsilon_{ox}}{t_b}$ .

Using Eq. (3) in Eq. (1) and considering the independence of x and y, Equation (4) can be derived.

$$\frac{\mathrm{d}^{2}\varphi_{sj}(x)}{\mathrm{d}x^{2}} - \lambda^{2}\varphi_{sj}(x) = \beta_{j},$$

$$L_{j-1} \leqslant x \leqslant L_{j}, j = 1, 2, 3 \qquad (4)$$

Here  $\lambda = \left[\frac{2(c_{b}c_{si} + c_{f}c_{si} + c_{f}c_{b})}{t_{si}^{2}c_{si}(2c_{si} + c_{b})}\right]^{1/2}$  and

$$\beta_{j} = \frac{qN_{j}}{\varepsilon_{si}} - 2(V_{gs,f} + V_{FB,fj}) \frac{c_{f}(c_{si} + c_{b})}{t_{si}^{2}c_{si}(2c_{si} + c_{b})} - 2(V_{gs,b} - V_{FB,bj}) \frac{c_{b}}{t_{si}^{2}(2c_{si} + c_{b})}, \quad j = 1, 2, 3$$

where  $V_{\rm gs,f}$  is the front gate-to-source bias voltage,  $V_{\rm FB,fj}$  (j=1,2,3) is the front channel flat band voltage of zone j,  $V_{\rm gs,b}$  is the substrate bias voltage, and  $V_{\rm FB,bj}$  (j=1,2,3) is the back channel flat band voltage of zone j.

Equation (4) is a second-order differential equation with constant coefficients, and therefore the expression for the surface potential of the front channel is of the form:

$$\varphi_{sj}(x) = A_j e^{-\lambda x} + B_j e^{\lambda x} - \frac{\beta_j}{\lambda^2},$$

$$L_{j-1} \leqslant x \leqslant L_j, \ j = 1, 2, 3 \tag{5}$$

Using the continuity of electric flux and surface potential at the boundaries of the three silicon film zones, the built-in potential drop  $V_{\rm b}$  across the source-body junction, and the applied

drain-source bias  $V_{ds}$ , we can obtain the constants  $A_i$  and  $B_i$  (i = 1, 2, 3).

$$A_{1} = (V_{b1} + (1 - e^{\lambda L}) V_{gs,f})/2\sinh(\lambda L)$$

$$B_{1} = (V_{b2} + (e^{-\lambda L} - 1) V_{gs,f})/2\sinh(\lambda L)$$

$$A_{j} = A_{j-1} - e^{\lambda L_{j-1}} (\beta_{j-1} - \beta_{j})/2\lambda^{2}, \quad j = 2,3$$

$$B_{j} = B_{j-1} - e^{-\lambda L_{j-1}} (\beta_{j-1} - \beta_{j})/2\lambda^{2}, \quad j = 2,3$$

(6)

where

$$\begin{split} V_{\rm bl} &= (V_{\rm b} + \beta_{\rm l}/\lambda^2 + V_{\rm gs,f}) {\rm e}^{\lambda L} - \\ &(V_{\rm b} + V_{\rm ds} + \beta_{\rm 3}/\lambda^2 + V_{\rm gs,f}) - \\ \sum_{j=1}^2 {\rm cosh} [\lambda (L - L_j)] (\beta_j - \beta_{j+1})/\lambda^2 \\ V_{\rm b2} &= V_{\rm b} + V_{\rm ds} + \beta_{\rm 3}/\lambda^2 + V_{\rm gs,f} + \\ \sum_{j=1}^2 {\rm cosh} [\lambda (L - L_j)] (\beta_j - \beta_{j+1})/\lambda^2 - \\ &(V_{\rm b} + \beta_{\rm l}/\lambda^2 + V_{\rm gs,f}) {\rm e}^{-\lambda L} \\ L &= L_3 \end{split}$$

The electric field pattern along the channel determines the electron transport velocity through the channel. The electric field component in the x direction is given by differentiating  $\varphi_{sj}(x)$  (j=1, 2,3) with respect to x:

$$E(x) = -A_{j\lambda}e^{-\lambda x} + B_{j\lambda}e^{\lambda x},$$

$$L_{j-1} \leqslant x \leqslant L_{j}, j = 1,2,3$$

(7)

#### 2.2 Analytical threshold voltage

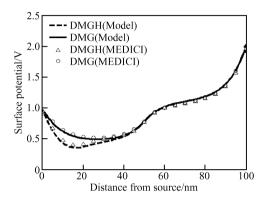

When the doping concentration  $N_{\rm A}$  is greater than  $N_{\rm B}$ , the minimum surface potential  $\varphi_{\rm smin}$  lies in zone 1, as shown in Fig. 2. The threshold volt-

age of the channel is determined by  $\varphi_{\rm smin}$ , which occurs where the differentiation of  $\varphi_{\rm sl}\left(x\right)$  is equal to zero and is as follows:

$$\varphi_{\rm smin} = 2\sqrt{A_1 B_1} - \beta_1/\lambda^2 \tag{8}$$

The threshold voltage is the value of the gate voltage at which a conducting channel is induced at the surface of an SOI MOSFET. In a fully depleted thin-film SOI MOSFET, it is desirable that the front channel turns on before the back channel. Therefore, the threshold voltage is taken to be the value of  $V_{\rm gs,f}$  for which  $\varphi_{\rm smin}=2\varphi_{\rm F}$ , where  $\varphi_{\rm F}$  is the difference between the extrinsic Fermi level in the bulk region and the intrinsic Fermi level. Considering  $t_{\rm b}\gg t_{\rm f}$  and  $t_{\rm b}\gg t_{\rm si}$  generally,  $V_{\rm th}$  can be derived from Eq. (8).

$$V_{\rm th} = \frac{-\eta + \sqrt{\eta^2 - 4\sigma\xi}}{2\sigma} \tag{9}$$

where

$$\begin{split} \sigma &= 2 \cosh(\lambda L) - 2 - \sinh^2(\lambda L) \\ \eta &= V_{b3} (\mathrm{e}^{-\lambda L} - 1) + V_{b4} (1 - \mathrm{e}^{\lambda L}) + \\ &\quad 2 \sinh^2(\lambda L) (2 \varphi_{\mathrm{F}} + U_1) \\ \xi &= V_{b3} V_{b4} - \sinh^2(\lambda L) (2 \varphi_{\mathrm{F}} + U_1)^2 \\ V_{b3} &= (V_b + U_1) \mathrm{e}^{\lambda L} - (V_b + V_{ds} + U_3) - \\ &\quad \sum_{j=1}^2 \cosh[\lambda (L - L_j)] (U_j - U_{j+1}) \\ V_{b4} &= V_b + V_{ds} + U_3 + \\ \sum_{j=1}^2 \cosh[\lambda (L - L_j)] (U_j - U_{j+1}) - (V_b + U_1) \mathrm{e}^{-\lambda L} \\ U_j &= \frac{q N_j t_{\mathrm{si}}}{c_{\mathrm{f}}} - (V_{\mathrm{gs,b}} - V_{\mathrm{FB,bj}}) \frac{c_b}{c_{\mathrm{f}}} + \\ V_{\mathrm{FB,fj}}, \quad j = 1, 2, 3 \end{split}$$

### 3 Model verification and discussion

Now we will analyze the performance of a DMGH in terms of DIBL, the threshold voltage roll-off, and carrier transport efficiency, and verify the models by comparing the results with simulations in MEDICI. Fully depleted SOI nMOSFETs are utilized in the analysis. Unless otherwise noted, the typical values of parameters are as follows.

For DMGH,  $W_1 = 4.77$ V,  $W_2 = 4.10$ V,  $V_{\rm gs.b} = 0$ V, drain and source doping concentration  $N_{\rm D} = 10^{20}\,{\rm cm^{-3}}$ ,  $N_{\rm A} = 4\times10^{17}\,{\rm cm^{-3}}$ ,  $N_{\rm B} = 10^{17}\,{\rm cm^{-3}}$ ,  $t_{\rm f} = 2\,{\rm nm}$ ,  $t_{\rm b} = 300\,{\rm nm}$ ,  $t_{\rm si} = 12\,{\rm nm}$ ,  $L_1 = 20\,{\rm nm}$ ,  $L_2 = 50\,{\rm nm}$ ,  $L_3 = 100\,{\rm nm}$ , and the work function of the buried gate is equal to  $W_1$ . For a conventional DMG (DMG with uniform doping profile),  $N_{\rm A} = 100\,{\rm mm}$

$10^{17}\,\mathrm{cm^{-3}}$  , and all the other parameters are the same as DMGH.

The surface potential along the front channel is plotted in Fig. 2. It can be seen from the figure that for a DMGH, an extra potential step profile exists near the halo boundary in addition to the one near the interface between the two gates in the DMG.

Fig. 2 Surface potential ( $V_{ds} = 1V$ ,  $V_{gs,f} = 0.3V$ )

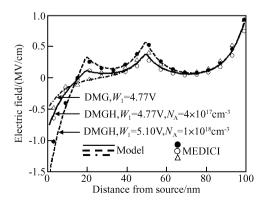

The surface electric field along the front channel is plotted in Fig. 3. It is shown that for a DMGH, there is an additional local electric field peak near the halo boundary and the peak will increase with increasing  $N_A$ . It can also be found that the other peak will increase when  $W_1$  is increased. Because the additional electric field peak is closer to the source, carriers will be accelerated earlier and travel through the channel more quickly in a DMGH than in a DMG. Therefore the transport efficiency of carriers in a DMGH is enhanced as compared with a DMG, and it will be further improved with the increase of  $N_A$  in some scope considering the degradation of mobility with increasing impurity concentration.

Fig. 3 Surface electric field ( $V_{ds} = 1V$ ,  $V_{gs,f} = 0.3V$ )

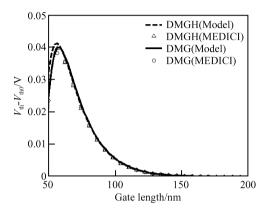

Figure 4 shows the threshold voltage roll-off with gate length, where  $V_{\rm th}$  is the threshold voltage of devices with short gate length and  $V_{\rm th0}$  is the  $V_{\rm th}$  value with a gate length of 200nm. It can be found that the threshold voltage of both structures exhibits inverse SCE, and the difference between them is small.

Fig. 4 Threshold voltage roll-off

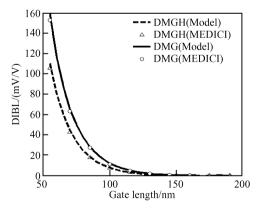

The DIBL can be expressed by  $\Delta V_{\rm th}/\Delta V_{\rm ds}$ . Figure 5 shows the DIBL variation in a DMGH and a DMG with gate length, where  $\Delta V_{\rm th} = V_{\rm th} \mid_{V_{\rm ds}=0} - V_{\rm th} \mid_{V_{\rm ds}=2}$  and  $\Delta V_{\rm ds}=2 \rm V$ . It is evident from the figure that the DMGH exhibits better suppression of DIBL, which results from the double effects of the asymmetrical halo and dual material gates.

Fig. 5 DIBL in DMGH and DMG ( $L_1:L_2:L_3=1:3:9$ )

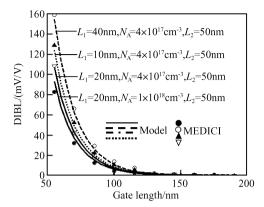

Figure 6 gives the DIBL variation in a DMGH under different halo structures. It is found that DIBL does not change monotonically with halo length and reaches a minimum when the halo length is around 20nm. The DIBL decreases with

increasing halo doping concentration.

Fig. 6 DIBL in DMGH under different halo structures

Figures 2 to 6 show that the derived models are in good agreement with MEDICI.

### 4 Conclusion

A novel structure called a dual material gate SOI MOSFET with a single halo is proposed to improve DIBL and carrier transport efficiency in the sub-100nm regime. The analytical models of surface potential and threshold voltage of the novel structure in the fully depleted condition are derived, and the characteristics are examined. The novel device shows better performance in suppressing DIBL and enhancing carrier transport efficiency than conventional dual material gate SOI MOSFETs. Its DIBL is reduced when the halo doping concentration is increased but does not change monotonically with halo length. The derived analytical models are in good agreement with the two-dimensional device simulator MEDI-CI.

### References

- [1] Saxena M, Haldar S, Gupta M, et al. Design considerations for novel device architecture; hetero-material double-gate (HEM-DG) MOSFET with sub-100nm gate length. Solid State Electron, 2004, 48(7):1169

- [2] Long W.Ou H, Kuo J M, et al. Dual material gate (DMG) field effect transistor. IEEE Trans Electron Devices, 1999, 46(5):865

- [3] Zhou X, Long W. A novel hetero-material gate (HMG) MOSFET for deep-submicron ULSI technology. IEEE Trans Electron Devices, 1998, 45(11):2546

- [4] Chaudhry A, Kumar M J. Investigation of the novel attributes of a fully depleted dual-material gate SOI MOSFET.

IEEE Trans Electron Devices, 2004, 51(9): 1463

- [5] Trivedi V P, Fossum J G. Nanoscale FD/SOI CMOS: thick or thin BOX. IEEE Electron Device Lett. 2005. 26(1):26

- [6] Miyamoto M, Toyota K, Seki K, et al. An asymmetrically doped buried-layer (ADB) structure for low-voltage mixed analog-digital CMOS LSIs. IEEE Trans Electron Devices, 1999,46(8):1699

- [7] Choi C, Kim K, Choi W. Design and analysis of a new self-aligned asymmetric structure for deep sub-micrometer MOS-FET. Solid-State Electron, 2001, 45(9):1673

- [8] Odanaka S, Hiroki A. Potential design and transport property of 0.1-\mu MOSFET with asymmetric channel profile. IEEE Trans Electron Devices, 1997, 44(1):595

- [9] Adan A O, Higashi K, Fukushima Y. Analytical threshold voltage model for ultrathin SOI MOSFET's including short-channel and floating-body effects. IEEE Trans Electron Devices, 1999, 46(4):729

- [10] Shin H, Lee S. An 0.1-µm asymmetric halo by large-angletilt implant (AHLATI) MOSFET for high performance and reliability. IEEE Trans Electron Devices, 1999, 46(4), 820

- [11] Hakim N. Dunga M V. Kumar A. et al. Analysis of floating body effects in thin film conventional and single pocket SOI

- MOSFETs using the GIDL current technique. IEEE Electron Device Lett, 2002, 23(4):209

- [12] Reddy G V, Kumar M J. Investigation of the novel attributes of a single-halo double gate SOI MOSFET: 2D simulation study. Microelectronics Journal, 2004, 35(9):761

- [13] Gan Xuewen, Huang Ru, Liu Xiaoyan, et al. Nanoscale CMOS devices. Beijing, Science Press, 2004 (in Chinese) [甘 学温,黄如,刘晓彦,等.纳米 CMOS 器件.北京:科学出版社, 2004]

- [14] Lin S C, Kuo J B. Closed-form analytical drain current model considering energy transport and self-heating for short-channel fully-depleted SOI NMOS devices with lightly-doped drain structure biased in strong inversion. IEEE Trans Electron Devices, 2002, 49(12):2193

- [15] Bolouki S, Maddah M, Ali A K, et al. A unified I-V model for PD/FD SOI MOSFETs with a compact model for floating body effects. Solid State Electron, 2003, 47(11):1909

- [16] Kumar M J. Chaudhry A. Two-dimensional analytical modeling of fully depleted DMG SOI MOSFET and evidence for diminished SCEs. IEEE Trans Electron Devices, 2004, 51 (4):569

## 异质栅非对称 Halo SOI MOSFET\*

李尊朝1, 蒋耀林2 吴建民2

(1 西安交通大学电子与信息工程学院,西安 710049) (2 西安交通大学理学院,西安 710049)

摘要:为了抑制异质栅 SOI MOSFET 的漏致势垒降低效应,在沟道源端一侧引入了高掺杂 Halo 结构.通过求解二维电势 Poisson 方程,为新结构器件建立了全耗尽条件下表面势和阈值电压解析模型,并对其性能改进情况进行了研究.结果表明,新结构器件比传统的异质栅 SOI MOSFETs 能更有效地抑制漏致势垒降低效应,并进一步提高载流子输运效率.新结构器件的漏致势垒降低效应随着 Halo 区掺杂浓度的增加而减弱,但随 Halo 区长度非单调变化.解析模型与数值模拟软件 MEDICI 所得结果高度吻合.

关键词:异质栅; SOI; 阈值电压; 解析模型

EEACC: 2560R: 2560B

中图分类号: TN386 文献标识码: A 文章编号: 0253-4177(2007)03-0327-05

<sup>\*</sup> 国家自然科学基金(批准号:60472003)和国家重点基础研究发展计划(批准号:2005CB321701)资助项目

<sup>†</sup>通信作者.Email:zcli@mail.xjtu.edu.cn