# Models and Related Mechanisms of NBTI Degradation of 90nm pMOSFETs $^{\ast}$

Cao Yanrong<sup>†</sup>, Ma Xiaohua, Hao Yue, Yu Lei, Zhu Zhiwei, and Chen Haifeng

(Key Laboratory of the Ministry of Education for Wide Band-Gap Semiconductor Materials and Devices, School of Microelectronics, Xidian University, Xi'an 710071, China)

Abstract: We investigate the negative bias temperature instability (NBTI) of 90nm pMOSFETs under various temperatures and stress gate voltages ( $V_{\rm g}$ ). We also study models of the time (t), temperature (T), and stress  $V_{\rm g}$  dependence of 90nm pMOSFETs NBTI degradation. The time model and temperature model are similar to previous studies, with small difference in the key coefficients. A power-law model is found to hold for  $V_{\rm g}$ , which is different from the conventional exponential  $V_{\rm g}$  model. The new model is more predictive than the exponential model when taking lower stress  $V_{\rm g}$  into account.

Key words: NBTI; 90nm; pMOSFETs; model

PACC: 7340Q; 7300; 7220J

CLC number: TN386.1 Document code: A

Article ID: 0253-4177(2007)05-0665-05

#### 1 Introduction

Negative bias temperature instability (NBTI) is an important effect in pMOSFETs. It didn't receive much attention for the larger devices of the past. However, as device sizes are continually scaling down without appropriate reduction of supply voltages, NBTI is getting more and more serious and has become one of the most important limiting factors of pMOSFET lifetime, especially for device sizes in the ultra-deep sub-micron region<sup>[1-3]</sup>.

Many people have studied NBTI and obtained lots of results, which count for much. However, there is still no model that explains NBTI exactly. In most studies, NBTI is thought to be related to H species [4~6]. As its name NBTI implies, negative bias and temperature play the most important roles in the degradation of pMOSFETs. With the effects of electric field and temperature, SiH bonds break, and therefore generate interface states and oxide positive charges [4.7], which cause the degradation of parameters  $V_{\rm th}$ ,  $I_{\rm dsat}$ ,  $I_{\rm dlin}$ ,  $G_{\rm m}$  and more. To model the effect of severe NBTI on

the performance of a pMOSFET, it is important to treat the degradation as dependent on  $V_{\rm g}$  and temperature. In addition, the time model, which has been studied for a long time, is also significant.

In this paper, we examine NBTI degradations of 90nm devices in long term stresses under different conditions, including various  $V_{\rm g}$  and T. Based on the results, models dependent on t, T, and  $V_{\rm g}$  are studied.

### 2 Devices and experiments

The pMOSFETs used here were fabricated in 90nm process technology with a lightly doped drain (LDD) structure and a shallow trench isolation (STI) scheme. The devices have a channel length of 90nm, width of  $10\mu m$ , and gate oxide thickness of 1. 4nm. The gate oxides of all devices were annealed in N<sub>2</sub>O gas ambient after thermal growth. The operation voltage is 1.0V. An Agilent B1500A high precision semiconductor parameter analyzer was used to complete the tests. NBTI stress was applied to the gate electrode, with the source, drain, and substrate grounded at elevated

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (No. 60376024) and the National High Technology Research and Development Program of China (No. 2003AA1Z1630)

<sup>†</sup> Corresponding author. Email: yrcao200@163.com

temperatures. Stress testing combined with I-V measurement were performed at  $90\sim150\,^{\circ}\mathrm{C}$  in a dark box.

#### 3 Results and discussion

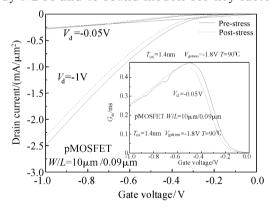

Figure 1 shows the degradation of the transfer characteristics of the pMOSFETs. The pMOS-FETs were stressed under  $V_g = -1.8V$  at  $90^{\circ}$ C. After 10000s, the drain current appears clearly degraded, and the current in the saturation region is degraded more than that in the linear region. The threshold voltage  $V_{\mathrm{th}}$  becomes larger than the former. From the inset in Fig. 1, we can see that  $G_{\rm m}$ after 10000s decreases, and the peak point shifts left. This is due to the interface states and fixed oxide charges produced during NBTI stress. From the figure, we can see the serious degradation caused by NBTI clearly. This degradation will result in the final failure of the devices and affect the circuits badly. Therefore, it is important to study NBTI and to found models for key factors.

Fig. 1 Degradation of transfer characteristics of 90nm pMOSFETs pre- and post-NBTI stress with  $V_{\rm g}$  = -1.8V at 90°C for 10000s

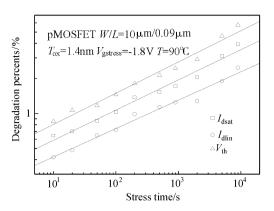

The shifts of the pMOSFET parameters with stress  $V_{\rm g} = -1.8 \, {\rm V}$  versus stress time are shown in Fig. 2.  $I_{\rm dsat}$  shifts more than  $I_{\rm dlin}$ , indicating that the interface states and oxide fixed charges produced during NBTI stress are located not in the overlap region but in the channel region. The degradation of the threshold voltage  $V_{\rm th}$  is the most severe. We will study it to model the degradation caused by pivotal factors.

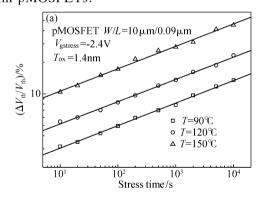

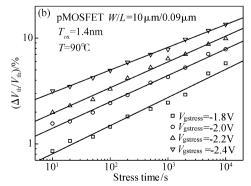

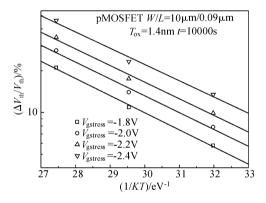

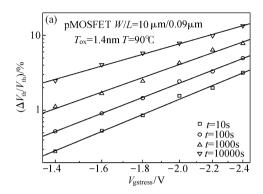

Figure 3 shows the relation of  $V_{\rm th}$  degradation to time at different temperatures or under different stresses  $V_{\rm g}$ . All data are plotted in a loglog scale.  $V_{\rm th}$  shifts show excellent accordance to

Fig. 2 Shifts of 90nm pMOSFET parameters with  $V_{\rm g}$  = -1.8V versus stress time

$t^n$ . Though this time model was brought forward a long time ago, and has been confirmed by most studies, the parameter n is different for different devices manufactured by different technologies [5.8.9]. And when the device scale reaches 90nm, it is important to identify the t model. In Fig. 3 (a), at different temperatures, n shows a nearly constant value of 0. 21, and in Fig. 3 (b), n decreases from 0. 26 to 0. 21, as the stress  $V_{\rm g}$  increases. All of these results are similar to those of previous studies and show that the model  $\Delta V_{\rm th} = Ct^n$  can also account for NBTI degradation of 90nm pMOSFETs.

Fig. 3  $V_{\rm th}$  shift versus stress time at different temperatures (a) or under different  $V_{\rm gstress}$  (b)

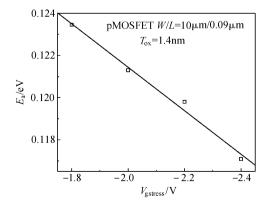

The shift of  $V_{th}$  versus temperature under different stresses  $V_{\rm g}$  is plotted in Fig. 4 with a loglinear scale. All data under different stresses  $V_{\sigma}$ are fitted with  $\Delta V_{\rm th} = C \exp(-E_{\rm a}/KT)$ , where  $E_{\rm a}$ is the activation energy. The activation energy  $E_a$ of  $\Delta V_{\rm th}$  for each stress  $V_{\rm g}$  is extracted from the data of Fig. 4. The results are shown in Fig. 5.  $E_a$ represents the difficulty of NBTI degradation. In Fig. 5,  $E_a$  decreases with increasing stress  $V_g$ , which implies that stress  $V_{\rm g}$  plays an important role in NBTI degradation. The range of E<sub>a</sub> in Fig. 5 is  $0.11 \sim 0.13 \text{ eV}$ , which is smaller than that in previous studies, in which the device scale was larger<sup>[10]</sup>. From these results, we conclude that higher stress  $V_{\rm g}$  and smaller device scale result in the easier occurrence of NBTI degradation. Therefore, we can also use  $\Delta V_{\rm th} = C \exp (-E_{\rm a}/$ KT) as the T model of 90nm pMOSFET NBTI degradation. However, the activation energy is smaller.

Fig. 4  $V_{\rm th}$  shift versus temperature under different  $V_{\rm gstress}$

Fig. 5 — Activation energy (  $E_{\rm a}$  ) of  $V_{\rm th}$  shift versus  $V_{\rm gstress}$

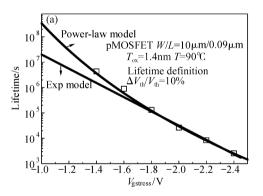

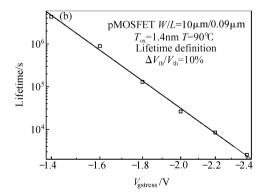

From studies on NBTI with regard to time and temperature, we have known the importance of stress  $V_{\rm g}$ . Accelerated testing is usually used to evaluate the lifetime of devices. A high gate voltage  $V_{g}$  is applied to a pMOSFET to measure its lifetime in NBTI studies. Some researchers have proposed a model of the dependence of lifetime  $(\tau)$  on  $V_{\mathfrak{g}}$  to estimate the lifetime at operation voltages<sup>[2]</sup>. The conventional exponential model is  $\tau = C \exp((-\beta V_g))$ , where C and  $\beta$  are constants. From this lifetime model, we deduce that the model of  $\Delta V_{\text{th}}$  is dependent on  $V_{\text{g}}$  as  $\Delta V_{\text{th}} =$  $C_1 \exp (\beta_1 V_g)$ , where  $C_1$  and  $\beta_1$  are also constants. Both of these models are used by manufacturers to estimate the  $V_{\rm th}$  shift and lifetime of devices. In this paper, we take the 10% shift of  $V_{\rm th}$  as the lifetime definition. The data gained under higher stress  $V_{\rm g}$  agree well with both exponential models. However, when the stress  $V_g$  reaches a smaller value, but still higher than operation voltage, the exponential model departs from the experimental data, as shown in Fig. 6 (a). We change the loglinear scale into a log-log scale, and therefore

Fig. 6 (a) Comparison of exp model and power-law model; (b) Power-law model:  $\tau = CV_{\rm g}^{-\beta}$  All data fit well with power-law model.

make the exponential model into the power-law model  $\tau = C \ V_{\rm g}^{-\beta}$ , where C and  $\beta$  are constants. For all data, lifetime under higher and lower stresses  $V_{\rm g}$ , the power-law model is more predictive than the exponential model, as shown in Fig. 6 (b). Taking lower stress  $V_{\rm g}$  into account, the exponential model underestimates the NBTI lifetime of 90nm pMOSFETs. Therefore, the power-law  $V_{\rm g}$  model should be instead of the exponential model to predict the NBTI lifetime of ultra-deep sub-micron MOSFETs. We deduce the  $\Delta V_{\rm th}$  model dependent on  $V_{\rm g}$  from the power-law model of lifetime. The NBTI lifetime of the power-law  $V_{\rm g}$  model is  $\tau = C \ V_{\rm g}^{-\beta}$ , which can be expressed in another form:

$$\lg \tau = \lg C - \beta \lg V_{g} \tag{1}$$

We use t (time) instead of  $\tau$ , and both sides are multiplied by n (the parameter of the time model):

$$\lg t^n = \lg C^n - \lg V_{\mathfrak{g}}^{n\beta} = \lg (C_1 V_{\mathfrak{g}}^{-\beta_1}) \qquad (2)$$

Here  $C_1$  is equal to  $C^n$ , and  $\beta_1$  is equal to  $n\beta$ . From Eq. (2), we can get

$$t^{n} = C_1 V_{g}^{-\beta_1} \tag{3}$$

$$C_2 t^n = \Delta V_{\text{th}} V_{\text{g}}^{-\beta_2} \tag{4}$$

where  $\Delta V_{\rm th}/C_2$  is equal to  $C_1$ ,  $\beta_2$  is equal to  $\beta_1$ , and  $\Delta V_{\rm th}$  is the lifetime definition of the devices. Therefore, taking no account of the time t, we can get the  $\Delta V_{\rm th}$  model dependent on  $V_{\rm g}$ :

$$\Delta V_{\rm th} = C_0 V_{\rm g}^{\beta_0} \tag{5}$$

Here  $C_0$  and  $\beta_0$  are constants.

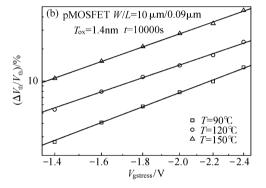

Figure 7 shows that the power-law  $V_{\rm g}$  model for  $V_{\rm th}$  shift agrees well with the experimental data. Figure 7 shows  $V_{\rm th}$  shift at different times (a) and at different temperatures (b). All data fit well with the new deduced power-law  $V_{\rm g}$  model.

#### 4 Conclusions

We examine NBTI degradations of 90nm devices in long term stresses under different conditions. Based on the results, we studied the models of the dependence of NBTI degradation of 90nm pMOSFETs on time, temperature, and stress  $V_{\rm g}$ . The t model  $\Delta V_{\rm th} = C t^n$  is also used, where n is similar to that of previous studies.  $\Delta V_{\rm th} = C \times \exp{(-E_{\rm a}/KT)}$  can be used as the T model of 90nm pMOSFET NBTI degradation. However, the activation energy is smaller. The conventional exponential model is not precise for predicting the

NBTI lifetime of 90nm pMOSFETs taking lower stress  $V_{\rm g}$  into account. We found a power-law  $V_{\rm g}$  model which is more predictive. Finally, the NBTI degradation model dependent on stress  $V_{\rm g}$  is deduced:  $\Delta V_{\rm th} = C V_{\rm g}^{\beta}$ . All data show that the models are good approximations.

Fig. 7 Power-law  $V_{\rm g}$  model for  $V_{\rm th}$  shift:  $\Delta V_{\rm th} = C_0 V_{\rm g}^{\beta_0}$  at different times (a) and at different temperatures (b) All data fit well with power-law  $V_{\rm g}$  model.

#### References

- [1] Jeon C H, Kim S Y, Kim H S, et al. The impact of NBTI and HCI on deep sub-micro pMOSFETs' lifetime. IEEE IRW Final Report, 2002:130

- [2] Wen S J, Hinh L, Puchner H. Voltage acceleration NBTI study for a 90nm CMOS technology. IEEE IRW Final Report, 2003:147

- [3] Chen Y F, Lin M H, Chou C H, et al. Negative bias temperature instability (NBTI) in deep sub-micron p<sup>+</sup>-gate pMOS-FETs. IEEE IRW Final Report, 2000:98

- [4] Schroder D K, Babcock J A. Negative bias temperature instability:road to cross in deep submicro silicon semiconductor manufacturing. J Appl Phys, 2003, 94(1):1

- [5] Li Z H, Liu H X, Hao Y. Mechanism of NBTI degradation in ultra deep submicron pMOSFET's. Acta Physica Sinica, 2006,55(2).820

- [6] Huard V, Monsieur F, Ribes G, et al. Evidence for hydrogenrelated defects during NBTI stress in p-MOSFETs. IEEE IR-PS, 2003;178

- [7] Rashkeev S N, Fleetwood D M, Schrimpf R D, et al. Proton-Induced defect generation at the Si-SiO<sub>2</sub> interface. IEEE Trans Nucl Sci, 2001, 48(6):2086

- [8] Chen M G, Li J S, Jiang C, et al. NBTI mechanism explored on the back gate bias for pMOSFETs. IEEE IRW Final Report, 2003; 131

- [9] Jeppson K O, Svensson C M. Negative bias stress of MOS devices at high electric field and degradation of MNOS devices. J Appl Phys, 1977, 48(5); 2004

- [10] Chaparala P, Shibley J, Lim P. Threshold voltage drift in pMOSFETS due to NBTI and HCI. IEEE IRW Final Report, 2000, 95

## 90nm pMOSFETs NBTI 退化模型及相关机理\*

曹艳荣 马晓华 郝 跃 于 磊 朱志炜 陈海峰

(西安电子科技大学微电子学院 宽禁带半导体材料与器件教育部重点实验室,西安 710071)

摘要:对 90nm pMOSFETs 在不同温度及栅压应力下的 NBTI 效应进行了研究,从而提出了 90nm pMOSFETs NBTI 退化对时间 t、温度 T 及栅压应力  $V_g$  的模型.时间模型及温度模型与过去研究所提出的模型相似,但是关键 参数有所改变.栅压应力模型遵循双对数关系,这与传统的单对数栅压应力模型不同.将较低的栅压应力也考虑在内时,双对数栅压应力模型较单对数栅压应力模型更为准确.

关键词: NBTI; 90nm; pMOSFETs; 模型

PACC: 7340Q; 7300; 7220J

中图分类号: TN386.1 文献标识码: A 文章编号: 0253-4177(2007)05-0665-05

<sup>\*</sup>国家自然科学基金(批准号:60376024)和国家高技术研究发展计划(批准号:2003AA1Z1630)资助项目

<sup>†</sup>通信作者.Email:yrcao200@163.com 2006-11-16 收到,2006-12-20 定稿