# 抗辐射 128kb PDSOI 静态随机存储器

> (1 中国科学院半导体研究所,北京 100083) (2 传感器技术国家重点实验室,北京 100083) (3 中国电子科技集团第 58 研究所,无锡 214035)

摘要:介绍在部分耗尽绝缘体上硅(PD SOI)衬底上形成的抗辐射 128kb 静态随机存储器.在设计过程中,利用 SOI 器件所具有的特性,对电路进行精心的设计和层次化版图绘制,通过对关键路径和版图后全芯片的仿真,使得芯片一次流片成功.基于部分耗尽 SOI 材料本身所具有的抗辐射特性,通过采用存储单元完全体接触技术和 H型 栅晶体管技术,不仅降低了芯片的功耗,而且提高了芯片的总体抗辐射水平.经过测试,芯片的动态工作电流典型值为 20mA@10MHz,抗总剂量率水平达到 500krad(Si),瞬态剂量率水平超过 2.45×10<sup>11</sup> rad(Si)/s.这些设计实践必将进一步推动 PD SOI CMOS 工艺的研发,并为更大规模抗辐射电路的加固设计提供更多经验.

关键词: 部分耗尽绝缘体上硅; 静态随机存储器; 加固设计

EEACC: 1265D; 2570A; 2550R

中图分类号: TP333.8 文献标识码: A 文章编号: 0253-4177(2007)07-1139-05

### 1 引言

先进的部分耗尽绝缘体上硅(partial-depletion silicon-on-insulator,PD SOI)技术适于辐照环境下的高速、低功耗应用. 大规模静态随机存储器(static random access memory,SRAM)是这项技术的成功实例之一. 1991 年,美国 Harris 公司推出基于  $1.2\mu m$  CMOS SOS(silicon on sapphire,蓝宝石上硅)技术的  $8k \times 8bit$  抗辐射 SRAM,其抗总剂量水平超过  $1 \times 10^5$  rad(Si),成为抗辐射 SRAM 产品的里程碑. 1993 年,Lu 和 Yee 等人宣布在  $0.8\mu m$  SI-MOX SOI 衬底上成功研制出 1Mbit 的抗辐射 SRAM<sup>[1]</sup>. 1996 年,Honeywell 公司又推出商用的  $32k \times 8bit$  的抗辐射 SRAM,该款产品应用极为广泛,采用的就是  $0.55\mu m$  的抗辐射 SOI 技术,其抗总剂量水平已超过  $1 \times 10^6$  rad(Si) [2].

本文所介绍的抗辐射 128kb SRAM,是国内首次独立设计并流片成功的如此大规模的抗辐射静态随机存储器.文中较为详细地介绍了芯片的研制过程和测试结果.

# 2 128kb SRAM 的总体布局与阵列 划分

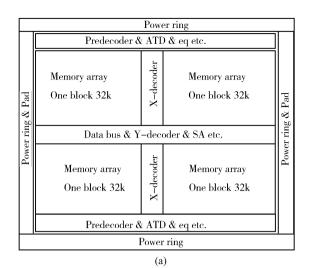

如图 1(a)所示,输入输出管脚单元(I/O PAD)

和电源环放置在芯片外侧,中间部分是存储阵列、地址译码器和数据总线等存储器的核心逻辑.

图 1(b)给出该 SRAM 的阵列划分情况.存储阵列包含 256×512 个六管存储单元,分为上下两个拥有同样结构的 Bank.每个 Bank 均包含左右两个128×256 的 Block,共用一组地址转换探测(address transition detection,ATD)电路.由于异步存储器的读写操作均需要 ATD 信号的触发才能启动,因此在功耗方面比同步 SRAM 更有优势.每个Block 阵列包含一个主字线(master word line,MWL)译码器,用于产生主(一级)字线信号.每个Block 又包含 8 组 4kb 大小的 Section,每个 Section有一组本地字线(local word line,LWL)译码器,产生本地(二级)字线信号.两级字线结构使得每次读写操作过程中仅有一个 Section 中的一条本地字线被激活,从而降低存储器芯片的总体功耗.

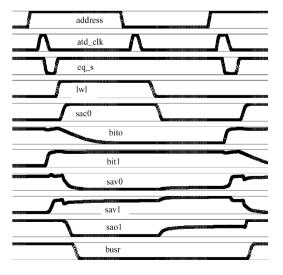

# 3 字线结构与关键路径

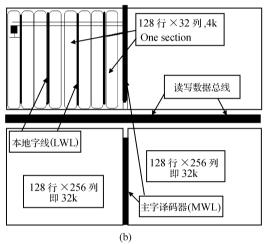

位线(bit line,BL)是 SRAM 功耗、延时的主要组成部分<sup>[3]</sup>.图 2 给出了该 SRAM 的位线结构.从上至下依次为:由"EQ"信号驱动的位线预充电路,交叉耦合上拉电路(cross-coupled pull up pair circuit,CPP),存储单元,CMOS 列选开关,子阵列数据线,灵敏放大器和写入缓冲.由于读写过程中为"1"一侧的位线电位可能被存储单元拉至  $V_{DD}$  –

图 1 (a)128kb CMOS/SOI SRAM 总体布局示意图;(b) 存储阵列划分示意图

Fig. 1 (a) Floorplan of 128kb CMOS/SOI static RAM; (b) Memory array floorplan

$V_{\text{TN}}$ ,因此引入了 CPP. CPP 的作用是在读、写过程中把为"1"的 BL 电位保持在  $V_{\text{DD}}$ ,以提高并稳定读写速度. 4 组位线共用一个灵敏放大器 (sense amplifier, SA). SA 的启动受使能信号 sac0 的控制,仅在读操作时有效,同样达到降低功耗的目的.

如图 2 所示,关键路径的选取是 SRAM 设计过程中重要的一步.从地址信号开始,触发 ATD 电路,生成 EQ 信号,然后激发位线预充、字线,列选打开,灵敏放大器开启,数据总线进行读写操作,这是一条关键的信号通路.为了能够模拟这些关键信号的最坏情况,选择位于距离字线译码器最远的列上的两个存储单元,一个单元距离灵敏放大器最远,另一个则距灵敏放大器最近.此外,将数据 IO PAD 加入会使关键路径更接近实际情况[4].

将各部分的版图进行寄生参数提取,将寄生 R,C值带入到关键路径的网表中,利用 HSPICE 工具进行电路仿真,根据仿真结果不断对网表进行

图 2 静态随机存储器的位线结构示意图

Fig. 2 Bitline structure of static RAM

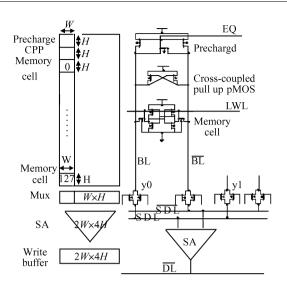

修改,最终使关键路径能在各种参数模型和温度情况下正常工作.图 3 给出的是一次读写操作中,关键路径上某些重要节点的仿真结果.

### 4 抗辐射加固设计

除了正确的电学性能参数设计之外,抗辐射性能的提高也是该电路设计的重点. SOI 材料本身具有天然的抗辐射性能,但仅仅依靠这些还远远不够. 因此,特别采用了存储单元完全体接触、晶体管 H型栅等多项技术,并通过精心的版图设计来提高整个电路的抗辐射加固性能.

图 3 关键路径的 SPICE 仿真结果

Fig. 3 SPICE simulation results of SRAM critical path

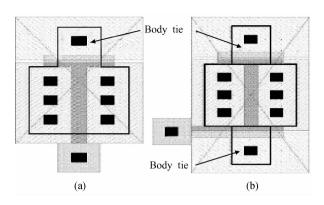

图 4 (a)T型栅体接触结构;(b)H型栅体接触结构 Fig. 4 (a) T-type body-tie structure;(b) H-type body-tie structure

### 4.1 存储单元完全体接触技术

浮体(floating body)是影响部分耗尽 SOI 基电路抗总剂量性能的主要因素.为了抑制浮体效应并减少辐照过程中的瞬态寄生三极管(BJT)电流,对存储单元中的 pMOS 管和 nMOS 管均进行体接触.通过把存取门管(access transistor)的体区接地来引走体区内多余的空穴,以限制并稳定体区电位,避免触发 BJT 效应.同时,稳定的体电位也使得单元两侧的位线寄生电容负载失配得以大大减轻[5].

对一个未选中的存储单元在写周期中的最坏情况进行模拟.单元门管为浮体时,当位线电位下降使得体源结正偏以后,就触发了 BJT 效应,引发相当大的体源电流,测得瞬态 BJT 电流峰值达到  $48\mu A/\mu m$ ,电流平均值为  $17\mu A/\mu m$ .对六管单元中所有晶体管进行体接触后,重新进行模拟,体源电流峰值降低至  $1.8\mu A/\mu m$ ,电流平均值为  $0.75\mu A/\mu m$ .流片之后的测试结果也表明,这样的存储单元不但保证了抗辐射性能,而且也显著降低了整个芯片的静态泄漏电流和动态工作电流.

#### 4.2 晶体管 H 型栅技术

通常采用的体接触结构是 T 型栅体接触,如图 4(a) 所示. 在器件一端把栅做成 T 字型. 对于 nMOS 管,在栅外侧形成  $p^+$  有源区与栅下面的  $p^-$  体区相连,从而把体区引出. 但是,受制于较大的体接触电阻,T 型栅体接触不宜应用在宽尺寸器件上.

为了增强体接触的抗辐射性能,对 T 型栅体接触做了一些改进,得到 H 型栅体接触结构,如图 4 (b)所示.在 T 型栅体接触的对面也形成一个同样的体接触结构.由于 H 型栅在有源区的两侧均安排了体接触,使浮体中产生的辐射电荷能够更快地传出,从而显著降低浮体效应所带来的影响,提高整个芯片的抗辐射性能<sup>[6]</sup>.

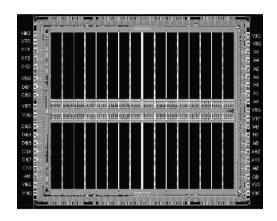

图 5 128kb SOI SRAM 最终版图 Fig. 5 Final layout of 128kb SOI SRAM

## 5 SRAM 的流片和封装

该 SRAM 的版图绘制是完全定制的层次化设计,其最终版图如图 5 所示,芯片达到 100 万晶体管规模.

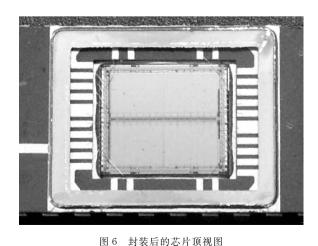

芯片的加工在中电集团 58 所进行,采用  $0.8\mu m$  CMOS/SOI 工艺,125mm SIMOX SOI 基片,浅槽隔离,3 层金属布线.电路一次流片成功.芯片采用 28Pin 双列直插封装(DIP).图 6 是封装后的芯片顶视图.

# 6 电学参数测试与辐照实验结果

对封装后的成品进行功能测试和电学参数测试,这些测试均在中电集团 58 所进行.

功能测试采用通用的 MARCH(II), MAS-EST, GALROW, GALCOL, CHECKERBOARD (& BAR)测试图形. 这些测试程序利用 Perl 软件编写,使测试程序的编写速度和测试图形的准确性得

图 5 到装后的心片 灰枕图 Fig. 6 Topview of packaged SRAM chip

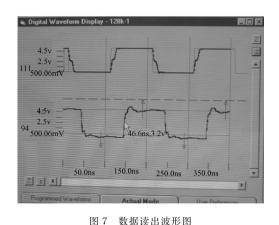

图 / 数据跃山级形图

Fig. 7 Data output waveform

到很大提高.经过测试,芯片可以通过所有图形,表明其读写功能、邻位打扰特性等均正常.

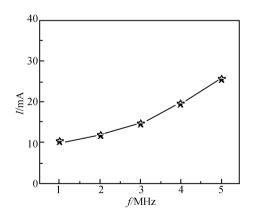

地址存取时间的测试在 5V,25°C,5MHz 条件下进行,结果如图 7 所示(111 为地址波形,94 为数据通路波形). 测得典型的地址读出时间为 25ns. 芯片静态等待电流约为  $500\mu$ A,在 10MHz 频率下测试,其工作电流约为 20mA. 如图 8 所示,计算可得,芯片的平均工作功耗增加值为 5mW/MHz.

总剂量辐照实验在西北核技术研究院的 Co60 辐射源上进行,参照美国军标 883E 的要求,辐照过程中芯片处于静态等待状态,并对其静态功耗进行实时监测;在达到要求的总剂量水平后停源,采用在位测试的方法对 SRAM 芯片进行测量.典型样品的测试情况如表 1 所示,实验中分别设定了 1×10<sup>5</sup>,3×10<sup>5</sup>,4×10<sup>5</sup> 和 5×10<sup>5</sup> rad(Si)四个总剂量水平.结果表明,该款静态随机存储器的抗总剂量率(TID)

图 8 典型 IDDOP 数值 Fig. 8 Typical IDDOP value

表 1 CMOS/PDSOI 128kb SRAM 样品辐照条件及结果

Table 1 Sample radiation condition and result of 128kb

CMOS/PDSOI SRAM

| 总剂量累计           | 工作电压       | 辐照前后读写 | 工作电流 | 读写功能 | 测试条件          |

|-----------------|------------|--------|------|------|---------------|

| /rad(Si)        | / <b>V</b> | 频率/MHz | /mA  | 是否正常 | 侧风尔什          |

| 0(辐照前)          | 5          | 5      | 10.3 | 正常   |               |

| $1 \times 10^5$ | 5          | 5      | 9.8  | 正常   | <10min        |

| $3 \times 10^5$ | 5          | 5      | 36.1 | 正常   | <10min        |

| $4 \times 10^5$ | 5          | 5      | 58.6 | 正常   | <10min        |

| $5 \times 10^5$ | 5          | 5      | 65.1 | 正常   | $<$ 30 $\min$ |

水平达到 500krad(Si),抗瞬态剂量率水平超过  $2.45 \times 10^{11}$  rad(Si)/s.非常适于在一些具有特殊要求的辐照环境中应用.

### 7 结论

抗辐射的 SRAM 芯片是军事和航空应用中的核心芯片之一.本文在部分耗尽 SOI 材料本身所具有的抗辐射特性的基础上,对电路进行特殊的加固设计和精心的版图绘制,使最终 SRAM 芯片的静态等待电流小于 1mA,在 10MHz 主频下工作电流约为 20mA. 同时测得 SRAM 芯片的 TID 达到500krad(Si),抗瞬态剂量率水平超过 2.45×10<sup>11</sup> rad (Si)/s.这些设计实践必将进一步推动部分耗尽 SOI CMOS 工艺的研发,并为更大规模抗辐射电路的加固设计提供更多经验.

#### 参考文献

- [1] Lu H. Yee E. Hite L. et al. 1-M bit SRAM on SIMOX material. Proc IEEE Int SOI Conf, 1993;182

- [2] http://www.ssec.honeywell.com/aerospace/datasheets/ HLX6256.pdf

- [3] Kuang J B, Ratanaphanyarat S, Saccamango M J, et al. SRAM bitline circuits on PD SOI; advantages and concerns. IEEE J Solid-State Circuits, 1997, 32(6);837

- [4] Zhao Kai, Jiang Fan, Liu Zhongli. Design and simulation of 0.8 µm PDSOI CMOS 128k SRAM. Proc of the 6th National SOI Technology Conference, Xi'an, 2005; 120 (in Chinese) [赵凯,姜凡,刘忠立. 0.8 µm PD SOI CMOS 128K SRAM 的设计及仿真. 第六届全国 SOI 技术研讨会论文集,西安, 2005;120]

- [5] Lu P F. Chuang C T. Ji J. et al. Floating body effects in partially depleted SOI CMOS circuits. IEEE J Solid-State Circuits, 1997, 32(8):1241

- [6] Damiano J, Franzon P D. Integrated dynamic body contact for H-gate PD-SOI MOSFETs for high performance/low power. IEEE International SOI Conference, 2004:115

#### Radiation-Hardened 128kb PDSOI CMOS Static RAM

Zhao Kai<sup>1,2,†</sup>, Liu Zhongli<sup>1,2</sup>, Yu Fang<sup>1,2</sup>, Gao Jiantou<sup>1,2</sup>, Xiao Zhiqiang<sup>3</sup>, and Hong Genshen<sup>3</sup>

(1 Integrated Technology Center, Institute of Semiconductors, Chinese Academy of Sciences,

Beijing 100083, China)

(2 State Key Laboratories of Transducer Technology, Beijing 100083, China)

(3 The 58th Institute, CETC, Wuxi 214035, China)

Abstract: A radiation-hardened 128kbit asynchronous SRAM fabricated in partial depletion silicon on insulator substrate is presented. Special characteristics of SOI devices are used in the design process. After careful circuit design, hierarchical layout design, and simulation of critical path, the SRAM chip was fabricated in the first turn-out. Besides the radiation-hardened characteristics of SOI material, fully-body-tied 6T memory cell and H-type gate MOSFETs techniques are also implemented in this PDSOI SRAM. These advanced techniques reduce the power consumption and raise the radiation-hardened level of this SRAM. The final testing shows that the 128k bit SOI SRAM has a typical operating current of 20mA at 10MHz, total dose tolerance of 500krad(Si), and dose rate survivability of 2. 45 × 10<sup>11</sup> rad (Si)/s. The implementation of radiation-hardened 128k SOI SRAM will accelerate the development of PD SOI CMOS processes, and will surely contribute more to the radiation design of VLSI circuits in the future.

Key words: partial-depletion SOI; static RAM; radiation hardened design EEACC: 1265D; 2570A; 2550R

Article ID: 0253-4177(2007)07-1139-05

<sup>†</sup> Corresponding author. Email: zhaokai@red. semi. ac. cn Received 17 January 2007, revised manuscript received 5 March 2007