Vol. 28 No. 12 Dec., 2007

# 基于RT器件的三值与非门、或非门电路设计

歌<sup>1,2,†</sup> 吕伟锋<sup>1</sup> 孙玪玪<sup>1,2</sup>

(1 杭州电子科技大学 电子信息学院, 杭州 310018) (2 浙江大学信息与电子工程学系, 杭州 310027)

摘要:共振隧穿(resonant tunnel, RT)器件本身所具有的微分负阻(negative differential resistance, NDR)特性使 其成为天然的多值器件. 文中利用 RT 器件的负阻特性,以开关序列原理为指导,设计了基于 RT 电路的开关模型, 实现了更为简单的三值 RT 与非门和或非门电路,并利用 MOS 网络模型,通过 SPICE 软件仿真验证了所设计电路 的正确性.该设计思想可推广到更高值的多值电路设计中.

关键词: RT 器件; 多值逻辑; 开关序列; 与非门; 或非门

**EEACC**: 1265Z

中图分类号: TN312.2 文献标识码: A 文章编号: 0253-4177(2007)12-1983-05

#### 1 引言

目前计算机科学中主要使用的是二值数字电 路,以布尔代数为基础,以基本门电路作为构造单元 进行设计[1~3]. 而使用多值逻辑可以使每根连线携 带的信息量增加,从而减少数字系统的连线,降低电 路复杂度,减小芯片面积,且多值逻辑的结构比二值 更加丰富.因此三、四值以及更高值的逻辑已经在计 算机科学中得到应用,并将进一步扩大应用范围.

多值逻辑的研究目标是为了设计和应用多值逻 辑电路. 多值逻辑电路在结构简单性、工作可靠性、 速度、功耗等方面均可以与成熟的二值电路相比甚 至更优, 迄今为止, 具有各种逻辑功能的多值门电路 已经被提出.如今共振隧穿二极管(resonant tunneling diode, RTD) 等量子器件的制造工艺技术已经 开始成熟,其固有的超高速、超高频、超高集成度、高 效、低功耗等特点,在未来 VLSI 方面有着极其重要 的应用前景[4~9]. 本文将探讨利用共振隧穿器件实 现三值"与非门"、"或非门"单元电路,为用 RT 器件 实现三值逻辑电路提供一种新的思路.

### 共振隧穿器件

### 2.1 RTD 和三端 RTT 器件

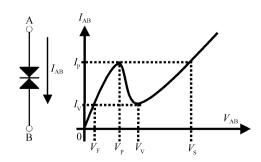

RTD 是基于半导体异质结构的量子器 件[10,11],其电路符号和 I-V 特性曲线如图 1 所  $\vec{\pi}^{[12,13]}$ .

由图 1 可以看出 RTD 具有两个正的斜率区和 一个负的斜率区. 当 RTD 工作在正斜率区(称为导 通状态,表现出一般 pn 结特性,导通电阻很小)时, 具有稳定的工作点. 在这里把 RTD 从第一正阻抗 区(原点到  $V_{\rm P}$ )进入到负阻区( $V_{\rm P}$  到  $V_{\rm V}$ )这个过程 称为翻转,翻转后的 RTD 管具有较大的负阻抗 值[14].

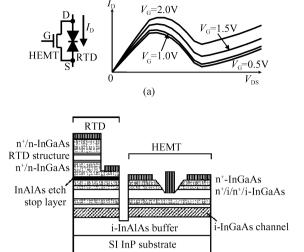

相对于二端 RTD 来说,将 RTD 与一些成熟的 Ⅲ-V族材料器件(例如 HBT 和 HEMT 等)集成在 一起获得三端 RT 器件来设计电路会更为灵活[9]. 图 2(a)为 RTD/HEMT 的电路符号及其 I-V 特性 曲线,从图中可以看出 RTD/HEMT 的 I-V 特性曲 线与RTD相似,其峰值电流随着输入电压 $V_G$ 的增 大而增大,且峰值电流小的管子先从第一正阻抗区 进入负阻区,发生翻转,因此它是一种压控器件,可 以通过控制输入电压  $V_{\rm G}$  的大小来控制管子的工作 状态. RTD/HEMT 为现今较为热门的研究方向,其

图 1 RTD 的符号及其 I-V 特性曲线

Fig. 1 Symbol and I-V characteristic of RTD

图 2 RTD/HEMT 符号、I-V 特性曲线(a) 及结构(b) Fig. 2 Cross-section structure(b), symbol and I-V characteristic curves (a) of RTD/HEMT

(b)

结构如图 2(b)所示. RTD/HETM 可以形成新的电路族,RTD 与传统的晶体管进行单独优化,这种单独的优化对于再制造以及统一样式这些与集成工艺紧密相关的技术是非常有好处的. 最重要的是,这些综合利用技术可以使 RTD 作为电路的核心器件,电路性能将会得到大幅度地提高.

#### 2.2 RTD 的电路模型

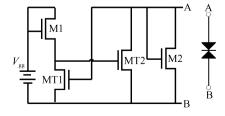

由于 RTD 的微分负阻特性,其无法利用已有的器件和软件进行直接仿真(除美国密歇根大学等实验室拥有自行研发的 RTD-SPICE 软件外).本文主要采用文献[13]中提出的 RTD 的 MOS 网络电路模型,如图 3 所示.

该 MOS 网络能模拟单个 RTD 的 I-V 特性曲线,适合进行 RTD 电路的功能仿真,且易于通过现有的 SPICE 软件实现. MT1 和 MT2 管选择不同的沟道宽长比参数就可以得到不同的 RTD 电流峰值和谷值,因此只要选择合适的 MOS 管参数就可以得到所需的 I-V 特性曲线.本文仿真的 RTD 参数:  $V_{\rm P}$  约为 0.372 V,  $V_{\rm V}$  约为 0.561 V, 电流峰/谷比约为 10:1.

图 3 基于 MOS 网络的 RTD 电路模型 Fig. 3 Model of RTD based on MOS net

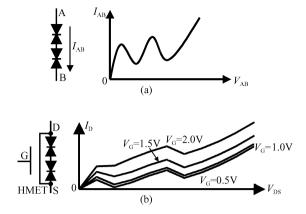

图 4 (a) 三值 RTD 的符号及 *I-V* 特性曲线;(b) 三值 RTD/HEMT 的符号及 *I-V* 特性曲线

Fig. 4 Symbol and *I-V* characteristic curves of ternary RTD (a) and ternary RTD/HMET (b)

#### 2.3 多值 RTD 与多值三端 RTT 器件

两个 N 峰值的 RTD 串联可以拥有 2N+1 个稳定的工作点<sup>[15]</sup>,因此,三值 RTD 由两个单峰值的 RTD 串联而成. 图 4(a) 为三值 RTD 的符号及 I-V 特性曲线. 三值 RTD 有三个正阻抗区和两个峰值 电流,且第二峰值电流大于第一峰值电流. 它有三个稳定的工作区. 图 4(b) 为三值 RTD/HEMT 符号及 I-V 特性曲线的模拟结果. (文中三值 RTD 仿真结果  $V_{P1}$ 到  $V_{V1}$ 分别为 0.364 和 0.572V,第一电流峰/谷比约为 10:1, $V_{P2}$ 到  $V_{V2}$ 分别为 1.456 和 1.676V,第二电流峰/谷比约为 4:1).

基于以上介绍的三值 RT 器件就可以方便快捷 地设计出三值逻辑单元电路.

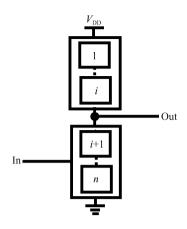

### 3 开关序列理论

开关序列设计方法<sup>[16]</sup>通过控制电路中 RT 器件的峰值电流,使 RT 器件按照特定的顺序进行翻转,也称为开关转换,以达到设计要求.根据此原理,作者设计了一个开关网络,该开关网络将 RT 电路划分为数个具有固定开启顺序的子电路,其电路模型可用图 5 来表示.它的工作过程如下:

当开关网络 $(i+1)\sim n$  翻转, $1\sim i$  导通时,输出电平最大;

当开关网络  $1 \sim i$  翻转, $(i+1) \sim n$  导通时,输出电平最小;

其余状态根据不同开关子网络的翻转和导通, 呈现不同的阻值对工作电源进行分压,从而输出不 同的电平.本文将基于该开关电路模型,设计出三值 与非和或非门电路.

图 5 基于 RT 器件的开关电路模型 Fig. 5 Model of switching RT circuits

### 4 三值 RT 门电路的设计

在三值逻辑电路中,有 0,1,2 三种状态,与二值逻辑电路相似,三值逻辑中也有与、或、非三种基本运算,其性质如下<sup>[17]</sup>:

与运算:

$$\begin{cases} 0 * x = 0 \\ 2 * x = x \\ x * x = x \end{cases}$$

(2)

或运算:

$$\begin{cases} 0 + x = x \\ 2 + x = 2 \\ x + x = x \end{cases}$$

(3)

式中变量 x 的取值为(0,1,2).

#### 4.1 二输入端三值 RT 与非门电路的设计

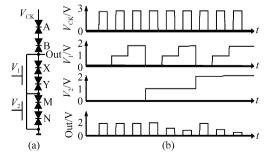

根据上节提出的开关电路模型,结合开关序列工作原理,可以设计出基于 RT 器件的二输入端三值与非门电路,如图 6(a)所示.它由两个三值 RTD/HEMT和一个三值 RTD 对串联而成,其中

图 6 三值与非门电路及仿真曲线 (a)三值与非门;(b) 仿真曲线

Fig. 6 Ternary NAND circuit (a) and its simulation curves (b)

图 7 三值门电路开关序列工作原理

Fig. 7 Theory of ternary logic circuit based on switching sequence

RTD 管作为负载,两个三值 RTD/HEMT 管作为驱动管.此电路是一个时钟上升沿有效电路.

图 6(b)为 SPICE 仿真曲线. 输入有(0,0),(0,1),(0,2),(1,0),(1,1),(1,2),(2,0),(2,1)和(2,2) 9种状态组合.

输入信号的取值范围: 低电平为 0V,中间电平为 1V,高电平为 2V. 输出高电平为 1.9V,中间电平为 0.8~1.2V,低电平为 0.3V. 工作电源  $V_{CK}$  为 3V. 由于输入为(1,1)和(2,1),(1,2)时翻转的管子不同,故输出的中间电平值略有不同.

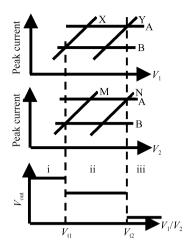

下面结合开关电路模型来分析与非门的设计原理,三值与非门的开关电路模型如图7所示.

图中阈值电压  $V_{11}=0.5$ V,  $V_{12}=1.5$ V. A 和 B 代表 RTD 的峰值电流, A 的峰值电流大于 B 的峰值电流(也即可假设 A 为三值 RTD 的第二峰值电流, B 为第一峰值电流); 其峰值电流是固定的值,表示为两条平行的横线. X 和 M, Y 和 N 代表 RTD/HEMT 的峰值电流, X 的值大于 Y, M 的值大于 N, 可以分别表示三值 RTD/HEMT 的第二峰值电流和第一峰值电流. 在图中用四条斜线表示,它们的值会随着输入电压  $V_1$  和  $V_2$  的变化而变化.

在 i 区,也即输入  $V_1$  和  $V_2$  都为低电平时,X 管和 Y 管、M 管和 N 管的峰值电流小于 A 管和 B 管,所以 A 管和 B 管导通,而 X,Y,M 和 N 管翻转产生大电阻,电路输出为高电平;

在 ii 区,也即输入  $V_1$  和  $V_2$  都为中间电平时, A 管、X 管和 M 管导通,B 管、Y 管和 N 管翻转,B, Y 和 N 3 只管子对工作电源分压,电路输出中间电平;

在 iii 区,也即输入  $V_1$  和  $V_2$  都为高电平时, X,Y,M 和 N 管的峰值电流大,此时 A 管和 B 管翻转,X,Y,M 和 N 管均导通,电路输出为低电平;

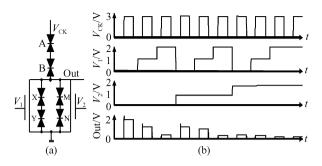

图 8 三值或非门电路(a)及模拟曲线(b)

Fig. 8 Ternary NOR circuit (a) and its simulation curves (b)

当输入电压  $V_1$  和  $V_2$  中一个为高电平而另一个为低电平时,两个 RTD/HEMT 中必有一个发生翻转,呈现较大的电阻,而 A 管和 B 管为导通状态,所以电路输出为高电平;

当输入电压  $V_1$  和  $V_2$  中一个为中间电平而另一个为低电平时,此状态和输入电压一个为高一个为低电平时相似;

当  $V_1$  和  $V_2$  中一个为高电平而另一个为中间电平时,输入为中间电平的 RTD/HEMT 管中一个RTD 管与 B 管同时翻转,而另一个 RTD/HEMT 管中的两个 RTD 均为导通状态,输出对工作电源分压,为中间电平.需要说明的是,此时的输出电平相对于两端输入均为中间电平状态时的输出略低,但它的值仍处于  $V_{11}$ 和  $V_{12}$ 之间,认为输出逻辑值为"1".

基于以上分析可见,在  $V_{\rm CK}$ 信号的上跳沿,只有当  $V_1$  和  $V_2$  都为高电平,图 6(a) 所示电路才输出低电平;只要输入  $V_1$  或  $V_2$  两者中有一个为低电平,电路就输出高电平;当输入  $V_1$  和  $V_2$  均为中间电平时,输出为中间电平;当输入  $V_1$  和  $V_2$  中一个为高电平一个为中间电平时,输出仍然为中间电平,因此该电路具有三值与非功能.

由于此电路的逻辑功能取决于各个管子的峰值 电流的大小,因此设置合适的峰值电流参数是设计 的关键. 只要在 RTD 的电路模型中选取合理的沟 道宽/长比参数满足上述要求,就能实现正确的逻辑 功能.

### 4.2 二输入端三值 RT 或非门电路的设计

二输入端三值或非门的设计原理与上文中与非门的设计原理相类似. 图 8(a) 为所设计的基于 RT 器件的二输入端三值或非门电路. 三值 RTD 管为负载管,并联的三值 RTD/HEMT 管为驱动管,各个管子的参数设置都与上文中的与非门相同. 图 8(b) 中模拟曲线输出高电平为 1.95V,中间电平为  $1.0\sim1.2V$ ,低电平为  $0.22\sim0.29V$ .

### 5 结论

本文实现了基于 RT 器件的三值与非门和或非门设计,所设计的电路结构简洁,且利用 SPICE 仿真验证了设计的正确性.三值逻辑中与、或、文字运算可以构成完备集,本文所设计的三值门电路结合已有的三值文字电路<sup>[18]</sup>和改进型的三值非门<sup>[19]</sup>便可以实现任意形式的三值逻辑函数,为三值量子电路的设计提供了基本单元.虽然本文设计的均为三值电路,但本文的设计思想可以应用到更高值逻辑电路的设计.

由于实验条件和设备的限制,现阶段的工作暂时只能停留在理论阶段,通过仿真的方式来设计RT电路.设计出的电路在性能参数上与实际的器件可能小有差距,文中门电路的工作速度约为20GHz,静态功耗小于4mW.后续的工作可以从器件结构和材料等方面考虑,对RT电路进行性能和功能上的改进.文中与非门和或非门的工作电源均为3V,如果实际应用中使用SOI或者锗硅异质结材料的RTD和RTD/HEMT,工作电源可以降低到1V左右,在实现低功耗应用方面能有进一步地突破.

#### 参考文献

- [1] He Xiaoting. Digital circuits. Hangzhou: Zhejiang University Press,2000(in Chinese)[何小艇. 数字电路. 杭州:浙江大学出版社,2000]

- [2] Chen Xiexiong, Shen Jizhong. Recent digital theory. Hangzhou. Zhejiang University Press, 2001 (in Chinese) [陈偕雄, 沈继忠. 近代数字理论. 杭州. 浙江大学出版社, 2001]

- [3] Mao Fayao, Ouyang Xingming, Ren Hongping. Digital logic. Wuhan: Huazhong University of Science Press, 1996 (in Chinese) [毛法尧, 欧阳星明,任宏萍. 数字逻辑. 武汉:华中理工大学出版社,1996]

- [4] Maezawa K. Resonant tunneling diodes and their application to high-speed circuits. CSIC '05 Compound Semiconductor Integrated Circuit Symposium, 2005:97

- [5] Li Ding, Mazumder P. A novel application of resonant tunneling device in high performance digital circuits. 2003 Third IEEE Conference on Nanotechnology, 2003, 2:520

- [6] Li Singrong, Mazumder P, Kyounghoon Y. On the functional failure and switching time analysis of the MOBILE circuit. 2005 IEEE International Symposium on Circuits and Systems, 2005, 3, 2531

- [7] Avedillo M J, Quitana J M, Pettenghi H. Self-latching operation of MOBILE circuits using series-connection of RTDs and transistors. IEEE Trans Circuits Syst, 2006, 53(5):334

- [8] Choi S, Lee B, Kim T, et al. CML-type monostable bistable logic element (MOBILE) using InP-based monolithic RTD/HBT technology. Electron Lett, 2004,40(13);792

- [9] Mazumder P, Kulkarni S, Bhattacharya M, et al. Digital circuit applications of resonant tunneling devices. Proceedings

- of the IEEE, 1998, 86(4):664

- [10] Sen S, Capasso F, Cho A, et al. Resonant tunneling device signal processing applications with reduced circuit complexity. IEEE Trans Electron Devices, 1987, 34:2185

- [11] Potter R C, Lakhani A, Hier H. Three and six logic states by the vertical integration of InAlAs/InGaAs resonant tunneling structures. Appl Phys. 1990. 64;3735

- [12] Lin H C. Resonant tunneling diodes for multi-valued digital applications. Proceedings of Twenty-Fourth International Symposium on Multiple-Valued Logic, 1994;188

- [13] Bhattacharya M, Kulkarni S, Gonzalez A, et al. A prototyping technique for large-scale RTD-CMOS circuits. Proceedings of IEEE International Symposium on Circuits and Systems, 2000, 1;635

- [14] Waho T, Chen K J, Yamamoto M. Resonant-tunneling diode and HEMT logic circuits with multiple thresholds and multilevel output. IEEE J Solid-State Circuits, 1998, 33:268

- [15] Wei S J, Lin H C. A multi-state memory using resonant tun-

- neling diode pair. IEEE International Sympoisum on Circuits and Systems, 1991, 5:2924

- [16] Waho T, Hattori K, Honda K. Novel resonant-tunneling multiple-threshold logic circuit based on switching sequence detection. Proceedings of 30th IEEE International Symposium on Multiple-Valued Logic, 2000;317

- [17] Wu Xunwei. The design theory of multiple logic circuits. Hangzhou: Hangzhou University Press, 1994 (in Chinese) [吴训威.多值逻辑电路设计原理. 杭州:杭州大学出版社, 1994]

- [18] Waho T, Chen K J, Yamamoto M. A literal gate using resonant-tunneling devices. Proceedings of 26th International Symposium on Multiple-Valued Logic, 1996:68

- [19] Lin Mi, Shen Jizhong, Wang Lin. Design of multiple-valued RTD inverters based on switching sequence. Journal of Zhejiang University (Science Edition), 2004, 31(1):38 (in Chinese)[林弥,沈继忠,王林. 基于开关序列的 RTD 多值反相器设计. 浙江大学学报理学版, 2004, 31(1):38]

## A Design for Triple-Valued NAND and NOR Gates Based on Resonant Tunneling Devices

Lin Mi<sup>1,2,†</sup>, Lü Weifeng<sup>1</sup>, and Sun Lingling<sup>1,2</sup>

(1 College of Electronic and Information, Hangzhou Dianzi University, Hangzhou 310018, China) (2 Department of Information Science and Electronic Engineering, Zhejiang University, Hangzhou 310027, China)

**Abstract:** The unique negative differential resistance characteristics lead the RT (resonant tunnel) devices to multiple-valued applications. In this paper, an RT switching circuit model is proposed, ternary NAND and NOR circuits are designed based on the switching sequence theory using RT devices, and they have correct logic certified by the SPICE simulation using MOS net model. This method can be used in other multiple-valued circuits design.

Key words: RT device; multiple-valued logic; switching sequence; NAND; NOR

**EEACC**: 1265**Z**

Article ID: 0253-4177(2007)12-1983-05