# 芯片的 EOS 失效分析及焊接工艺优化

吴顶和1 沈 萌1 邵雪峰2 俞宏坤1, \*\*

(1 复旦大学材料科学系,上海 200433) (2 飞兆半导体(苏州)有限公司,苏州 215021)

摘要:为了研究电过应力对功率 MOSFET 可靠性的影响,分别对含有焊料空洞、栅极开路和芯片裂纹缺陷的器件进行失效分析与可靠性研究.利用有限元分析、电路模拟及可靠性加速实验,确定了器件发生 EOS 失效的根本原因.并通过优化芯片焊接温度-时间曲线和利用开式感应负载测试方法,比较了工艺优化前、后器件抗 EOS 的能力,结果表明优化后器件的焊料空洞含量显著减少,抗 EOS 能力得到明显提高.

关键词: 电过应力; 失效分析; MOSFET; 芯片焊接; 工艺优化

PACC: 7850G; 7215C

中图分类号: TN306 文献标识码: A 文章编号: 0253-4177(2008)02-0381-06

## 1 引言

近 10 年来,随着集成电路的快速发展和自然资源的日渐匮乏,功率器件需求不断增大,功率器件在呈现快速发展趋势.功率器件是指可以控制高达 100A 的电流或是 1200V 的电压而不发生损伤和毁坏的半导体器件,同时还在向着大电流和高电压趋势发展[1]. 工作在大电流或高电压下的功率器件更加易于发生电过应力(electrical overstress)损伤而造成失效. EOS 是指所有的过度电性应力. 当电应力超过芯片最大极限后,器件功能将会减弱或损坏. 如何更好地提高功率器件可靠性与抗 EOS 能力,已经成为非常重要的问题<sup>[2,3]</sup>.

EOS 都是由芯片过热造成的,属于热应力失效.造成芯片过热的因素可形成于晶圆减薄、划片、贴片和器件封装、测试等工序及客户的不当使用[4].为确定芯片过热主要由哪些因素造成,进而优化这些参数使器件抗EOS 能力有所提高,这是对芯片乃至整个器件或模块都非常重要的问题,而迄今还缺乏详细的分析研究资料.本文利用目前被广泛应用的功率 MOSFET 为例,先分析了造成功率 MOSFET 发生 EOS 的因素,然后优化芯

片焊接温度-时间曲线,利用开式感应负载(unclamped inductive loading)测试比较了优化前、后器件抗 EOS 的能力,并进行了分析.

# 2 实验结果与讨论

### 2.1 焊料空洞(solder void)导致 EOS

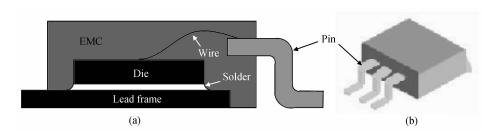

功率 MOSFET 的封装结构如图 1 所示.

已有文献报道,焊料空洞对器件的热耗散有显著影响,并分析了不同空洞尺寸对器件散热的影响<sup>[5]</sup>.本文在此基础上,进一步分析研究焊料空洞对器件芯片热应力及可靠性的影响.表1为组成器件材料的导热系数.

表 1 材料导热系数 Table 1 Thermal conductivity of material

| Material                          | Copper | Silicon | SiO <sub>2</sub> | Lead-free solder/<br>Ag adhesive epoxy | EMC  |

|-----------------------------------|--------|---------|------------------|----------------------------------------|------|

| Thermal conductivity /(W/(m • K)) | 383    | 124     | 14               | ~50                                    | 0.15 |

图 1 功率器件封装结构 (a)截面图;(b)轮廓图

Fig. 1 Packaging structure of power device (a) Cross-section; (b) Outline

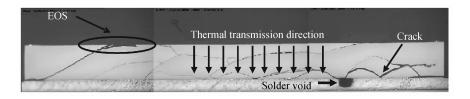

图 2 焊料空洞导致 EOS Fig. 2 EOS induced by solder void

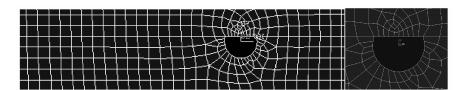

图 3 二维有限元网格划分

Fig. 3 2D FEA model and meshing detail

环氧塑封料(epoxy mold compound)的导热系数很低,是热的不良导体,器件在工作中产生的热主要是沿着芯片向下传递.如图 2 所示,图中箭头表示芯片在工作状态下产生热的传递方向.当器件生产过程中由于工艺原因在焊料内形成空洞时,由于空气的导热系数仅有 0.03W/(m • K),是热的不良导体,将会造成器件散热不良,经过长期的热循环后,热的积累使得器件发生EOS,导致器件致命的失效.

利用计算机有限元模拟计算对这一过程进行了分析.采用二维有限元模型结构,芯片横截面尺寸为3.5mm×0.25mm,根据分析需要对局部网格划分进行细化加密,具体网格划分如图3所示.

模型中组成器件的芯片、焊料以及铜焊盘散热片均假设为与温度无关的弹性材料,而且铜焊盘散热片正交各向异性,其他为各向同性材料.具体的材料参数如表2所示.

表 2 材料特性参数 Table 2 Material properties

|         | Elastic modulus/GPa     | Poisson's ratio | CTE/10 $^{-6}$ °C $^{-1}$  |

|---------|-------------------------|-----------------|----------------------------|

| Sn3.5Ag | 41(5℃)~<br>38(50℃)      | 0.33            | 21.85 + 0.02039            |

| Chip Si | 169                     | 0.23            | 2.49(20°C)∼<br>3.61(250°C) |

| Copper  | 103(30°C)∼<br>99(200°C) | 0.34            | 17.5                       |

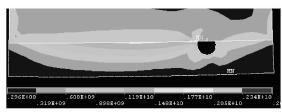

芯片导通后,热主要从芯片上部有源区向芯片底部传递.因此有限元模拟采用热加载方式模拟器件实际的芯片表面工作温度及热传递过程.器件芯片表面热加载设定为 100℃<sup>[6]</sup>,加载时间为 10min.所得结果如图 4 所示.

当热传递到芯片/焊料界面时,如果界面接触良好, 热将直接传到散热片(一般为铜板散热片)上,散热片将 热量散发出去,从而达到散热目的. 当焊料中有空洞存 在时,空气的热阻挡作用使得此区域的热传导性能下 降,无法散发出去的热将积累并聚集在此区域. 经过一 定周期的热循环之后,热集中将使此局部区域温度升 高. 空洞中气体的存在会在热循环过程中产生收缩和膨 胀的应力作用,空洞存在的地方便会成为应力集中点, 并成为产生应力裂纹的根本原因. 热集中又加剧了裂纹 的扩展并导致芯片短路,在大电流的冲击下最终导致芯 片发生 EOS.

比较图 2 和图 4,可以看到模拟结果与实际情况吻合得较好.在空洞与两种材料界面的交界处有很明显的应力集中,并有裂纹在此界面产生、扩展.有限元模拟结果显示了由于不同材料热膨胀系数的不匹配,在交界处会产生很大的应力.当芯片所受应力达到一定临界值时,裂纹开始产生.裂纹从空洞顶部与芯片的界面处孕育并向芯片内部扩展.由于热应力持续不断地增大,经过一段时间的扩展,裂纹朝芯片内部延伸,最终出现宏观裂纹并导致器件短路与 EOS 的发生.

图 4 功率 MOSFET 工作时的应力分布图

Fig. 4 Stress distribution of power MOSFET

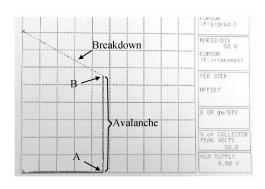

图 5 BV<sub>DSO</sub>的 I-V 曲线 Fig. 5 I-V curves of BV<sub>DSO</sub>

#### 2.2 栅极开路(gate open)导致 EOS

MOSFET 是一种电压控制型的场效应晶体管,它的控制栅压作用于绝缘层的沟道区,通过改变栅压大小来调制此区域的载流子浓度,从而达到控制源漏间的电流大小.在栅极引线因打线(wire bonding)不牢而升离(bonding lift)或是由于引线跟部裂纹(heel crack)经过一定周期的热循环而裂断之后,栅极开路,栅极控制电流的作用消失.

为了研究栅极开路导致 EOS,利用 Curve Tracer 370B 对 BV<sub>DSO</sub>击穿过程进行模拟,如图 5 所示.

首先测试样品的电特性,确认器件栅极开路、源级与漏极接触良好;再在源级与漏极间施加电压并不断增大,直到出现雪崩现象(图 5 中 A 点);继续增大电压,到某一临界点(图 5 中 B 点),器件发生击穿、短路.图中虚线表示器件发生击穿瞬间,器件从雪崩向短路过渡.实验结果表明,当器件栅极开路,电路中的瞬间过电压即瞬时的 $V_{\rm ds}>$ BV $_{\rm DSO}$ 即可击穿芯片,造成器件永久性失效.

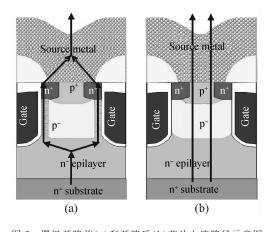

与正常器件相比,栅极开路导致无法在栅极施加偏压并形成沟道,芯片电流的流动路径发生了变化.栅极开路前、后芯片电流流动路径对比如图 6 所示.

对于正常器件,当在栅极施加偏压后,电子将会被吸引到栅极,同时在栅周围形成一条沟道,从而使得电流经过沟道从漏极流向源极.与正常器件不同,栅极引线升离意味着无法在栅极施加偏压,电流将直接从体二

图 6 栅极开路前(a)和开路后(b)芯片电流路径示意图 Fig.6 Current path in die before (a) and after (b) gate open

极管(body diode)流过.

反向击穿电压  $BV_{DSO}$  是漏极-源极击穿电压,描述的是当栅极开路时,加在漏极和源极间的最大允许电压.打线不牢或是引线材料不佳的器件经过一定使用周期后,材料的热胀冷缩与热应力疲劳导致在栅极的薄弱环节出现裂纹,即引线与引脚接触界面开裂和引线跟部裂纹的出现,并最终造成栅极开路.在异常情况下,器件外部有电感应突然加到器件里,或者在器件运行中的测试、操作等原因引起电路系统内部电磁能量的振荡、积聚和传播,造成电路中出现过电压现象.过电压现象一般持续时间很短(一般从几微秒至几十毫秒),但电压升高的总能很大,当  $V_{ds} > BV_{DSO}$ ,器件就会被击穿.

#### 2.3 芯片裂纹(die crack)导致 EOS

单晶硅具有金刚石晶格,晶体硬而脆.硅片在受力 情况下易于开裂与脆断. 硅芯片裂纹可形成于晶圆减薄 (wafer backside grinding)、晶圆测试(wafer test)、圆 片划片(die sawing)、芯片焊接(die attach)、引线键合 (wire bonding)等过程. 如果芯片微裂纹没有扩展到引 线区域则不易被发现,更为严重的是一般在工艺过程中 无法观察到芯片裂纹,甚至在芯片电学测试过程中,含 有微裂纹芯片的电特性与无微裂纹芯片的电特性几乎 相同,但微裂纹会影响封装后器件的可靠性和寿命.而 芯片裂纹也只有经过可靠性高低温循环实验(temperature cycle test)或者器件热耗散时的瞬时加热,由芯片 和封装材料热膨胀系数(CTE)不匹配或者在使用中受 外界应力作用,最终才会显现出来.例如:穿过结的裂纹 可能导致短路或者漏电并最终导致 EOS 的发生. 最为 致命的是裂纹引起的这些效应只有当有热或者电流通 过时才会显现,而标准的电学测试则根本无法检测到这 些失效.即只有发生失效后,裂纹的存在与状态才可被 验证[7~10].

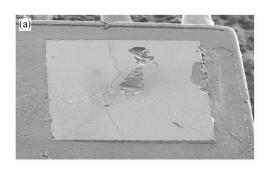

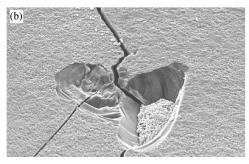

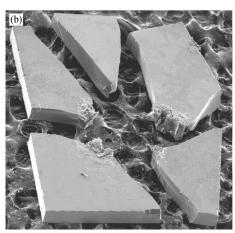

为证实芯片裂纹在发生 EOS 之前已存在于芯片内部而进行了高低温循环实验. 采用 JEDEC 标准对同批次的 77 个试样进行 200 周期的高低温循环实验(-50~150°C),每一周期的高低温各为 30min. 实验结束后随机抽取 5 个样品进行背面开封和焊料腐蚀,在扫描电镜(SEM)下观察到芯片背面有不同形貌的裂纹存在,如图 7 所示.

从图 7(b)中可以清晰地看到裂纹源及裂纹扩展路径.为排除芯片裂纹可能形成于高低温循环实验过程中的影响,在设计实验时选取同种型号不同生产批次的77 个器件进行高低温循环实验.实验结束后随机抽取5个样品用 SEM 观察芯片背面形貌,发现芯片背面状态完好,没有裂纹出现.由此可以推知,有裂纹源存在于芯片内部的器件,裂纹经过高低温循环实验的冲击后最终会显现出来;而芯片内部没有裂纹源的器件,在短周期的高低温循环实验中没有裂纹出现.

用已证实有芯片裂纹源的同一生产批次的 77 个器件进行 1000 个周期的功率循环实验 (power cycle test),实验加载电流为 0.75A,电压为 5V,每个周期开

图 7 高低温循环后芯片背面整体形貌(a) 和裂纹源区域局部放大图(b) Fig. 7 Global morphology of backside (a) and close-up view of crack source area (b) after temperature cycle test

启时间为 35s,关断时间为 140s.实验结束后随机抽取 5 个样品进行化学开封,发现有 EOS 发生,如图 8 所示.

图 8 功率循环实验后芯片正面整体形貌(a)和背面的 SEM 图(b) Fig. 8 Global morphology of front-side (a) and SEM image of backside (b) after power cycle test

裂纹导致芯片发生 EOS 失效的机理与热应力引发的芯片裂纹扩展有关. 当负载循环过程中温度变化时,由于结构中各种材料的热膨胀系数不匹配而产生热应力,使芯片内的裂纹不断扩展,导致脆性的硅芯片破裂.芯片裂纹致使短路发生,并最终导致 EOS 的发生.

综合分析以上两个可靠性加速实验,高低温循环实验验证了含有裂纹源的芯片经过一定周期的高低温循环实验后,在应力作用下芯片微裂纹不断扩展并最终显现出来;在功率循环实验中,芯片微裂纹不断扩展并造成芯片内部形成短路,最终导致 EOS 的发生.

#### 2.4 芯片焊接工艺优化

在器件的生产过程中,芯片焊接是封装过程中的重 点控制工序.此工艺的目的是将芯片通过融化的合金焊 料粘结在引线框架上,使芯片的集电极与引线框架的散 热片形成良好的欧姆接触和散热通路.由于固体表面的 复杂性和粘结剂的不同特性,目前存在的吸附理论、静 电理论、扩散理论、机械理论、化学键理论和配位键理 论,都不能单一地解释各种表面与粘接剂的粘接机理. 任何一个固体表面都会吸附气体、油污、尘埃等污物,还 会与空气中的氧起作用形成氧化膜使表面不清洁.由于 加工精度的影响,固体表面存在微观和宏观的表面几何 形状误差,粘接界面只有理论值的极少一部分,两固体 表面的实际接触面积仅占总几何面积的 2%~7%[11], 因而严重影响粘接剂对固体表面的润湿作用. 因此在芯 片焊接过程中,常常会在焊料中发现有空洞存在,这严 重地影响了器件的欧姆接触和散热,对器件的可靠性产 生不利影响.

芯片焊接的过程是先在引线框架上涂上焊膏,然后在框架上附着芯片,最后是高温的焊接过程.根据粘片剂与器件类型的不同,焊接的温度-时间曲线也有所不同.本实验所使用的样品是采用无铅焊料(SnAgCu)作为粘片剂的功率 MOSFET 器件.

在芯片焊接工艺优化前,经 X 射线扫描得知器件的焊料空洞约为芯片面积的 1%~7%.按照产品规范,器件焊料空洞面积小于芯片面积的 10%即为合格产品.但在实际应用过程中发现,即使含有少量空洞的器件仍然存在可靠性隐患.本实验通过优化芯片焊接温度-时间曲线,减少焊料空洞含量,从而提高器件的可靠性与延长器件使用寿命.

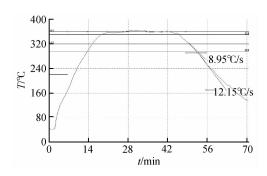

工艺优化前,实验样品所采用的芯片焊接温度-时间曲线的最高温度、熔融时间和焊后降温速率分别为360.9 $^{\circ}$ ,37min 和 9.82 $^{\circ}$ /s.工艺优化后,芯片焊接温度-时间曲线的最高温度、熔融时间和焊后降温速率分别为363.3 $^{\circ}$ ,38min 和 8.95 $^{\circ}$ /s,如图 9 所示.

与芯片焊接工艺优化前相比,优化后的焊接温度-时间曲线有3大变化:最高温度提高、熔融时间延长及 焊后降温速率降低.提高温度,可增加芯片下焊膏的流 动性,有利于焊膏内空气排出芯片焊接区域;延长熔融 时间,有利于焊膏内空气的完全排出;降低焊后降温速 率,有利于保护芯片,减少芯片产生微裂纹的可能性.

图 9 优化后芯片的焊接温度-时间曲线

Fig. 9 Temperature-time curve of die attach after optimization

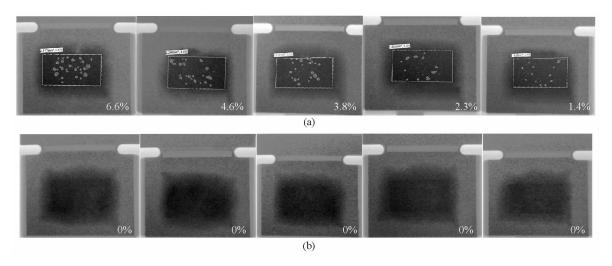

分别随机抽取采用优化前、后焊接曲线进行芯片焊接的样品各 5 片,利用 X-ray 测量器件焊料空洞含量并进行比较,如图 10 所示.

图 10(a)中的方框表示芯片面积,是为了排除此区域以外的空洞影响,百分比是空洞在芯片区域所占面积的比例;(b)图中所有器件的引线框架区域均无空洞存在,因此未进行芯片面积选取.由图 10 得知,在工艺优化前器件焊料的空洞含量在 1.4%~6.6%之间(根据设备误差,误差范围为 ± 0.1%).采用优化前的焊接曲线进行芯片焊接,器件含有含量不一的空洞,有的空

洞含量甚至已经接近规范的最大允许值(10%).而采用 优化后的焊接曲线进行芯片焊接的器件无一包含有焊 料空洞,优化效果非常明显.

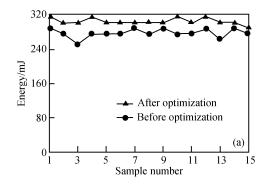

同时对优化前、后的样品进行(unclamped inductive loading 测试,UIL),UIL 是考察器件抗 EOS 能力的参数.它的测试原理是,对器件施加栅压使电路导通后,外部电源对电感器充电,直到电感器的电流达到预期测试数值,这是电感器的充电阶段;随后关断器件栅压,电感器对器件反向放电,这是电感器的放电阶段<sup>[12]</sup>.电感器对器件反向放电,使器件进入雪崩状态,从而可以考察器件抗 EOS 的能力.

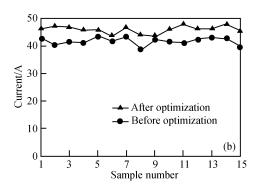

分别从工艺优化前、后的两组样品中各随机抽取 15 个样品进行 UIL 测试,测试条件为:  $V_{DD}$  = 23V,  $V_{GS}$  = 10V, L = 0.3mH. 对它们发生 EOS 时的能量与电流进行比较, 如图 11 所示.

结果表明,含有焊料空洞的器件发生 EOS 时的能量与电流的平均值分别为 279.3 mJ 和 41.8 A,而无焊料空洞的器件发生 EOS 时的能量与电流的平均值分别为 307.6 mJ 和 46.1 A.由此可知无焊料空洞的器件需要更高的能量与更大的电流才会发生 EOS 失效,因此无焊料空洞器件的抗 EOS 能力高于含有焊料空洞的器件.

图 10 芯片焊接工艺优化前(a)和优化后(b)器件的焊料空洞含量

Fig. 10 Volume of solder void of device before (a) and after (b) die attach process optimization

图 11 优化前、后器件抗 EOS 能力对比 (a)能量;(b)电流

Fig. 11 EOS resistance contrast before and after optimization (a) Energy; (b) Current

# 3 结论

通过对功率 MOSFET 芯片 EOS 失效分析与焊接工艺优化的研究,根据实验结果得出以下结论:

(1)导致器件发生 EOS 失效的主要因素有:焊料空洞、栅极开路、芯片裂纹.焊料空洞会造成器件散热不良,热积累将导致器件发生 EOS;栅极开路造成栅压控制电流作用消失,当  $V_{ds}>BV_{DSO}$ 时器件被击穿;芯片裂纹造成芯片短路,在大电流的冲击下器件最终将发生 EOS.

(2)通过优化芯片焊接工艺,即提高芯片焊接最高温度,延长焊接熔融时间,降低焊后降温速率,可以显著地减少器件焊料空洞含量.同时,通过 UIL 测试得知,无焊料空洞器件的抗 EOS 能力明显高于含有焊料空洞的器件.

本论文优化的功率 MOSFET 芯片焊接温度-时间 曲线已成功应用于有关企业的生产部门,为功率 MOSFET 产品质量和可靠性的提高做出贡献.

#### 参考文献

- Desbiens D. Trends in power semiconductor packaging. Proceedings of the 6th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Micro-Electronics and Micro-Systems, 2005; 6

- [2] Huang C Y. Simulation prediction of electrothermal behaviors of ESD N/PMOS devices. Solid-State Electron, 2005, 49:1925

- [3] Eveloy V, Hwang Y C, Pecht M G. The effect of electrostatic discharge on electrical overstress susceptibility in a gallium arsenide

- MESFET-based device. IEEE Trans Device Mater Reliab, 2007, 7,200

- [4] Kuzm J, Pogany D, Gornik E. Electrical overstress in AlGaN/GaN HEMTs: study of degradation processes. Solid-State Electron, 2004.48:271

- [5] Chang J, Wang L, Dirk J. Finite element modeling predicts the effects of voids on thermal shock reliability and thermal resistance of power device. Welding Journal, 2006, 85(3):63

- [6] Ishiko M, Usui M, Ohuchi T, et al. Design concept for wire-bonding reliability optimization by optimizing position in power devices. Microelectronics Journal, 2006, 37:263

- [7] Irving S, Liu Y, Almagro E I V, et al. An effective method for improving IC package die failure during assembly punch processing. Proceedings of the 6th International Conference on Thermal, Mechanical and Multi-Physics Simulation and Experiments in Micro-Electronics and Micro-Systems, 2005;227

- [8] Xue Ming, Frankie L. A quantitative study of die crack in leaded IC package. Electronics Packaging Technology Conference, 2006: 733

- [9] Ni Jinfeng, Wang Jiaji. Fracture of thin silicon die used in IC car. Semiconductor Technology, 2004, 4(4):40(in Chinese) [倪錦峰, 王家楫. IC 卡中薄芯片碎裂失效机理的研究. 半导体技术, 2004, 4(4), 40]

- [10] Gu Jing, Wang Jun, Lu Zhen. Failure analysis and thermal stress simulation in a stacked die package. Chinese Journal of Semiconductors, 2005, 26(6):1275(in Chinese)[顾靖,王珺,陆震.芯片叠层封装的失效分析和热应力模拟.半导体学报, 2005, 26(6):1275]

- [11] Gu Jiyou. Adhesion theory and basic. Beijing: Science Press, 2003: 2 (in Chinese) [顾继友. 胶接理论与胶接基础. 北京: 科学出版社, 2003:2]

- [12] Shen C C, Kefner A R Jr, Berning D W, et al. Failure dynamics of the IGBT during turn-off for unclamped inductive loading conditions. IEEE Transactions on Industry Applications, 2000, 36(2): 64

## **EOS Failure Analysis and Die Attach Optimization**

Wu Dinghe<sup>1</sup>, Shen Meng<sup>1</sup>, Shao Xuefeng<sup>2</sup>, and Yu Hongkun<sup>1,†</sup>

(1 Department of Material Science, Fudan University, Shanghai 200433, China) (2 Fairchild Semiconductor (Suzhou) Co., Suzhou 215021, China)

Abstract: To investigate the influence of electrical overstress (EOS) on the reliability of power MOSFETs, failure analysis is employed to assess the reliability of devices, including defects related to solder void, gate openings, and die cracks. After using finite element analysis, a circuit simulation, and a reliability accelerated test, the root cause of EOS is confirmed. EOS resistance of the devices after optimizing the die attach temperature-time curve is compared with that of the devices before the optimization using unclamped inductive loading test. The volume of solder void is observably decreased and EOS resistance is improved after optimization.

**Key words:** EOS; failure analysis; MOSFET; die attach; process optimization **PACC:** 7850G; 7215C

Article ID: 0253-4177(2008)02-0381-06

<sup>†</sup> Corresponding author. Email; hkyu@fudan. edu. cn Received 23 July 2007, revised manuscript received 11 September 2007