# OTFT with Bilayer Gate Insulator and Modificative Electrode\*

Bai Yu<sup>1,†</sup>, Khizar-ul-Haq<sup>1</sup>, M. A. Khan<sup>1</sup>, Jiang Xueyin<sup>1,2</sup>, and Zhang Zhilin<sup>1,2</sup>

(1 Department of Materials Science, Shanghai University, Jiading Campus, Shanghai 201800, China) (2 Key Laboratory of Advanced Display and System Application, Ministry of Education, Shanghai University, Shanghai 200072, China)

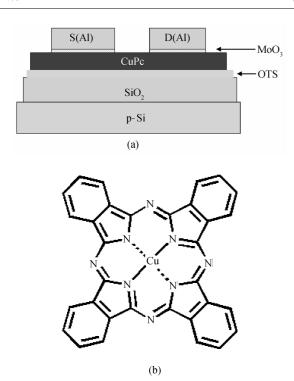

**Abstract:** An organic thin-film transistor (OTFT) with an OTS/SiO<sub>2</sub> bilayer gate insulator and a MoO<sub>3</sub>/Al electrode configuration between gate insulator and source/drain electrodes has been investigated. A thermally grown SiO<sub>2</sub> layer is used as the OTFT gate dielectric and copper phthalocyanine(CuPc) is used as an active layer. This OTS/SiO<sub>2</sub> bilayer gate insulator configuration increases the field-effect mobility, reduces the threshold voltage, and improves the on/off ratio simultaneously. The device with a MoO<sub>3</sub>/Al electrode has shown similar  $I_{ds}$  compared to the device with an Au electrode at the same gate voltage. Our results indicate that using a double-layer of electrodes and a double-layer of insulators is an effective way to improve OTFT performance.

Key words: organic thin film transistor; modified electrode; bilayer insulator; mobility

**EEACC**: 2560

**CLC number:** TN386. 2 **Document code:** A **Article ID:** 0253-4177(2008)04-0650-05

#### 1 Introduction

Organic field-effect transistors (OFETs) based on semiconductive materials have attracted increasing interest for their promising application to flexible, low cost, and large area displays, and electronic devices like smart cards due to the extraordinary electrical and mechanical properties of the small molecules<sup>[1~3]</sup>. Since the interface between the organic active material and the gate dielectric material is a critical part of the field-effect device, control over this interface is of great importance. Therefore, many methods of modifying the inorganic/organic interface have been explored to improve the growth of ordered vapor deposited films. We found that the characteristics of CuPc TFTs can be improved by using a self-organizing material like octadecyltrichlorosilane(OTS) between the SiO<sub>2</sub> gate dielectric and the CuPc active layer<sup>[4]</sup>.

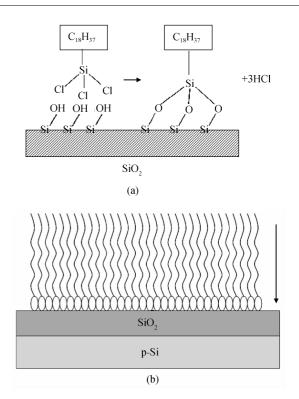

The silane coupling agent OTS is a particularly interesting material because it can bond to silicon oxide surfaces and form a Si—O—Si bond, which can influence deeply the characteristics of insulator films. In this paper, a solution technique was used to form OTS monolayers. High-quality OTS monolayers can also be spontaneously formed in solution through a simple chemical reaction. Then, we investigated the effect of OTS self-assembled monolayers (SAMs) on the characteristics of evaporated CuPc thin films<sup>[5~7]</sup>, and ob-

served that OTS SAMs not only depress the surface roughness of SiO<sub>2</sub> film but also decrease leakage current. Finally, we found that this method improved the organic/inorganic interface significantly and enhanced the performance of a CuPc organic thin film transistor.

Since the organic FETs are generally used for low-cost applications, the easy fabrication processes and the simplified structures are of great interest. In most of the literature, Au is used in the device as the electrode material because of its high work function, which can match that of many organic active materials. However Au is also a high price metal, which increases the cost of the device. If we can find a suitable cheaper alternative material and reduce the cost of manufacturing, then the work is of great significance. Although aluminum (Al) is a well-known contact material in integrated circuits, its low-work function precludes the application of Al to high performance OT-FT for p-type semiconductors. In addition, high performance OTFTs can be achieved by inserting a transition metal oxide layer between Al electrodes and organic semiconductors. Following Chu et al. [8], we select MoO<sub>3</sub> as a modified layer of electrodes.

In this paper, we present the fabrication procedure and electrical characteristics of a FET using  $OTS/SiO_2$  with the bilayer gate insulators modifying method and  $MoO_3/Al$  for the device modificative electrodes.

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (Nos. 90202034,60477014,60577041) and the State Key Development Program for Basic Research of China (No. 2002CB613400)

<sup>†</sup> Corresponding author. Email: by72@shu.edu.cn

Fig. 1 (a) Schematic structure of the OTFTs; (b) Chemical structure of CuPc

## 2 Experiment

The OTFT device structure used in this study is shown in Fig. 1 (a). For simplicity, our devices were fabricated using a heavily doped silicon wafer as the substrate and gate electrode, with thermally grown silicon dioxide as the TFT gate dielectric. First, a 230nm thick thermal SiO<sub>2</sub> layer was grown as the OTFT gate dielectric (SiO<sub>2</sub> thickness was measured by ST2000-DLXn, Apectra Thick STD-Auto). The SiO<sub>2</sub> surface was ultrasonically cleaned with acetone, ethanol, and deionized water in that order, and subsequently the wafer was treated by UV for ten minutes. Then, the SiO<sub>2</sub> surface was treated with OTS by immersing the sample into a 0.5% solution of OTS (CH<sub>3</sub>Cl: C<sub>6</sub>H<sub>12</sub> = 1 : 3) for 12 hours at room temperature in an anhydrous ambient. This chemical process is described in Fig. 2(a), which allows a monolayer of OTS to self-assemble on the surface of the SiO2 and form an LB monolayer (the schematic structure is shown in Fig. 2 (b)). The UV activates the Si-OH bond and makes the reaction occur more easily. A 40nm thick CuPc thin film (the chemical structure is shown in Fig. 1 (b)) was then deposited by vacuum deposition at a rate of 2nm/min under a pressure of  $6 \times 10^{-4}$  Pa. It was purified twice using vacuum successive sublimation. Finally, the devices were completed by depositing Au or MoO<sub>3</sub>/Al bilayer source and drain electrodes through a shadow mask (the thickness of the MoO<sub>3</sub> is 10nm). The electrodes were patterned to be

Fig. 2 (a) Chemical process between OTS and surface of  $SiO_2$ ; (b) LB membrane schematic structure of OTS on surface of  $SiO_2$

$35\mu m$  in length and  $2000\mu m$  in width.

The current-voltage characteristics of devices were measured by home-made transistor detection equipment. The measuring voltage (YJ32-2 Model) and accuracy of the micro-ammeter (HP-4140B Model) used in our experiments can reach  $\pm~100\,\mathrm{V}$  and  $10^{-12}\,\mathrm{A}$ , respectively. All experiments were carried out under dark conditions in ambient at room temperature.

### 3 Results and discussion

The *I-V* curves of OTFT have two working regions; the linear region and the saturated region. In this paper, the field-effect mobility is estimated in the saturation region using the equation:

$$I_{\rm DS} = (W/2L) \mu C_{\rm i} (V_{\rm G} - V_{\rm T})^2$$

where W and L are the channel width and length, respectively,  $\mu$  is the carrier mobility of the holes in the OTFT channel,  $C_i$  is the gate dielectric capacitance per unit area, and  $V_{\rm G}$ ,  $V_{\rm DS}$ ,  $V_{\rm T}$  are the gate voltage, drain-source voltage, and threshold voltage, respectively.

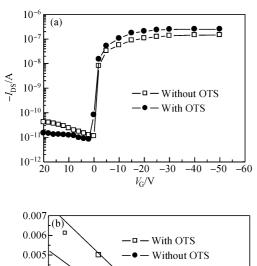

Figures 3 (a) and (b) shows the I-V characteristics for a CuPc OTFT fabricated on untreated and OTS-treated oxidized silicon substrates held at room temperature. Clearly, a significant increase in current is observed in devices biased with the same  $V_{\rm G}$  and  $V_{\rm DS}$ . The plots in Fig. 4(a) show the characteristics of

Fig. 3 (a) Current-voltage characteristics of an OTFT device without an OTS layer; (b) Current-voltage characteristics of an OTFT device with an OTS layer

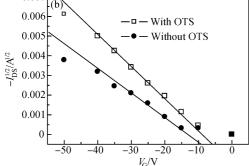

$\lg I_{\rm DS}$  versus  $V_{\rm G}$  at a fixed  $V_{\rm DS}$  of  $-40{\rm V}$  for the devices. Figure 4(b) shows the square root of the drain current  $I_{\rm DS}^{1/2}$  versus gate voltage  $V_{\rm G}$  curve at a fixed

Fig. 4 (a)  $I_{\rm DS}$  versus  $V_{\rm G}$  at a fixed  $V_{\rm DS}$  of  $-40\rm V$  for OTFT device; (b)  $I_{\rm DS}^{1/2}$  versus  $V_{\rm G}$  at a fixed  $V_{\rm DS}$  of  $-40\rm V$  for OTFT device

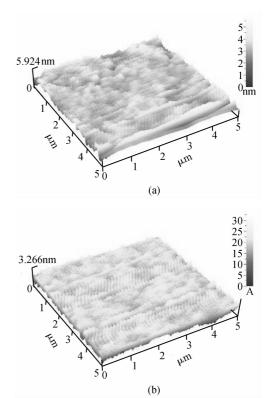

Fig. 5 (a) AFM image of a  $5\mu m$  square of untreated SiO $_2$  surface; (b) AFM image of a  $5\mu m$  square of OTS-treated SiO $_2$  surface

drainsource voltage  $V_{\rm DS}$  of  $-40{\rm V}$ . From these four figures, we can conclude that OTFTs on untreated gate dielectrics have a field-effect mobility of  $6\times10^{-4}$  cm²/(V • s), an on/off current ratio of about  $10^3$ , and a threshold voltage of  $-9{\rm V}$ . Meanwhile, OTFTs fabricated with OTS-treated gate dielectrics have a field-effect mobility as high as  $1.5\times10^{-3}$  cm²/(V • s), an on/off current ratio of more than  $10^4$ , and a threshold voltage of  $-6{\rm V}$ . The above-mentioned results suggest that treating the SiO<sub>2</sub> surface prior to the CuPc active layer deposition with an OTS monolayer has been shown to improve noticeably the electrical characteristics of CuPc TFT.

The surface roughness of the insulator is critical to the OTFT device's performance because the regular morphology of thin film is important for the transport of carriers in the film. In our tests, the surface of the OTS-treated SiO<sub>2</sub> insulator was characterized with atomic force microscopy (AFM). Tappingmode AFM was used to characterize the surface roughness and to image the surface effect, such as pinholes and defects. Figures 5(a) and (b) show that the OTS-treated SiO<sub>2</sub> layer is flatter than the bare SiO<sub>2</sub> layer and also show a considerable difference in surface roughness. Thus, the OTS shows an improved surface modified result.

For OTS-treated TFTs, another reason for the large improvement in OTFT performance using an

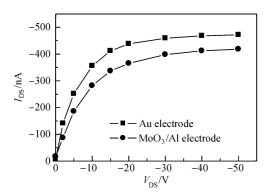

Fig. 6 Current-voltage characteristics of an OTFT device with Au and  $MoO_3/Al$  electrodes

OTS-treated SiO<sub>2</sub> gate dielectric is the altered film growth at the gate dielectric interface and adhesion of CuPc to the substrate. The OTS SAMs change the surface properties of the thermal oxide SiO<sub>2</sub> to a more hydrophobic surface with a low surface energy<sup>[9]</sup>. Secondly, the OTS SAMs perpendicular to the SiO<sub>2</sub> substrate would cause a preferential out-of-plane orientation of the evaporated CuPc molecules in an initial layer at the interface, which effectively improve the  $\pi^-\pi$  stacking in the direction of current flow and lead to higher mobility. Therefore, the characteristics of CuPc organic TFTs can be improved with a silicon dioxide gate dielectric chemically modified with OTS monolayers. Importantly, the interface trap of organic film and inorganic insulator proved to be a limiting factor in OTFT performance. The results presented in this paper show clearly that the use of monolayers self-assembled at the interface is indeed a good method for improving the performance of the devices.

Field effect transistors require an ohmic source contact and an ohmic drain contact for ideal operation. In many real situations, the injection of charge carriers from metals into semiconductors can be an inefficient process, that is, non-ohmic, for example, Al to many of organic active materials such as CuPc, pentacene. This has an adverse impact on the performance of thin film transistors and makes the mobility of electrical measurements very poor because contact effects need to be disentangled from transistor properties. In this paper, to resolve this question, we adopt a vaporing thin MoO<sub>3</sub> film to modify the Al electrode layer and form double-layer electrodes. Figure 6 shows the current-voltage characteristics of OTFTs and MoO<sub>3</sub> covered with Al metal as the electrode. The source-drain current  $I_{\mathrm{DS}}$  versus  $V_{\mathrm{DS}}$  of the OTFT at the same  $V_G$  display very clear saturation currents as a function of the gate bias voltage and also show similar characteristics and performance compared to the Au electrode.

The introduction of the metal oxide MoO3 in our

OTFTs played an important role in decreasing the contact resistance. The measurement of work function based on the method of contact potential difference reported by our team showed that the work function of  $MoO_3$  was 5. 4eV, which is near that of CuPc (5. 3eV). The small hole injection barrier from  $MoO_3$  to CuPc resulted in strong hole injection. In addition,  $MoO_3$  has a lower melting point and the ability of preventing Al metal diffusion into the organic material. These results demonstrate that the device with  $MoO_3/Al$  electrodes has a similar  $I_{ds}$  to the device with Au electrodes at the same gate voltage. Thus, using a transition metal oxide as the hole injection layer is an effective way to improve the characteristics of OTFTs.

#### 4 Conclusion

We have fabricated bilayer gate dielectic organic TFTs with improved electrical characteristics, including a field-effect mobility as high as  $1.5 \times 10^{-3}$  cm<sup>2</sup>/(V·s), an on/off current ratio of more than  $10^4$ , and a threshold voltage of -6V. This OTS/SiO<sub>2</sub> bilayer gate insulator configuration increases the field-effect mobility, reduces the threshold voltage, and improves the on/off ratio at the same time. The device with MoO<sub>3</sub>/Al electrodes has a similar  $I_{DS}$  to the device with Au electrodes at the same gate voltage. MoO<sub>3</sub>/Al has been proven to be a superior electrode.

These results further increase the likelihood that organic thin film transistors will find use in low-cost electronic applications.

Acknowledgments The generous supply of surface atomic force microscope (AFM) tests by the Department of Electrical Engineering of National Cheng Kung University is gratefully acknowledged.

### References

- [1] Gundlach DJ, Lin YY, Jackson TN, et al. Pentacene organic thin film transistors-molecular ordering and mobility. IEEE Electron Device Lett, 1997, 18(3);87

- [2] Zhang Jidong, Wang Jun, Wang Haibo, et al. Organic thin-film transistors in sandwich configuration. Appl Phys Lett, 2004, 84:

- [3] Yuan Jianfeng, Zhang Jidong, Wang Jun, et al. Bottom-contact organic field-effect transistors having low-dielectric layer under source and drain electrodes. Appl Phys Lett, 2003, 82:3967

- [4] Lin Yenyi, Gundlach D J, Nelson S F, et al. Pentacene-based organic thin-film transistors. IEEE Trans Electron Devices, 1997, 44 (8):1325

- [5] Pernstich K P, Goldmann C, Krellner C, et al. Shifted transfer characteristics of organic thin film and single crystal FETs. Synthetic Metals, 2004, 146(3):32

- [6] Gundlach D J, Jia L L, Jackson T N. Pentacene TFT with im-

- proved linear region characteristes using chemically modified source and drain electrodes. IEEE Electron Device Lett, 2001, 22 (12):571

- [7] Lin Y Y, Gundlach D J, Nelson S F, et al. Stacked pentacene layer organic thin-film transistors with improved characteristics. IEEE Electron Device Lett, 1997, 18(12):606

- [8] Chu C W. Li S H, Chen C W, et al. High-performance organic thin-film transistors with metal oxide/metal bilayer electrode.

Appl Phys Lett, 2005, 87:193508

- [9] Xiao K, Liu Y, Guo Y, et al. Influence of self-assembly monolayers on the characteristics of copper phthalacyanine thin film transistor. Appl Phys A, 2003, 80(7):1541

## 具有双绝缘层和修饰电极的薄膜场效应晶体管\*

白 钰1, 中 克1 鲁富翰1 蒋雪茵1,2 张志林1,2

(1上海大学材料学院,上海 201800) (2上海大学新型显示教育部重点实验室,上海 200072)

摘要:研究了具有 OTS/SiO<sub>2</sub> 双绝缘层结构及  $MoO_3$ /Al 电极结构的有机薄膜晶体管.器件是以热生长的 SiO<sub>2</sub> 作为有机薄膜晶体管的栅绝缘层,酞菁铜作为有源层的.OTS/SiO<sub>2</sub> 双绝缘层的结构提高了器件的场效应迁移率和开关电流比,降低了阈值电压.实验表明在同样的栅极电压下,具有  $MoO_3$ /Al 电极的器件和金电极的器件有着相似的源漏输出电流.结果显示具有  $OTS/SiO_2$  双绝缘层及  $MoO_3$ /Al 电极结构的器件能有效改进有机薄膜晶体管的性能.

关键词:有机薄膜晶体管;修饰电极;双绝缘层;迁移率

**EEACC:** 2560

中图分类号: TN386.2 文献标识码: A 文章编号: 0253-4177(2008)04-0650-05

<sup>\*</sup> 国家自然科学基金(批准号:90202034,60477014,60577041)和国家重点基础研究发展规划(批准号:2002CB613400)资助项目

<sup>†</sup>通信作者.Email:by72@shu.edu.cn 2007-09-26 收到,2007-12-04 定稿