# A Novel 4/5 Prescaler with Automatic Power Down\*

Zeng Longyue, Zhu Siqi, and Yan Yuepeng<sup>†</sup>

(Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China)

Abstract: An "automatic power down" method is introduced to design a 4/5 prescaler, with the characteristic of making one of its D-flip-flops power down when it operates in divide-by-4 mode. Implemented with the TSMC  $0.25\mu m$  mixed-signal CMOS process, the 4/5 MOS current mode logic prescaler is designed with this automatic power down technique. The simulation results show that the new 4/5 prescaler is immune to the "wake-up" issue and thereby retains the same maximum operating frequency as the conventional prescaler. An integer-N divider with this proposed prescaler and with the division ratio 66/67 is manufactured, and it is estimated to save more than 20% of the power compared with the conventional 4/5 prescaler.

Key words: MCML prescaler; automatic power down; frequency synthesizer

EEACC: 1265B; 2570D; 1230B

### 1 Introduction

In the design of an integer-N frequency synthesizer, a dual-modulus prescaler is required to provide two consecutive dividing ratios. This is a key component for integrated radio frequency transceiver design in terms of maximum operating frequency and power consumption[1]. Several CMOS high-speed dual-modulus prescalers, including true single phase clocking (TSPC) and MOS current mode logic (MCML) architecture have been reported<sup>[2~5]</sup>. Those reports pay much importance to improving the speed and power efficiency at the transistor circuit level; However, little attention was paid to optimizing the overall dualmodulus architecture. In this report, we present a method to reduce the MCML 4/5 prescaler's power consumption, with the characteristic of making one of its third D-flip-flop automatically power down when it operates in divide-by-4 mode. Simulation and measured results are reported to verify the expected performance.

### 2 General considerations

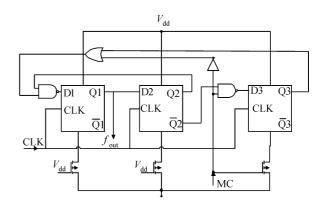

The dual-modulus prescaler is one of the most power-hungry components and may consume more than 40% of the power in the overall frequency synthesizer [6,7]. The conventional high-speed 4/5 prescaler is generally composed of three synchronous D-flipflops, as shown in Ref. [6]. Operation analysis reveals that when the modulus-control signal (MC) is at the

low level, the output frequency  $(f_{out})$  is determined by the loop over the first two D-flip-flops and equals one-fourth of the input frequency. At this operation mode, the third D-flip-flop has no contribution to the output frequency but it offers a high-level signal to the former NAND gate. This high-level signal can be provided by other components rather than a powerhungry D-flip-flop. In order to achieve this, a novel 4/ 5 prescaler topology with an added OR gate and an inverter is proposed, as shown in Fig. 1. In the new topology, when the MC is at the low level, the prescaler still operates in divide-by-4 mode, but the third Dflip-flop is powered down by an nMOS named N1 whose gate voltage is set to zero. In order to keep all the D-flip-flops at the same DC operating points, two additional nMOS transistors are connected between the ground and the first two D-flip-flops, respectively. When it operates in divide-by-5 mode, the third D-

Fig. 1 Novel 4/5 prescaler with automatic power down

<sup>\*</sup> Project supported by the National High Technology Research and Development Program of China (No. SQ2007AA01Z238433)

<sup>†</sup> Corresponding author. Email: yanyuepeng@ime.ac.cn

Fig. 2 Proposed 4/5 prescaler implemented with MCML

flip-flop is active and the prescaler works as a conventional one. The MC of the dual-modulus prescaler is reused as the enable-signal to make the third D-flip-flop active or inactive. Therefore, unlike the conventional power down mode, dividers with this proposed prescaler do not need an external enable-signal, so this technique is called "automatic power down".

When this proposed 4/5 prescaler is applied to an integer-N divider, providing the division ration; M = 5A + 4(N - A), the percentage of the power consumption saved (PS) by the 4/5 prescaler can be expressed as:

$$PS = \frac{N - A}{3 \times \left[5A + 4(N - A)\right]} \times 100\%$$

$$= 400\% \left/ 3\left(4 + 1.25 \frac{A}{N - A}\right)$$

(1)

where A, N are the values of the swallow and the programmable counter, respectively.

### 3 Proposed topology

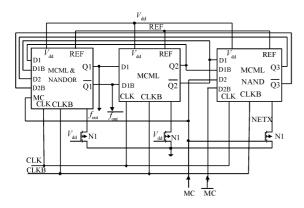

A drawback of the above MCML 4/5 prescaler is that an OR gate is added in the critical feedback loop, which causes an additional delay and reduces the prescaler's maximum operation frequency. To overcome this limitation, the embedded technique, which is widely used to increase the maximum frequency<sup>[4,6]</sup>, is applied to this MCML 4/5 prescaler. The conventional MCML 4/5 prescaler architecture and its operating mechanism can be found in Ref. [6] in detail, in which the NAND gate has already been embedded. Figure 2 is the full schematic of the proposal MCML 4/5 prescaler.

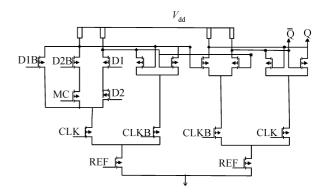

In order to embed the OR gate in Fig. 2, the first D-flip-flop is revised a little from the traditional one, as shown in Fig. 3. An additional transistor named MC is inserted, which cooperates with transistor D2B to replace the OR gate. Since the MC is differential, unlike that in Fig. 1, the inverter is unnecessary.

Fig. 3 Improved MCML D-flip-flop

## 4 Experimental results

When the proposed prescaler switches from divide-by-4 to divide-by-5, the third D-flip-flop is in "sleep" mode. Since the prescaler usually operates in very high frequency, the third D-flip-flop should wake up quickly. In order to investigate the influence of the proposed architecture on the maximum operating frequency, a conventional MCML 4/5 prescaler is designed and implemented with a TSMC 0. 25 µm mixedsignal CMOS process. The size of this prescaler is optimized according to Ref. [8] to achieve the available maximum operating frequency with less power consumption. The proposed MCML 4/5 prescaler is also designed with the identical transistor sizes. In order to keep the same DC operating point for both the conventional and proposed prescaler, the switch transistors N1 have a rather larger periphery, as shown in Fig. 2.

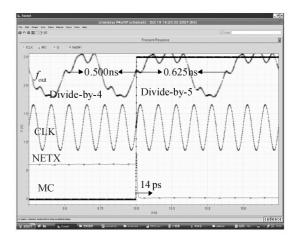

This conventional MCML 4/5 prescaler consumes 3. 3mA current with a maximum operating frequency of 8. 0GHz under a power supply of 2. 5V. This novel prescaler also consumes 3. 3mA current in divide-by-5 mode, while consuming only 2. 2mA current in divide-by-4 mode. Figure 4 shows the transient response of

Fig. 4 Simulation of the proposed 4/5 prescaler at 8GHz

Fig. 5 Die photo of the proposed prescaler and its buffer

the proposed prescaler. At a frequency of 8.0GHz, when the MC signal is rising, the prescaler changes into divide-by-5 mode immediately. As indicated in Fig. 4, the NETX achieves a proper DC operating point within 14ps, from which it can be inferred that the wake-up time of the third D-flip-flop is very short. Therefore, the prescaler's maximum operating frequency is also 8.0GHz, which shows that the proposed architecture does no harm to the maximum operating frequency.

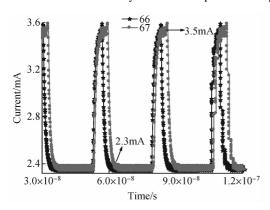

The above novel prescaler was applied to an integer-N divider with a division ratio of 66/67 and this integer-N divider was manufactured. Figure 5 is the die photo of the proposed prescaler and its buffer that is usually attached in the MCML frequency divider as a level-shifter. Its area is about  $180 \mu \text{m} \times 110 \mu \text{m}$ . From Eq. (1), in order to reduce the power consumption, the proposed prescaler should operate in the divideby-4 mode as long as possible, which minimizes A/(N- A). In order to achieve this goal, the values of the A, N must be 2,16 for division ratio 66 and 3,16 for division ratio 67, respectively. To measure the current's variety of the prescaler, a resistor is connected between the power supply line and the prescaler, and the current is achieved through dividing the measured voltage by the resistor. The currents' variabilities against time with division ratios 66/67 are shown in Fig. 6, where the input frequency of the CLK is 2. 5GHz. In Fig. 6, at divide-by-4 mode, the prescaler consumes about 2.35mA of current, while consuming about 3.55mA in divide-by-5. From Eq. (1), compared

Fig. 6 Proposed prescaler consumed current varieties against time

with the conventional prescaler, the power reduction of this one is estimated to be 28.7% for division ratio 66 and 21.5% for the division ratio 67, respectively. The maximum operating frequency of the divider is about 3.2GHz, which is less than the simulation results mainly due to its successive buffer.

### 5 Conclusion

A method is presented in this report to reduce the MCML 4/5 prescaler's power consumption, with its characteristic of making one of its three D-flip-flops automatically power down when it operates in divideby-4 mode. This technique can also be applied to various dual-modulus prescalers, such as the 2/3 TSPC prescaler, and the 8/9 and 16/17 MCML prescalers. The method to eliminate the influence to the maximum operating frequency due to the automatic power down architecture is discussed in detail. This simulation results show that the proposed MCML 4/5 prescalers is immune to the "wake-up" issue and retains the same maximum operating frequency as the conventional prescaler. A divider with this novel prescaler is manufactured and it is capable of saving more than 20% of the power compared with the conventional 4/5 prescaler.

#### References

- [1] Lee J, Razavi B. A 40-GHz frequency divider in 0.18-µm CMOS technology. IEEE J Solid-State Circuits, 2007, 39(4);594

- [2] Zhang Chunhui, Li Yongming, Chen Hongyi. A CMOS high-speed dual-modulus prescaler with new flip-flop. Chinese Journal of Semiconductors, 2001, 22(6): 788 (in Chinese) [张春晖,李永明,陈弘毅.一种采用新触发器的高速 CMOS 前置分频器. 半导体学报, 2001, 22(6): 788]

- [3] Zeng Xiaojun, Li Tianwang, Hong Zhiliang. Design of 1V 19GHz CMOS frequency divider. Chinese Journal of Semiconductors, 2003,24(4):416 (in Chinese) [曾晓军,李天望,洪志良.1V, 19GHz CMOS 分频器设计.半导体学报,2003,24(4):416]

- [4] Xu Yong, Wang Zhigong, Li Zhiqun, et al. A novel high speed lower jitter lower power dissipation dual-modulus prescaler and applications in PLL frequency synthesizer. Chinese Journal of Semiconductors, 2005, 26(1):176(in Chinese) [徐勇,王志功,李智群,等.一种新型高速低抖动低功耗双模预分频器及其在 PLL 频率综合器中的应用.半导体学报, 2005, 26(1):176]

- [5] Chi Baoyong, Shi Bingxue. A novel CMOS dual-modulus prescaler based on new optimized structure and dynamic circuit technique. Chinese Journal of Semiconductors, 2002, 23(4): 357(in Chinese) [池保勇, 石秉学. 一种基于新的优化结构和动态电路技术 CMOS 双模预分频器. 半导体学报, 2002, 23(4): 357]

- [ 6 ] Yang D J, Kenneth K O. A 14-GHz 256/257 dual-modulus prescaler with secondary feedback and its application to a monolithic CMOS 10.4-GHz phase-locked loop. IEEE Trans Microw Theory Tech, 2004, 52(2):461

- [7] Tong H, Cheng S, Martinez J S. A 13.5-mW 5-GHz frequency synthesizer with dynamic-logic frequency divider. IEEE J Solid-State Circuits, 2004, 39(2):378

[8] Nonis R, Palestri P, Selmi L, et al. A design methodology for MOS current-mode logic frequency dividers. IEEE Trans Circuit Syst I,

2007,54(2):245

## 一种具有自适应节能的新型 4/5 高速双模预分频器\*

曾降月 朱思奇 阎跃鹏节

(中国科学院微电子研究所,北京 100029)

摘要:首次提出一种自适应节能方法用于设计 4/5 高速双模预分频器,它的特点是工作在除 4 模式时,其中一个 D 类触发器处于休眠状态.使用台积电混合信号  $0.25\mu m$  CMOS 工艺,采用这一自适应节能的设计方法,设计了一个具有源极耦合结构的 4/5 高速双模预分频器.仿真结果证明,这一新型 4/5 高速双模预分频器不受休眠到工作转换状态的影响,最高工作频率保持不变.同时,流片结果表明,当这一新型高速预分频器用于实现 66/67 分频时,可节省高达 20% 以上的功耗.

关键词: MCML 预分频器; 自适应节能; 频率合成器

EEACC: 1265B; 2570D; 1230B

中图分类号: TN386 文献标识码: A 文章编号: 0253-4177(2008)08-1449-04

<sup>\*</sup> 国家高技术研究发展计划资助项目(批准号: SQ2007AA01Z238433)

<sup>†</sup>通信作者.Email:yanyuepeng@ime.ac.cn 2007-12-27 收到,2008-04-17 定稿