# 新型高速低功耗显式脉冲触发器电路设计\*

### 张小阳 贾 嵩 王 源 张钢刚

(北京大学微电子学研究院 教育部微电子器件与电路重点实验室,北京 100871)

摘要:提出了两种新型脉冲触发器结构——EXPAND 触发器和 EXPAND-TG 触发器.同传统结构相比,新结构一方面通过减小中间节点电容提高电路充放电速度,另一方面通过消除信号竞争避免直流短路电流对电路速度和功耗的影响.同其他文献报道的结构相比,新结构在功耗和速度上均有明显的改进.

关键词:数字电路;触发器;高速;低功耗;脉冲

EEACC: 1265A: 2570D

中图分类号: TN431.2 文献标识码: A 文章编号: 0253-4177(2008)10-2064-05

### 1 引言

触发器作为同步系统中的时序模块,其性能和功耗对系统的特性有着重要的影响.有报道称,包括触发器、锁存器在内的时钟网络消耗了30%~60%的系统功耗,而其中高达90%的功耗被触发器本身及用于驱动触发器的网络消耗<sup>[1]</sup>,所以降低触发器功耗对减少系统功耗有着重要的意义.另一方面,触发器的延迟时间和建立时间也占据了很大部分的系统时钟周期<sup>[2]</sup>,高速触发器设计对高性能应用来说也是不可缺少的<sup>[3]</sup>.

近年来,高速、低功耗的触发器设计已成为研究热点<sup>[4-7]</sup>.在为数众多的触发器结构中<sup>[2]</sup>,静态触发器采用基于传输门的多路选择器结构采样数据和基于交叉耦合反相器的双稳态结构保存数据,具有良好的抗噪声特性,因此工作稳定性较高,广泛应用于标准单元的设计中.但由于其速度较慢,无法满足高速应用的需要.动态触发器利用传输门开关采样数据,节点电容存储数据,因此具有速度优势.但是动态节点由于泄漏电流和电荷分享等问题,可能引起噪声特性的下降,影响工作稳定性,这个问题在深亚微米工艺中变得更加突出.此外,动态电路需要时钟控制预充和求值,因此动态功耗也较静态电路大.

脉冲触发器利用动态电路采样数据,静态电路保存数据,具有高速、低功耗的特点,在高速微处理器电路设计中受到广泛关注<sup>[3]</sup>.其中,显式脉冲触发器(explicit-pulsed flip-flop)中的脉冲产生电路可以被多个触发器共享,有利于节约硬件开销,因此受到更多的关注<sup>[3]</sup>.另外,对于脉冲触发器,因为在脉冲有效的一段时间中采样输入信号,这样时钟有效沿以后仍然可以进行数据采用,所以数据信号的建立时间是负值.这种时序特性意味着本周期可以借用上个周期的部分时间,进行组合逻辑的运算<sup>[2]</sup>,有利于高速应用.

作者提出了一种新型的显式脉冲触发器结构,通过

减小电路中间节点的电容提高充放电速度,同时通过避免信号竞争消除了直流短路电流,这样就缩短了触发器的延迟时间,并降低了动态功耗.

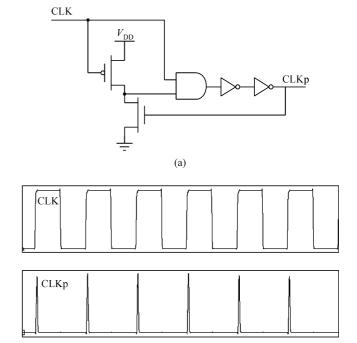

# 2 显式脉冲触发器

图 1 中所示为正常时钟 CLK 及其产生的脉冲时钟 CLKp 的波形图. 脉冲时钟产生电路利用 CLK 的上升 沿,每周期产生一个脉冲信号, 脉冲触发器在脉冲时钟 低电平期间保持数据, 在时钟高电平期间采样数据. 下面列举一些常见的显式脉冲触发器.

图 1 显式脉冲触发器的脉冲产生电路<sup>[2]</sup> (a) 脉冲产生电路;(b) 时钟与脉冲波形

Fig. 1 Pulse generator for explicit-pulsed flip-flop<sup>[2]</sup> (a) Pulse generator; (b) Waveforms of clock and pulse signals

<sup>\*</sup> 国家大学生创新性实验计划资助项目

<sup>†</sup> 通信作者.Email:jias@pku.edu.cn 2008-01-18 收到,2008-06-12 定稿

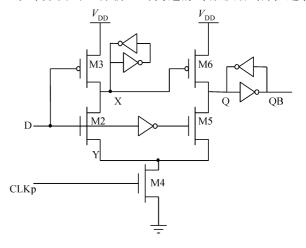

图 2 显式近输出脉冲触发器[4]

Fig. 2 Explicit-pulsed data-close-to-output flip-flop<sup>[4]</sup>

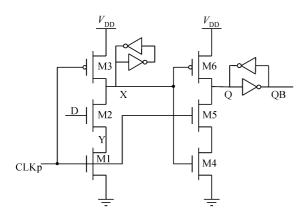

图 2 为显式近输出脉冲触发器(EP-DCO FF)的电路图<sup>[4]</sup>.EP-DCO 电路由两级时钟控制反相器结合交叉耦合反相器组成,主锁存器的采样电路为动态结构,锁存电路采用静态电路,而从锁存器的采样和锁存电路均为静态结构,可以减小内部节点的跳变因子,有利于降低动态功耗.在脉冲时钟低电平期间 M3 对 X 节点充电,X 保持高电平,主锁存器处于预充阶段;而在此期间,从锁存器的采样电路屏蔽输入信号,保持前一周期采样数据. 当脉冲为高电平期间,主锁存器采样 D 信号,从锁存器采样 X 节点信号,并输出到 Q 和 QB 端,直到短暂的时钟脉冲结束.

通过分析,容易看出该电路的最大 C-Q 延迟时间为两级门延迟,即由采样高电平 D 信号过程中 M2,M1对 X 节点放电,然后引起 M6 对 Q 节点充电的路径延迟,我们把这个延迟定义为  $T_{\rm COH}$ .而采样低电平 D 信号过程中由于 X 节点不会被 M2,M1 放电,此时的 C-Q 延迟为一级门延迟,即 M5,M4 对 Q 节点放电的路径延迟,我们把这个延迟定义为  $T_{\rm COL}$ .  $T_{\rm COH}$ 是二者之中较大的延迟,影响系统的最大周期时间,即系统速度.下面我们均用最大传输延迟  $T_{\rm COH}$ 来描述脉冲触发器的速度特性.

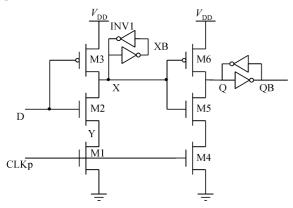

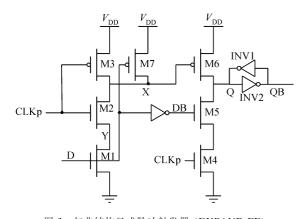

图 3 为显式静态脉冲触发器 (EPSFF)的电路图<sup>[5]</sup>,同EP-DCO相比,该结构将主锁存器的采样电路改为静态电路,目的是减少 X 节点充放电几率,降低功耗.

图 3 显式静态脉冲触发器[5]

Fig. 3 Explicit-pulsed static flip-flop<sup>[5]</sup>

图 4 条件放电触发器[6]

Fig. 4 Conditional discharge flip-flop<sup>[6]</sup>

图 4 为条件放电触发器(CDFF)的电路图[6],该结构将主锁存器中交叉耦合反相器改为图中所示结构,因为该部分电路的功能主要是在采样低电平 D 信号过程中保持 X 节点的高电平,减少一个 nMOS 器件后并不影响该功能,这样可以减少 X 节点处的电容;而且,该结构中将 M4 器件的控制信号由 X 节点信号改为反相的 D 信号,从而减小了 X 节点电容.此外,CDFF 在 X 节点放电通路上增加了一个 M8,可以避免 X 节点不必要的放电以降低动态功耗,但是其放电通路的等效电阻有所增加.

图 5 为单管时钟显式脉冲触发器(STC-EPFF)的电路结构<sup>[5]</sup>,该结构将 EPSFF 中时钟控制的 2 个 nMOS 器件 M1 和 M4 合并为一个器件,目的是减小时钟的负载电容.

# 3 新型显式脉冲触发器结构

#### 3.1 与非结构显式脉冲触发器(EXPAND FF)

本部分提出一种新型的高速脉冲触发器结构,适合

图 5 单管时钟显式脉冲触发器[5]

Fig. 5 Single transistor clocked EPFF<sup>[5]</sup>

图 6 与非结构显式脉冲触发器 (EXPAND FF)

Fig. 6 EXplicit-pulsed nAND flip-flop (EXPAND FF)

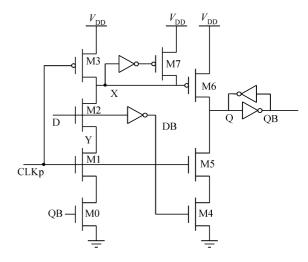

于高速、低功耗设计应用. 该结构如图 6 所示,由于其中主锁存器的主要部分为一个二输入与非门,我们将其命名为显式脉冲与非结构触发器(EXPAND FF). 该结构主要通过提高充放电速度来减小脉冲触发器的传输延迟时间  $T_{\text{COH}}$ . 其主要改进包括:

(1)利用 pMOS 器件 M7 代替交叉耦合反相器,作 为主锁存器的状态保持器件.如果触发器采样高电平数 据 D,在脉冲时钟高电平期间, M7 截止, X 节点放电, 数 据通过 M6 对 O 节点充电被传递到输出端,完成采样; 如果触发器采样低电平数据 D,在时钟高电平期间,M3 和 M1 截止, X 节点没有下拉, M7 导通, 维持对 X 节点 的上拉,从而保证了该节点的静态工作特性,即数据不 是靠 X 节点电容动态保持,因此电路具有良好的可靠 性.EP-DCO,EPSFF和STC-EPFF等结构中采用交叉 耦合反相器实现静态存储,而 CDFF 结构中去掉了一个 nMOS 器件,依靠反相的 X 信号控制 pMOS 器件保持 X 节点的高电平. 这些结构中 X 节点的电容负载较大, 直接影响放电速度.如图 6 所示,EXPAND FF 结构利 用一个 pMOS 器件代替了交叉耦合反相器中的 4 个 器件,并且借鉴 CDFF 和 STC-EPFF 结构中用反相数 据信号 DB作为 M5 器件栅极信号,减少了 X 节点电 容.

对于前面结构中的主锁存器的交叉耦合反相器结构,时钟低电平期间被预充并保持 X 节点高电平;当时钟上升沿到来,触发器进入采样阶段,nMOS 放电通路同交叉耦合反相器中导通的 pMOS 器件同时导通,产生竞争,影响放电速度,并引起直流短路功耗.这个问题可以通过减小交叉耦合反相器中维持电平的反相器的器件尺寸而部分地解决,一般需要将其器件取为宽长比小于1,但是这样又会进一步增加 X 节点的电容.而对于图 6 中所示的 EXPAND FF 结构来说,同样情况下,nMOS 下拉之前,高电平的数据 D 使得 M7 截止,完全避免了这种信号竞争带来的速度和功耗方面的消极影响.

(2)图 6 所示的 EXPAND FF 结构中,将主锁存器中放电通路中的两个 nMOS 器件的顺序进行了调整,将时钟控制 nMOS 器件安排在靠近 X 节点的位置.在时

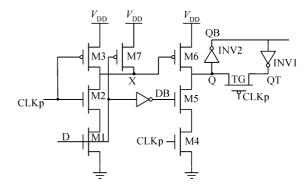

图 7 与非传输式显式脉冲触发器 (EXPAND-TG FF)

Fig. 7 EXplicit-pulsed nAND transmission-gate flip-flop (EX-PAND-TG FF)

钟上升沿到来之前,高电平的数据 D 信号已经使得 M1 器件导通,将 Y 节点放电,因此可以加快 X 节点的放电速度,从而减少触发器的传输延迟时间.

综上所述,EXPAND FF 结构通过减少 X 节点电容和调整器件位置加快放电过程,提高了触发器的工作速度;而减小 X 节点电容也有利于降低触发器的跳变功耗,同时避免了信号竞争,消除了短路功耗.此外,触发器工作过程中,X 还是一个静态节点,保持了良好的抗噪声特性.后面的电路仿真结果也验证了以上分析过程.

#### 3.2 与非传输式显式脉冲触发器(EXPAND-TG FF)

EXPAND FF 主要通过优化主锁存器中的节点电容,达到提高传输延迟的目的.根据前面的分析,脉冲触发器的最大传输延迟,由主锁存器中的下拉放电通路和从锁存器中的上拉充电通路组成,我们通过对 EXPAND FF 结构中从锁存器部分的优化,提出另一种与非传输式显式脉冲触发器(EXPAND-TG FF),目的是在 EXPAND FF 的基础上进一步提高触发器的速度,并降低功耗.

EXPAND FF 结构中的从锁存器采用的是交叉耦合反相器,如前所述,这种结构在采样过程中可能产生信号竞争,引起直流短路功耗,并影响电路速度.对于图6中的 EXPAND FF 结构,这种竞争发生在脉冲时钟高电平,即触发器采样阶段,例如如果前一个周期从锁存器的 Q端存储一个低电平数据,而现在的采样阶段将采样高电平的数据 D,则图中 M6 对 Q 节点的充电过程和 INV1 反相器中 nMOS 的放电过程产生竞争,增加了C-Q 延迟和直流短路功耗.

图 7 为 EXPAND-TG FF 结构,其中将 EXPAND FF 中从锁存器的交叉耦合反相器增加 pMOS 传输门开关,传输门的控制信号为脉冲时钟.在脉冲时钟低电平,即主锁存器预充、从锁存器保持阶段,传输门 TG 导通,交叉耦合反相器静态保持前一周期数据.当时钟上升沿到来,从锁存器进入采样阶段,pMOS 截止,该路径上的竞争被消除,缩短了 C-Q 传输延迟.这一改进既加快了Q 节点的充电速度,又消除了直流短路功耗.

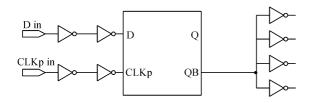

图 8 仿真电路结构 Fig. 8 Structure of testbench

# 4 电路仿真结果

为了验证以上分析结果,我们对常用的 EPFF 和本文中提出的新型结构进行了电路仿真,仿真电路如图 8 所示,输入信号经过缓冲器连接到触发器,输出信号驱动负载电容,其中缓冲器为 2 级反相器,负载电容为 4 个反相器的输入电容之和;时钟脉冲信号采用图 1 所示结构;而缓冲器、负载反相器和时钟产生电路的功耗没有计入触发器部分的功耗统计.

电路仿真器为 HSPICE,环境温度设为 25 亿.模型 参数来自中芯国际(SMIC)  $0.13\mu m$  数字工艺,电源电压为 1.2V,最小多晶硅栅长  $0.13\mu m$ ,最小器件沟道宽度  $0.15\mu m$ , nMOS/pMOS 阈值电压为 0.31V/-0.28V.

对于图 2~7 所示的 EPFF 电路结构,器件尺寸对 其特性有着很大的影响,为了能够公正地比较不同结构 的电路特性,我们将所有电路中的 nMOS 器件宽度取为  $2\lambda(\lambda$  取为  $0.13\mu$ m),pMOS 器件宽度取为  $4\lambda$ ,器件长度 均取为  $\lambda$ ;对于交叉耦合反相器,为了使其能够正常工作,将其中保持电路状态的反相器宽度取为  $\lambda$ ,长度取为  $2\lambda$ ,即为反比例关系.此外,器件的源漏区面积和周长数 据也基于 SMIC 的相关版图设计规则进行了估算.

电路仿真结果如表 1 所示,其中速度参数主要为关键路径传输延迟时间  $T_{COH}$ ,即数据 D 为高电平、时钟上升沿到 Q 端输出的延迟时间;建立时间为数据 D 超前脉冲时钟上升沿的时间;功耗为触发器部分的跳变功耗.时钟频率为 2GHz,为了模拟实际工作的情况,输入端 D 采用如下的序列 D = '0010 1101 1000 0111 1111 1010 00',一共 26 个周期,包含了各种逻辑值和活动因子的情况,根据仿真结果统计了触发器跳变功耗的平均

表 1 电路仿真结果 Table 1 Simulation results of the circuits

| Name         | Transistor $T_{\text{CQH}}$ |       | $T_{ m SETUP}$ | Power    | Power          | PDP   |

|--------------|-----------------------------|-------|----------------|----------|----------------|-------|

|              | count                       | /ps   | /ps            | $/\mu W$ | $/(\mu W@GHz)$ | / fJ  |

| EP-DCO       | 14                          | 131.9 | - 135.9        | 77.29    | 38.65          | 10.19 |

| EPSFF        | 14                          | 117.1 | -0.917         | 63.01    | 31.50          | 7.376 |

| CDFF         | 16                          | 123.7 | -54.02         | 62.12    | 31.06          | 7.682 |

| STC-EPFF     | 15                          | 110.0 | -119.5         | 65.00    | 32.50          | 7.147 |

| EXPAND FF    | 13                          | 83.86 | - 54.54        | 61.95    | 30.98          | 5.195 |

| EXPAND-TG FI | F 14                        | 67.98 | - 49.61        | 61.82    | 30.91          | 4.202 |

表 2 归一化结果

Table 2 Normalized results of circuit simulation

| Name         | $T_{\rm CQH}$ | Power         | PDP   |

|--------------|---------------|---------------|-------|

| Name         | /ps           | $/\mu { m W}$ | /fJ   |

| EP-DCO       | 1.00          | 1.00          | 1.00  |

| EPSFF        | 0.888         | 0.815         | 0.724 |

| CDFF         | 0.938         | 0.804         | 0.754 |

| STC-EPFF     | 0.834         | 0.841         | 0.701 |

| EXPAND FF    | 0.636         | 0.802         | 0.510 |

| EXPAND-TG FF | 0.515         | 0.800         | 0.412 |

值;功耗延迟积(PDP)为传输延迟和跳变功耗的乘积,该参数可以比较速度和功耗的综合特性.表2为电路仿真结果的归一化,更易于看出各种结构 EPFF 的特性.

由仿真数据可看出,EXPAND FF 相比 EP-DCO 结构,延迟时间下降 36%,功耗下降 20%,功耗延迟积下降 49%;而 EXPAND-TG FF 在延时方面有进一步的改进,同 EP-DCO 相比,延迟时间降低了 49%,功耗降低了 20%,功耗延迟积降低了 59%.与文献报道的其他电路结构相比,新结构触发器的延迟时间有着相当大的改进.在其他方面,EXPAND 电路中 MOS 管数目也较少;而对于电路的建立时间,EXPAND 和 EXPAND-TG 电路的建立时间均为负值,数值上仅次于 EP-DCO电路.

# 5 结论

提出了两种适用于高速度、低功耗的显式脉冲触发器电路,相比于其他脉冲触发器,新电路通过减小节点电容和消除竞争,提高了电路速度,并降低了动态功耗.电路仿真结果表明,同其他文献报道的结构相比,新结构的速度和功耗特性有着明显的改进,表明新结构适合高速、低功耗的数字系统设计.

#### 参考文献

- [1] Tschanz J. Narendra S. Chen Z P. et al. Comparative delay and energy of single edge-triggered & dual edge-triggered pulsed flip-flops for high-performance microprocessors. International Symposium on Low Power Electronics and Design, 2001;147

- [2] Chandrakasan A. Bowhill W. J., Fox F. Design of high-performance microprocessor. Piscataway, NJ; IEEE Press, 2001

- [3] Kawaguchi H, Sakurai T. A reduced clock-swing flip-flop (RCS-FF) for 63% power reduction. IEEE J Solid-State Circuits, 1998, 33,807

- [4] Rabaey J, Chandrakasan A, Nikolic B. Digital integrated circuits: a design perspective. 2nd ed. New Jersey: Prentice Hall, 2003

- [5] Zhao P, Darwish T, Bayoumi M. Low power and high speed explicit-pulsed flip-flops. The 45th Midwest Symposium on Circuits and Systems Conf, 2002, 2: II-477

- [6] Zhao P.Darwish T.Bayoumi M. High-performance and low-power conditional discharge flip-flop. IEEE Trans Very Large Scale Integr Syst, 2004, 12:477

# Design of Low Power and High Performance Explicit-Pulsed Flip-Flops\*

Zhang Xiaoyang, Jia Song<sup>†</sup>, Wang Yuan, and Zhang Ganggang

(Key Laboratory of Microelectronic Devices and Circuits, Institute of Microelectronics, Peking University, Beijing 100871, China)

**Abstract:** The speed and delay of flip-flops are critical to the performance of digital circuit systems. Two novel structures for dual-edge triggered explicit-pulsed flip-flops are proposed in this paper. The charging and discharging times are greatly reduced due to the lower capacitance of the interval nodes in the new structures, and the short circuit power consumption is diminished by overcoming the race problem as well. The flip-flops are also superior to the structures reported in the literature in terms of both power dissipation and working speed.

Key words: digital circuits; flip-flops; high speed; low power; pulse

EEACC: 1265A; 2570D

Article ID: 0253-4177(2008)10-2064-05

<sup>\*</sup> Project supported by the National Innovative Fund for Undergraduates

<sup>†</sup> Corresponding author. Email: jias@pku.edu.cn