# Characterization of the triple-gate flash memory endurance degradation mechanism

Cao Zigui(曹子贵)<sup>1,2,3,†</sup>, Sun Ling(孙凌)<sup>1,2,3</sup>, and Lee Elton(李嘉秩)<sup>3</sup>

(1 Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, Shanghai 200050, China)

(2 Graduate University of the Chinese Academy of Sciences, Beijing 100049, China)

(3 Grace Semiconductor Manufacturing Corporation, Shanghai 201203, China)

**Abstract:** Write/erase degradation after endurance cycling due to electron trapping events in triple-gate flash memory have been detected and analyzed using a UV erasure method. Different from the commonly degradation phenomenon, write-induced electron trapping in the floating gate oxide, electron trapping in tunneling oxide is observed in triple-gate flash memory. Further, the degradation due to single-electron locally trapping/de-trapping in horn-shaped SuperFlash<sup>®</sup> does not occur in the triple-gate flash cell. This is because of planar poly-to-poly erasing in the triple-gate flash cell instead of tip erasing in the horn-shaped SuperFlash<sup>®</sup> cell. Moreover, by TCAD simulation, the trap location is identified and the magnitude of its density is quantified roughly.

**Key words:** Fowler-Nordheim tunneling; endurance; traps; UV erasure **DOI:** 10.1088/1674-4926/30/1/014003 **PACC:** 7220J; 7340Q

# 1. Introduction

Electron trapping in charge-transfer dielectrics is known to be a limiting factor of write/erase (W/E) cycling endurance of non-volatile floating-gate memories. In SSI flash memory, which uses enhanced channel hot-electron injection (CHEI) for programming and Fowler-Nordheim tunneling for erasing<sup>[1,2]</sup>, electrons will be trapped in the tunnel oxide (TUNOX) or at the injection point of floating gate oxide (FGOX), resulting in gradual degradation of erase characteristics and leading to the closure of the memory cell threshold window. So, it is necessary to make sure that the trap location is accurately identified for the development of optimized program/erase schemes and memory cell design.

It is generally believed that charge trapping at the injection point of the device during programming is considered to dominate the weak erase failure. Houdt et al. put forward that charges trapping at the injection point dominate the endurance degradation of high injection MOS (HIMOS) flash memory which normally uses Fowler-Norheming (FN) tunneling at the source side for erase<sup>[4]</sup>. Hu and Wu et al. demonstrated similar results in the horn-shaped flash memory[5-9]. In contrast to the research above, Tkachev and Liu proved, when the polyto-poly erasure was applied, that charges trapping in the tunnel oxide (TUNOX) exert much greater effect on the degradation in the horn-shaped dual-gate SuperFlash® cell<sup>[3,13]</sup>. With the cell size scaling down and the geometry complex, the endurance degradation monitoring directly is a great challenge in the triple-gate flash cell. So far, there lacks detailed analysis and characterization of oxide degradation in the triplegate flash cell. In this paper, we will focus on clarifying the

# 2. Device fabrication and experimental setup

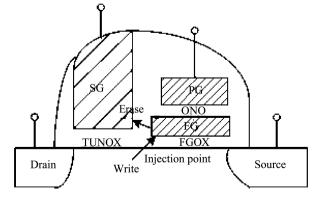

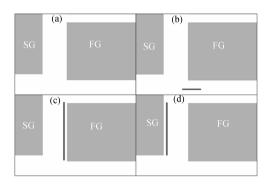

Write/erase degradation after endurance cycling in SSI flash EEPROM devices is studied using the triple-gate flash transistor as a typical example (Fig.1). During erasing, instead of exploiting tunneling through FGOX at the source side, as commonly adopted in HIMOS, the triple-gate flash utilizes FN tunneling of the electron from FG to SG. Programming is performed by enhanced CHEI at the injection point of the device. The detailed description of the operation and the underlying device physics is given in Refs.[10–12].

The cell was fabricated in a standard  $0.12 \,\mu\text{m}$  self-aligned flash process. The oxide under the floating gate was thermal grown of 9 nm thick and the inter-poly dielectric layer under

Fig.1. Schematic diagram of the triple-gate flash.

trap location being identified and analyze its effects on device characteristics using UV erasure. Further, TCAD simulation is applied to verify the results and approximately quantify the number of traps.

<sup>†</sup> Corresponding author. Email: steamcao@gsmcthw.com Received 1 July 2008

J. Semicond. 30 (1) Cao Zigui et al.

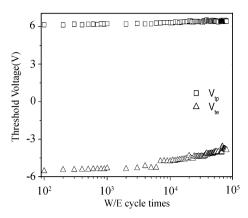

Fig.2. Endurance characteristic in triple-gate flash, showing a slightly shift in the written threshold ( $V_{\rm tp}$ ) but a deeper shift in the erased threshold ( $V_{\rm te}$ ).

SG was about 12 nm grown by high temperature oxidation (HTO), with a  $N_2O$  anneal process post its formation. In this study, the threshold voltage  $(V_t)$  is always defined as the program gate voltage  $(V_{PG})$  that corresponds to a fixed drain (BL) current  $(I_d)$  of 1  $\mu$ A at the BL bias of 0.1 V with a select gate (SG) voltage  $(V_{SG})$  2.5 V.

In order to identify the mechanism of write/erase degradation, a technique of ultraviolet (UV)light is applied at various stages throughout the endurance measurement. A UV erase operation is self-limiting and the device always ends up in the same equilibrium state with the same reference charge on the FG. Thus, any change in cell characteristics after UV erase will reveal only the damage in the oxide during W/E cycling, and will not be affected by changes in the amount of the stored FG charge.

The electric parameters were measured on HP4156. The measurement of  $V_t$ . kinetics during cycling included: regular programming and erase, and measurement of cell threshold voltage in program or erase status.

#### 3. Results and discussion

## 3.1. Endurance characteristic

Figure 2 shows the endurance characteristic of the triplegate flash memory cell. As can be seen, the erased threshold ( $V_{te}$ ) shows a large increase (~2.5 V) with the number of W/E cycles, implying a large decrease of the read-out current, whereas the written threshold ( $V_{tp}$ ) is lightly affected by repeated W/E operations. Since the cell is written by enhanced channel hot electron injection from channel to FG at the injection point through a thin oxide, the initial conclusion would ascribe this degradation behavior to electron trapping in FGOX<sup>[8–12]</sup>. However, in the following sections it will be shown that this conclusion is not reliable in triple-gate flash devices.

#### 3.2. I-V characteristics

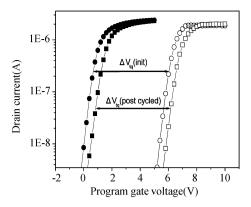

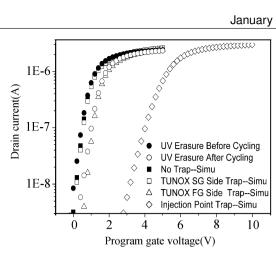

By comparing the *I-V* characteristics in a particular threshold state with the characteristics after UV erasure

Fig.3. Drain current versus program gate voltage characteristics in the written state, showing nearly no charge amount change on the FG with W/E cycling.  $\Delta V_{\rm tq}$  is a measure of the charge on the FG. (Full dots: fresh device after UV erasure; Open dots: fresh device in written state; Full squares: 60 000 cycles and UV erasure; Open squares: 60 000 cycles and written state).

during W/E cycling, the change in the amount of FG charge can be monitored. Indeed, since the device is always back to a state with the same reference charge on the FG after UV erasure,  $V_{\rm t}$  can be expressed as

$$V_{\rm t} = V_{\rm tuv} + \Delta V_{\rm tq},$$

where  $V_{\rm tuv}$  is the threshold voltage after UV erasure. The charge on the FG is always the same after UV erasure.  $\Delta V_{\rm tq}$  is the  $V_{\rm t}$  shift induced by the additional charge on the FG with respect to the UV erased state. A change in  $\Delta V_{\rm tq}$  in the written or the erased state is thus indicative of a change in the amount of charge transferred to or from the FG. Therefore, by evaluating the  $\Delta V_{\rm tq}$  during a degradation measurement, the  $V_{\rm t}$  shift due to the charge amount change on the FG can be monitored as a function of the number of W/E cycles.

Figure 3 shows the  $I_{\rm d}$ – $V_{\rm pg}$  curve of a written device combined with UV erasure, measured under read out conditions ( $V_{\rm BL}=0.1~\rm V,~V_{\rm SG}=2.5~\rm V$ ), before and after 60 000 W/E cycles. As can be seen,  $\Delta V_{\rm tq}$  in the written state has no degradation even after 60000 W/E cycles. This implies that, after writing, the net charge amount on the FG remains at almost the same level in the states before and after W/E cycles. Moreover, after P/E cycling, no severe degradation of the subthreshold slope is observed, impling that few negative trapping electrons exist at the injection point. The severe sub-threshold slope degradation can be caused by an interface trap density ( $D_{\rm it}$ ) or by highly localized negative oxide trapped charge in coupling oxide<sup>[8]</sup>.

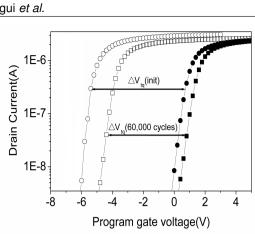

However, an obvious different phenomenon is observed in the erased state compared to that in the written state. As can be seen from Fig.4,  $\Delta V_{\rm tq}$  has decreased considerably after 60 000 W/E cycles (~1 V), which means the degradation of the erase characteristic. If the weak erase issue is due to electrons trapped at the injection point in coupling oxide, then  $\Delta V_{\rm tq}$  in the written state should be decreased due to the suppression of channel hot electron injection efficiency. But this is inconsistent with the result shown in Fig.3. On the contrary,

Cao Zigui et al. January 2009

Fig.4. Drain current versus program gate voltage characteristics in the erased state, showing a changing amount of charge out of the FG with W/E cycling.  $\Delta V_{tq}$  is a measure of the charge out of the floating gate. (Full dots: fresh device after UV erasure; Open dots: fresh device in the erased state; Full squares: 60 000 cycles and UV erasure; Open squares: 60 000 cycles and erased state).

Fig.5. Electron trapping location simulated structure: (a) Without electron trapping; (b) Electron trapping at the injection point of FGOX; (c) Electron trapping in TUNOX at the FG side; (d) Electron trapping in TUNOX at the SG side.

electrons trapped in the tunneling oxide could explain it. After W/E cycling, electrons trapped in the tunneling oxide will block the tunneling of the electron on the FG, as well as decrease the field between SG and FG. Therefore, due to the decrease of the electrons amount transferred from FG, less positive FG voltage is achieved and it will lead to the lower write efficiency. But the net charge in the written state will remain nearly unchanged. Based on different phenomena between pre-cycling and post cycling electron amount alteration in the floating gate between the program state and the erase state, in combination with non-degradation of the sub-threshold slope, we can conclude that major oxide traps should exist in IPO between SG and FG.

Moreover, in this study, we did not see the single electron trapping/de-trapping events<sup>[7]</sup> in the triple-gate flash device. A possible reason should be planar shaped erasing mode in triple-gate flash compared to the horn-shaped erasing mode in the double poly SuperFlash flash cell.

## 3.3. Trap location simulation and mechanism analysis

Figures 5 and 6 give the electron trapping location TCAD identification structure and result W/O traps at different loca-

Fig.6. Electron trapping location simulation results, showing that the sub-threshold slope nearly does not degrade with electron trapping in TUNOX compared to severe degradation with electron trapping in FGOX.

tions compared to the UV erasure results with/without 60 000 W/E cycles. As can be seen from Fig.6, the curves with electron trapping in TUNOX show a similar sub-threshold slope as that without electron trapping. However, severe degradation is observed with electron trapping in FGOX. The simulation results are in agreement with the observation above. The magnitude of the tunneling oxide traps is approximate  $10^{12} \, \mathrm{cm}^{-3}$  after 60 000 P/E cycles from the simulation result.

The endurance degradation mechanism in the triple-gate flash cell can be explained as below. Due to high electric field existence during erasure, as well as worse oxide integrity of tunneling oxide against coupling oxide, more traps will be generated in the tunneling oxide during W/E cycles. With the electrons trapped during the erasure procedure, the FN tunneling field will depressed and result in lower FG potential. Finally, the cell current will be degraded and lead to the failure of endurance.

## 4. Conclusion

In this paper, the endurance degradation after write/erase cycles in triple-gate flash memory have been detected and analyzed using UV erasure. Comparing the *I–V* curve with UV erasure before and after the cycling test, it is found the weak erase is dominated by the generation of electron traps in the tunneling oxide. This finding is contrary to the conventional point of view, which considers coupling oxide degradation after W/E cycling dominating the weak erase issue. Moreover, by TCAD simulation, the traps' location is identified again and the magnitude of their density is quantified roughly. So, in order to improve the endurance characteristic of triple-gate flash memory, optimizing the erase conditions and improving the tunnel oxide integrity is necessary.

#### References

Van Houdt J, Wellekens D, Haspeslagh L. The HIMOS flash technology: the alternative solution for low-cost embedded memory. Proc IEEE, 2003, 9: 627 J. Semicond. 30 (1) Cao Zigui et al.

[2] Kynett V, Fandrich M, Anderson J, et al. A 90-ns one-million erase/program cycle 1-Mbit flash memory. IEEE J Solid-State Circuits, 1989, 24: 1259

- [3] Liu X, Markov V, Kotov A, et al. Endurance characteristics of SuperFlash<sup>®</sup> memory. IEEE 8th International Conference on Solid-State and Integrated Circuit Technology, 2006: 763

- [4] Wellekens D, van Houdt J, Faraone L, et al. Write/erase degradation in source side injection flash EEPROM's: characterization techniques and wear-out mechanisms. IEEE Trans Electron Devices, 1995, 42:1992

- [5] Wu T I, Chih Y D, Chen S H, et al. Characterization of split gate flash memory endurance degradation mechanism. IEEE Proceedings of 11th IPFA, 2004: 115

- [6] Hu L C, Kang A C, Chen E, et al. Gate stress effect on low temperature data retention characteristics of split-gate flash memories. Microelectron Reliab, 2005, 45: 1331

- [7] Hu L C, Kang A C, Wu T Y, et al. Efficient low-temperature data retention lifetime prediction for split gate flash memories using a voltage acceleration methodology. IEEE Trans Device Mater Reliab, 2006, 6: 528

- [8] Hu L C, Kang A C, Tai I, et al. Statistical modeling for post-

- cycling data retention of split-gate flash memories. 42th Annual International Reliability Physics Symposium, 2004: 643

- [9] Hu L C, Kang A C, Shih J R, et al. Statistical modeling for postcycling data retention of split-gate flash memories. IEEE Trans Device Mater Reliab, 2006, 6: 60

- [10] Van Houdt J, Heremans P, Deferm L, et al. Analysis of the enhanced hot-electron injection in split-gate transistors useful for EEPROM applications. IEEE Trans Electron Devices, 1992, 39: 1150

- [11] Van Houdt J, Haspeslagh L, Wellekens D, et al. HIMOS-a high efficiency flash E<sup>2</sup>PROM cell for embedded memory applications, IEEE Trans Electron Devices, 1993, 40: 2255

- [12] Van Houdt J, Wellekens D, Faraone L, et al. A 5 V-compatible flash EEPROM cell with microsecond programming time for embedded memory applications. IEEE Trans Comp Hybrids Manuf Technol, 1994, 17: 380

- [13] Tkachev Y, Liu X, Kotov A, et al. Observations of single electron trapping/detrapping events in tunnel oxide of SuperFlash® memory cell. Non-Volatile Memory Technology Symposium, 2004: 45