# Low-power wide-locking-range injection-locked frequency divider for OFDM UWB systems\*

Yin Jiangwei(尹江伟)<sup>1</sup>, Li Ning(李宁)<sup>1,†</sup>, Zheng Renliang(郑仁亮)<sup>1</sup>, Li Wei(李巍)<sup>1</sup>, and Ren Junyan(任俊彦)<sup>1,2</sup>

(1 State Key Laboratory of ASIC & System, Fudan University, Shanghai 201203, China) (2 Micro/Nano Science and Innovation Platform, Fudan University, Shanghai 201203, China)

Abstract: This paper describes a divide-by-two injection-locked frequency divider (ILFD) for frequency synthesizers as used in multiband orthogonal frequency division multiplexing (OFDM) ultra-wideband (UWB) systems. By means of dual-injection technique and other conventional tuning techniques, such as DCCA and varactor tuning, the divider demonstrates a wide locking range while consuming much less power. The chip was fabricated in the Jazz 0.18  $\mu$ m RF CMOS process. The measurement results show that the divider achieves a locking range of 4.85 GHz (6.23 to 11.08 GHz) at an input power of 8 dBm. The core circuit without the test buffer consumes only 3.7 mA from a 1.8 V power supply and has a die area of 0.38 × 0.28 mm<sup>2</sup>. The wide locking range combined with low power consumption makes the ILFD suitable for its application in UWB systems.

**Key words:** UWB; ILFD; frequency synthesizer; divide-by-two **DOI:** 10.1088/1674-4926/30/5/055003 **PACC:** 2560

# 1. Introduction

The prospect of wireless date transmission at rates of hundreds of Mbps has drawn much attention from both academia and the industry to the ultra-wideband (UWB) system. Proposed by the multi-band orthogonal frequency division multiplexing (OFDM) alliance (MBOA), the entire UWB spectrum (from 3.1 to 10.6 GHz) is divided into 14 channels (bands) with a spacing of 528 MHz<sup>[1]</sup>. Usually, frequency synthesizers are employed in UWB transceivers to generate carriers for frequency hopping between different bands.

In phase locked loop (PLL)-based frequency synthesizers, the frequency divider (FD) is one of the most important building blocks and consumes a significant amount of power. More importantly, the power consumption of an FD will grow drastically with increasing operating frequency. Reducing the power consumption of the FD is, therefore, a critical issue in modern portable battery supplied equipment<sup>[2]</sup>. It remains a challenging task to design high-frequency dividers with low power dissipation.

Existing high-speed FDs can be categorized into three groups: flip-flop-based current-mode-logic (CML) FDs, regenerative dividers and ILFDs. CML FDs are widely used in high-speed PLLs due to their simple design and robust operation. However, they consume a significant amount of power at high input frequencies, which limits their applications in high-frequency low-power systems. Regenerative dividers can operate at very high frequencies (tens of gigahertz), but the main constrains are complex circuit implementation and large power dissipation. ILFDs are gaining popularity in recent years because they can reach higher operating frequencies and in the meantime dissipate less power<sup>[3]</sup>. Unfortunately, the ILFD has a narrow operating range and, more important, such a small operating range is also impacted by many factors, including the injected power and process variations.

In order to enhance the locking range of ILFDs and to extend their application potential, we propose in this paper a wide-locking-range ILFD, which is aiming at application in the frequency synthesizers for the high band groups (Group #3, #4, #5) of UWB systems. By utilizing both DCCA tuning together with varactor tuning and the dual-injection topology, the locking range of the presented ILFD is extended significantly. The principle of the injection locking and the concept of the proposed circuits are described and analyzed in detail, and the measurement results and a comparison with recently reported frequency dividers are also presented.

# 2. Principle of injection locking

## 2.1. Injection locking

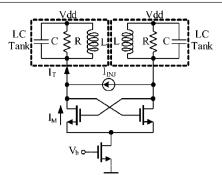

Injection locking is a special type of forced oscillation in nonlinear oscillators. For a given free-running oscillator, either ring oscillator or LC tank-based oscillator, when perturbed by an external signal, its output frequency changes to that of the external signal when their frequencies are close. This concept can be illustrated with an LC oscillator perturbed by a small signal  $I_{\text{INJ}}$  having frequency  $\omega_{\text{INJ}}$ , as shown in Fig. 1<sup>[4]</sup>. In the absence of the injected signal, the oscillator oscillates at its free-running frequency  $\omega_0 = 1/\sqrt{\text{LC}}$  and the current through the metal-oxide-semiconductor (MOS) transistors  $I_{\text{M}}$  is equal

Project supported by the National Program of the 11th 5-Year-Plan (No. 51308020403) and the IC Design Program of the Shanghai Science Committee (No. 08706200700).

<sup>†</sup> Corresponding author. Email: li\_ning@fudan.edu.cn Received 14 October 2008, revised manuscript received 19 November 2008

Fig. 1. LC oscillator under injection.

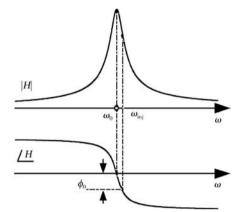

Fig. 2. Amplitude and phase of the LC tank impedance.

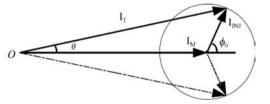

Fig. 3. Phasor diagram of the current signals in the LC oscillator.

to the tank current  $I_{\rm T}$  in both amplitude and phase. When a small signal  $I_{\rm INJ}$  with frequency  $\omega_{\rm INJ} \approx \omega_0$  is injected, it produces a phase difference between  $I_{\rm M}$  and  $I_{\rm INJ}$ . This forces the LC tank to oscillate at  $\omega_{\rm INJ}$  to contribute the necessary phase shift  $\phi_0$  in order to maintain  $\vec{T}_{\rm T} = \vec{T}_{\rm INJ} + \vec{T}_{\rm M}$ , as shown in Fig. 2.

#### 2.2. Locking range analysis

In order to investigate the locking range (the range of  $\omega_{INJ}$  across which injection locking holds), we plot the phasor diagram of the signals in the oscillator in Fig. 3. The total current entering the tank,  $I_T$ , now has two components after signal injection: one is due to the transconductor current produced by the cross-coupled transistors, and the other is injected. Once the oscillator is locked to the injected frequency, the angle  $\theta$  between the total tank current,  $I_T$ , and the transconductor current,  $I_M$ , must be equal to the phase shift created by the LC tank due to the shift of the oscillation frequency from  $\omega_0$  to  $\omega_{INJ}$ . When  $\omega_{INJ}$  moves away from  $\omega_0$ , to compensate for the increasingly greater phase shift introduced by the tank,  $\theta$  must also increase and it can be shown from Fig. 3 that,

$$\sin \theta = \frac{I_{\rm INJ}}{I_{\rm T}} \sin \phi_0 = \frac{I_{\rm INJ} \sin \phi_0}{\sqrt{I_{\rm INJ}^2 + I_{\rm M}^2 + 2I_{\rm M} I_{\rm INJ} \cos \phi_0}}, \quad (1)$$

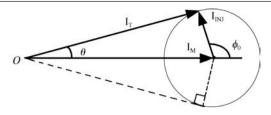

Fig. 4. Phasor diagram for maximum  $\theta$ .

Fig. 5. Conventional divide-by-two ILFD.

which reaches a maximum of,

$$\sin \theta_{\text{max}} = \frac{I_{\text{INJ}}}{I_{\text{M}}}$$

when  $\cos \phi_0 = -\frac{I_{\text{INJ}}}{I_{\text{M}}}$

As depicted in Fig. 4, this condition translates to a 90° angle between the total current  $I_{\rm T}$  and  $I_{\rm INJ}$ . Then we get the following relations,

$$\tan \theta = \frac{I_{\rm INJ}}{I_{\rm T}} \text{ and } I_{\rm T} = \sqrt{I_{\rm M}^2 - I_{\rm INJ}^2}.$$

(2)

To calculate the value of  $\omega_{INJ}$  in this case, we should first note the expression of phase shift  $\theta$  introduced by the LC tank, which is given in Ref. [5] as

$$\tan\theta \approx \frac{2Q}{\omega_0}(\omega_0 - \omega_{\rm INJ}),\tag{3}$$

where Q is the quality factor of the LC tank. Combining Eqs. (2) and (3), we can obtain the locking range as

$$2|\Delta\omega| = \frac{\omega_0}{Q} \frac{1}{\sqrt{(I_{\rm M}/I_{\rm INJ})^2 - 1}}.$$

(4)

Therefore, equation (4) reveals critical insights for the design of an ILFD: either increasing the injection current  $I_{INJ}$  or reducing the quality factor of the LC tank can effectively enhance the locking range of the ILFD.

#### 2.3. Divide-by-two ILFD

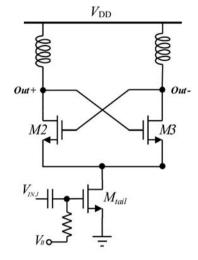

Injection locking can be used for frequency division when the signal is injected into the harmonic node of an oscillator. Figure 5 shows a conventional ILFD, where the signal is injected into the second harmonic node of the oscillator through a tail transistor. With proper amplitude and frequency,

Fig. 6. Direct-injection divide-by-two ILFD.

Fig. 7. Schematic of the proposed ILFD.

the input signal can lock the resonate frequency at exactly onehalf of its own frequency. The 3-GHz 1.2-mW CMOS divideby-two ILFD was reported with a 370-MHz locking range in Ref. [6].

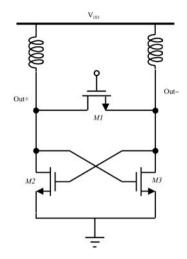

Such a small locking range is obviously a drawback for an ILFD, and several techniques were proposed to enhance its locking range. Among them, the direct injection technique is the most promising and widely adopted one, as shown in Fig. 6<sup>[7]</sup>. Since the output signals are locked directly by the input signal through the switch M1, the signal injection efficiency is significantly enhanced. The 15-GHz 23-mW CMOS ILFD using direct injection achieves a locking range of 3 GHz. This paper presents a wide-locking-range ILFD using a novel dual-injection technique together with DCCA tuning, for which the measured locking range is 4.85 GHz from 6.23 to 11.08 GHz. Using a 1.8-V power supply, the proposed ILFD consumes only 3.7 mA of current.

## 3. Circuit design

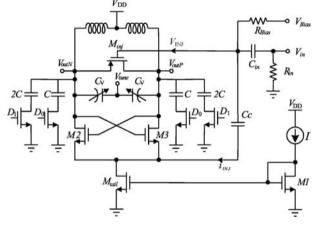

Figure 7 shows the schematic of the proposed ILFD. The oscillator core consists of a cross-coupled transistor pair M2-M3 to provide the negative impedance needed for sustained oscillation. A center-tapped spiral inductor was realized in metal layer 6 to resonate with the tank capacitances. The simulated

Fig. 8. Chip photograph of the ILFD.

values for the inductance and  $Q_L$  at 5 GHz are 0.9 nH and 10, respectively. The value we chose for the inductor was relatively small since  $Q_L$  should be decreased to achieve a wider locking range according to Eq. (3). However, such a degradation of  $Q_L$  entails higher tank losses which lead to an increase of power consumption. Therefore, a trade-off has to be made between locking range and power consumption at this design stage.

The free-running frequency of the oscillator is tuned in our design by both varactors and DCCA to obtain a wide tuning range. Two varactors connected back-to-back in the tank are formed by the accumulation MOS (A-MOS) varactor and are controlled by the tuning voltage  $V_{tune}$ . In addition, 2 bits digital control signals (D0, D1) are employed to switch the fixed capacitor array with unit value of 216 fF, which largely extends the tuning range of the oscillator. The free-running frequency of the oscillator is designed at one-half of the targeted input center frequency of the ILFD, which is around 4.3 GHz.

To further extend the locking range of the ILFD, the dualinjection technique was used in the proposed circuit topology. As shown in Fig. 7, two injection paths were formed at the input: one is injected through the switch connecting the differential outputs and the other is injected into the oscillator's second harmonic node through a coupling capacitor  $C_{\rm C}$ . The additional current from the latter path can contribute a lot to the total injection current, which directly enhances the locking range based on Eq. (4).

### 4. Implementation and measurements

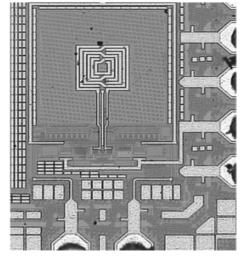

The ILFD was designed and fabricated in the Jazz 0.18- $\mu$ m RF 1P6M CMOS process. The photograph of the chip is shown in Fig. 8. The circuit occupies an area of 0.38 × 0.28 mm<sup>2</sup> (without pads), and draws a static current of 3.7 mA from the supply voltage of 1.8 V.

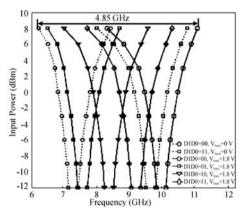

The performance of the designed ILFD was measured with an Agilent E8257D PSG 20-GHz analog signal generator, an E4440A PSA 26-GHz spectrum analyzer and an Infiniium DSO90000A oscilloscope. The measured sensitivity curve of the frequency divider is plotted in Fig. 9. The solid line and the dotted line are measured for a  $V_{tune}$  of 1.8 V and 0 V, respec-

Table 1. Performance comparison of the proposed ILFD with other ILFDs previously reported in the literature.

|           |                          |                    |                  |                  | 1                  | • •           |                     |

|-----------|--------------------------|--------------------|------------------|------------------|--------------------|---------------|---------------------|

|           | Technology               | $P_{\rm in}$ (dBm) | $V_{\rm DD}$ (V) | $P_{\rm diss}$ . | Area               | Locking range | Phase noise @ 1 MHz |

|           |                          |                    |                  | (mW)             | $(mm^2)$           | (GHz)         | offset (dBc/Hz)     |

| Ref. [7]  | $0.18 \mu m  CMOS$       | 7                  | 1.5              | 23               | $0.49 \times 0.47$ | 14.2–17.2     | NA                  |

| Ref. [8]  | $0.18\mu{ m m}{ m CMOS}$ | 0                  | 1.8              | 13.8             | NA                 | 1.2–7.4       | -130                |

| Ref. [9]  | $0.35 \mu m  CMOS$       | 10                 | 1.5              | 15.15            | $0.76 \times 0.78$ | 4.56-5.59     | -128                |

| Ref. [10] | $0.18 \mu m  CMOS$       | 10                 | 1.8              | 2.84             | NA                 | 4-8.2         | NA                  |

| Ref. [11] | 90 nm CMOS               | 5                  | 1.2              | 6.4              | $0.33 \times 0.08$ | 19.5-22.0     | -126.6              |

| Ref. [12] | $0.18 \mu m  CMOS$       | 5                  | 1.8              | 38               | $0.50 \times 0.53$ | 18.8–23.2     | -134.8              |

| This work | $0.18\mu{ m m}{ m CMOS}$ | 8                  | 1.8              | 6.6              | $0.38 \times 0.28$ | 6.5-11.08     | -137.9              |

Fig. 9. Measured sensitivity curve of the ILFD.

Fig. 10. Output spectrum at 7 GHz input.

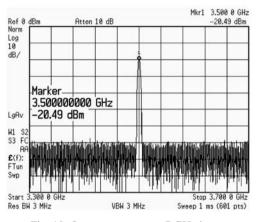

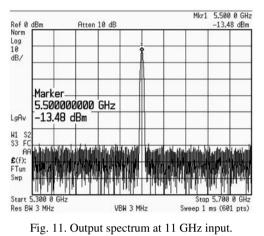

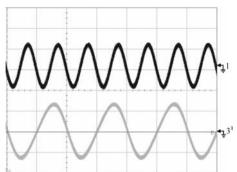

tively, with the control signals changing in incremental steps from D1D0 = 00 to D1D0 = 11. The entire locking range was measured at 4.85 GHz (from 6.23 to 11.08 GHz) with an input power of 8 dBm. Figures 10 and 11 show the measured output spectra for input signal frequencies of 7 and 11 GHz, respectively. It is noted that the output power at 3.5 GHz is much lower than that at 5.5 GHz, because the decrease of the oscillation frequency will reduce the equivalent resistance. The transient waveforms of a 10 GHz input and a 5 GHz output signals are plotted in Fig. 12.

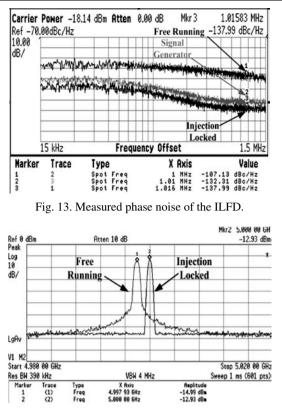

Figure 13 shows the measured phase noise performances of the proposed ILFD. The phase noise of the free-running oscillator at 1 MHz offset is about -107.3 dBc/Hz. After external signal injection, the phase noise of the ILFD is about -137.9dBc/Hz, while the input signal from the signal generator is 8 GHz with a phase noise of -132 dBc/Hz. The phase noise of the locked ILFD is lower than that of the free-running oscillator by 30 dB at an offset frequency of 1 MHz. Compared with

Fig. 12. Transient waveforms of input and output signals.

its injection source, the ILFD shows a 6 dB improvement at low offset frequency. This has been verified by different carrier frequencies from 7 to 11 GHz. A 6 dB phase noise reduction has been found, as shown in Fig. 13. This is in good agreement with theoretical predictions for an ideal divide-by-two frequency divider. Figure 14 intuitively compares the phase noise performance between a free-running and an injectionlocked divider for an injection signal of 10 GHz from a spectrum perspective.

Table 1 presents the performance comparison between the proposed ILFD and several recently published ILFDs.

# **5.** Conclusion

This paper presents the design and implementation of an ILFD in a 0.18  $\mu$ m RF CMOS process. At a supply voltage of 1.8 V, the power consumption of the proposed ILFD is only 6.6 mW. With the assistance of tuning methods and injection efficiency enhancement, the proposed ILFD achieves a locking range of 4.85 GHz from 6.23 to 11.08 GHz at an input

Fig. 14. Comparison of the output spectra for a free-running and an injection-locked divider.

power of 8 dBm. Such a wide locking range together with the low power consumption makes it possible for the ILFD to be applied in frequency synthesizers for the high group bands of UWB systems.

## References

[1] Multi-band OFDM physical layer proposal for IEEE 802.15

task group 3a. IEEE P802.15 Working Group for Wireless Personal Area Networks, 2004

- [2] Jin J, Yu X P, Zhou J J, et al. Gigahertz range injection locked frequency dividers with band-width enhancement and supply rejection. Electron Lett, 2008, 17(44): 999

- [3] Cheng S F, Tong H T, Jose S M, et al. A fully differential lowpower divide-by-8 injection-locked frequency divider up to 18 GHz. IEEE J Solid-State Circuits, 2007, 42(3): 583

- [4] Chee Y H, Ali M N, Jan M R. An ultra-low-power injection locked transmitter for wireless sensor networks. IEEE J Solid-State Circuits, 2006, 41(8): 1740

- [5] Ahmad M, Mohammad E H, Rahim B, et al. The quadrature LC oscillator: a complete portrait based on injection locking. IEEE J Solid-State Circuits, 2007, 42(9): 1916

- [6] Rategh H R, Lee T H. Superharmonic injection-locked frequency dividers. IEEE J Solid-State Circuits, 1999, 6(34): 813

- [7] Tiebout M. A CMOS direct injection-locked oscillator topology as high-frequency low-power frequency divider. IEEE J Solid-State Circuits, 2004, 7(39): 1170

- [8] Chuang Y H, Jang S L, Lee S H. A wide band injection locked frequency divider with variable inductor load. IEEE Microw Wireless Components Lett, 2007, 17(6): 460

- [9] Jang S L, Lin C Y, Lee C F. A low voltage 0.35  $\mu$ m CMOS frequency divider with the body injection technique. IEEE Microw Wireless Components Lett, 2008, 7(18): 470

- [10] Jin J, Yu X P, Zhou J J, et al. Gigahertz range injection locked frequency dividers with band-width enhancement and supply rejection. Electron Lett, 2008, 17(44): 999

- [11] Shibasaki T, Tamura H, Kanda K, et al. 20-GHz quadrature injection-locked LC dividers with enhanced locking range. IEEE J Solid-State Circuits, 2008, 3(43): 610

- [12] Lin H Y, Hsu S H, Chan C Y, et al. A wide locking-range frequency divider for LMDS applications. IEEE Trans Circuits Syst, 2007, 9 (54): 750