# A single-inductor dual-output switching converter with average current mode control

Xu Weiwei(许伟伟)<sup>1</sup>, Zhu Xiaoting(朱潇挺)<sup>1</sup>, Hong Zhiliang(洪志良)<sup>1,†</sup>, and Killat D<sup>2</sup>

(1 State Key Laboratory of ASIC and System, Fudan University, Shanghai 201203, China) (2 Dialog Semiconductor, Kirchheim-Teck, Germany)

Abstract: An integrated single-inductor dual-output (SIDO) switching DC–DC converter is presented. The outputs are specified with 1.2 V/400 mA and 1.8 V/200 mA. A decoupling small signal model is proposed to analyze the multi-loop system and to design the on-chip compensators. An average current control mode is introduced with lossless, continuous current detection. The converter has been fabricated in a 0.25  $\mu$ m 2P4M CMOS process. The power efficiency is 86% at a total output power of 840 mW while the output ripples are about 40 mV at an oscillator frequency of 600 kHz.

Key words: DC-DC converter; single-inductor multiple-output; average current mode control; on-chip current detection

**DOI:** 10.1088/1674-4926/30/9/095012 **EEACC:** 2570

# **1. Introduction**

Portable applications usually need different supply voltages for different functional modules to minimize power consumption. The conventional way to generate N regulated output voltages is to use N independent converters. However, a more interesting and efficient solution is to use one converter with a single inductor to generate multiple outputs, which reduces the external components and saves cost and space.

In recent years, there have been several kinds of singleinductor multiple-output (SIMO) switching converters reported. The converters in Refs. [1,2] make use of timemultiplexing control, which can be seen as a combination of two independent discontinuous conduction modes (DCM). There is a freewheeling state of inductor current when distributing energy from one channel to the other, which causes two channels independent of each other to suppress the cross regulation. But these converters suffer from very large current ripples and dissipate energy during the freewheeling state. The converter in Ref. [3] employs ordered power-distributive control which has a main channel for compensation and other subchannels controlled just by comparators. This simplifies the control loop, but has a higher ripple and is only suited for small load currents. The solution in Ref. [4] adopts digital control for a separate regulation of common-mode and differential-mode output voltages. The cross regulation problem is partially compensated by sophisticated control schemes. However, due to the limitations of digital control, the dynamic performance of the converter is not satisfactory.

This paper presents the analysis and design of an average current mode controlled SIDO buck converter. Compared with other designs, this SIDO converter maintains the advantages of continuous conduction mode (CCM) and also achieves fast load response. The system architecture and control sequence are introduced. A decoupling small signal model is proposed and the system stability is investigated. Circuit implementation is addressed. The measurement results confirm the system design.

## 2. Architecture of SIDO buck converter

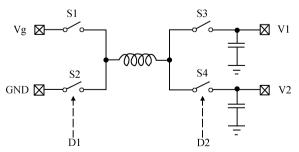

A conventional buck converter consists of two power switches and one inductor, which provide efficient power conversion. In a SIDO buck converter, the function of dual outputs is realized by adding another two switches at the output node of the inductor<sup>[5]</sup>. As shown in Fig. 1, there are four power transistors in the converter: two input switches S1 and S2, which regulate the total energy, and two output switches S3 and S4, which are used to share the energy in the inductor.

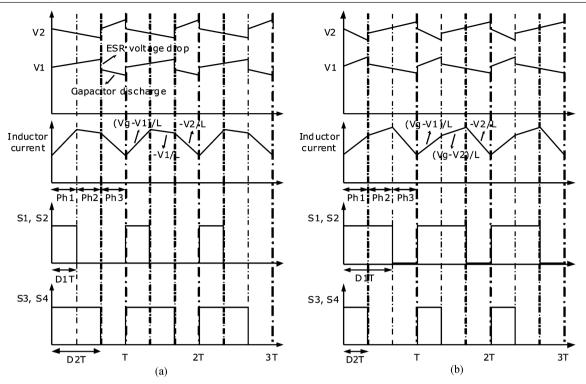

The control sequence is shown in Fig. 2. According to the switches' states, each period can be divided into three phases. Assuming the ripples and equivalent series resistors (ESRs) of the output capacitors are negligible, the power stage can be described by piecewise linear differential equations. By the time-averaging method, the equations are expressed as<sup>[4]</sup>:

Fig. 1. Power stage structure of a SIDO buck converter.

<sup>†</sup> Corresponding author. Email: zlhong@fudan.edu.cn Received 17 October 2008, revised manuscript received 17 April 2009

Fig. 2. Waveforms of output voltage ripples and inductor current with control signals: (a)  $D_1 < D_2$ ; (b)  $D_1 > D_2$ .

$$C_{1} \frac{d}{dt} v_{1} = i_{L} d_{2} - \frac{v_{1}}{R_{1}},$$

$$C_{2} \frac{d}{dt} v_{2} = i_{L} (1 - d_{2}) - \frac{v_{2}}{R_{2}},$$

$$L \frac{d}{dt} i_{L} = v_{g} d_{1} - v_{1} d_{2} - v_{2} (1 - d_{2}).$$

(1)

In steady state,  $\frac{d}{dt}\begin{bmatrix} v_1 & v_2 & i_L \end{bmatrix}^T = 0.$ So, the steady-state variables can be solved from Eq. (1).

$D_1$  is independent of load current, which is similar to of the situation in a conventional buck converter, while  $D_2$  is only related to the ratio of the two load currents.

There are two situations according to the relation of  $D_1$ and  $D_2$ . The slope of inductor current in Phase 2 is different in these two situations, which is labeled in Fig. 2. However, both control sequences can be unified into the description of Eq. (1), which means that they have the same behavior model. It will be analyzed below that the control loops of  $D_1$  and  $D_2$ can be regarded as independent of each other.

The waveforms of the steady-state inductor current and output voltage ripples in CCM are also depicted in Fig. 2. The ripples of SIDO output voltages mainly consist of two parts: the charge and discharge of capacitors and the voltage drop on the ESR of the capacitor. If the current ripple of the inductor is neglected, the output ripples in CCM can be estimated as:

$$V_{\text{ripple1}} = \Delta V_{\text{C1}} + \Delta V_{\text{ESR1}} = \frac{I_1(1 - D_2)T}{C_1} + I_{\text{L}}R_{\text{ESR1}}, \quad (2)$$

$$V_{\text{ripple2}} = \Delta V_{\text{C2}} + \Delta V_{\text{ESR2}} = \frac{I_2 D_2 T}{C_2} + I_{\text{L}} R_{\text{ESR2}}.$$

(3)

So, the steady-state voltage ripples depend on the discharge time and inductor current when switching S3 and S4. DCM and pseudo-CCM control in Refs. [1, 2] have longer discharging time and higher peak current, and thus have much larger ripples. However, due to the efficient usage of inductor current, which means there is no freewheel or idle state of inductor current, the control method shown in Fig. 2 has the advantages of low ripple and ability to sustain large load currents.

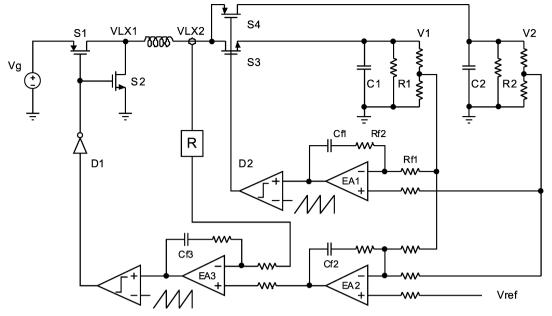

Voltage mode control is widely used in switching converters. It is simple, but requires large compensation components which are difficult for on-chip implementation<sup>[1]</sup>. Average current mode control exhibits the following important benefits<sup>[6]</sup>: (i) fast response which can partly suppress the cross regulation problem; (ii) easy compensation which can be realized by on-chip capacitors. Figure 3 illustrates the architecture of a SIDO converter with average current mode control.

In the SIDO converter system, there are two main control loops: the common-mode loop, which regulates the total energy by control signal  $D_1$ , and the differential-mode loop, which determines the distribution of inductor current between two output channels by control signal  $D_2$ . The common-mode and differential-mode voltages are defined as<sup>[4]</sup>:

$$V_{\rm CM} = m_1 V_1 + m_2 V_2,$$

$V_{\rm DM} = m_1 V_1 - m_2 V_2,$

(4)

where  $m_1$  and  $m_2$  are the feedback coefficients.

The converter is designed for an output load of 400 mA at 1.2 V on the first channel and 200 mA at 1.8 V on the second with an input voltage ranging from 2.8 to 5 V. The off-chip inductor is 4.7  $\mu$ H and the filter capacitors are 22  $\mu$ F. All compensation components are integrated on-chip.

Fig. 3. System architecture of the average current mode controlled SIDO buck converter.

## 3. System design of the SIDO buck converter

The SIDO converter demonstrates attractive advantages at the expense of more complicated system design. From Fig. 3, the converter works as a multi-loop feedback system so that the stability and dynamic response are the key problems. In this section the small signal model of the SIDO power stage is given. Based on the proposed decoupling model, the procedure for the compensator design is derived.

### 3.1. Small signal model

Based on Eq. (1), let  $x = X + \tilde{x}$ , where x, X and  $\tilde{x}$  are the average variable, steady state value and the small signal perturbation, respectively. Assuming the ripples and ESRs are negligible, the small signal behavior of the power stage can be described as:

$$\frac{d}{dt}\begin{bmatrix} \tilde{v}_{1}\\ \tilde{v}_{2}\\ \tilde{i}_{L} \end{bmatrix} = \begin{bmatrix} -\frac{1}{R_{1}C_{1}} & 0 & \frac{D_{2}}{C_{1}}\\ 0 & -\frac{1}{R_{2}C_{2}} & \frac{1-D_{2}}{C_{2}}\\ -\frac{D_{2}}{L} & -\frac{1-D_{2}}{L} & 0 \end{bmatrix} \begin{bmatrix} \tilde{v}_{1}\\ \tilde{v}_{2}\\ \tilde{i}_{L} \end{bmatrix} + \begin{bmatrix} 0 & \frac{I_{L}}{C_{1}}\\ 0 & -\frac{I_{L}}{C_{2}}\\ \frac{V_{g}}{L} & \frac{V_{2}-V_{1}}{L} \end{bmatrix} \begin{bmatrix} \tilde{d}_{1}\\ \tilde{d}_{2} \end{bmatrix}, \quad (5a)$$

$$\begin{bmatrix} \tilde{v}_{\mathrm{CM}}\\ \tilde{v}_{\mathrm{DM}}\\ \tilde{i}_{L} \end{bmatrix} = \begin{bmatrix} m_{1} & m_{2} & 0\\ m_{1} & -m_{2} & 0\\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} \tilde{v}_{1}\\ \tilde{v}_{2}\\ \tilde{i}_{L} \end{bmatrix}. \quad (5b)$$

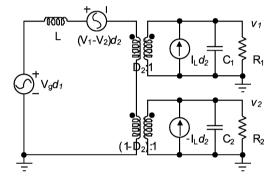

According to Eq. (5), the corresponding AC small signal model of SIDO power stage can be obtained (without consid

Fig. 4. AC small signal model of the SIDO power stage.

ering the variation of input voltage). It is shown in Fig. 4 that the averaged switching operation of S3 and S4 can be modeled as two transformers.

The SIDO converter in Fig. 3 is a multi-loop system which has several cross-regulated items. However, it is feasible to decompose the system into several single-loop subsystems to solve the stability problem<sup>[4]</sup>. Detailed analysis on the differential-mode and common-mode sub-systems will be derived.

#### 3.2. Differential-mode sub-system

When the common-mode loop is closed, the inductor behaves as a current source because of the average current mode control. Therefore, the approximated transfer function from  $\tilde{d}_2$  to  $\tilde{v}_{\rm DM}$  can be expressed as:

$$F_{\rm DM}(s) = I_{\rm L} \left( \frac{m_1 R_1}{1 + s R_1 C_1} + \frac{m_2 R_2}{1 + s R_2 C_2} \right). \tag{6}$$

Equation (6) gives us the valuable information that the power stage of the differential mode works as a first-order system whose dominant pole " $p_0$ " is related to the output capacitors and resistors. Based on this, the compensation of EA1 can be designed accordingly. Assuming the error amplifier is ideal with infinite gain, the transfer function of the proportional

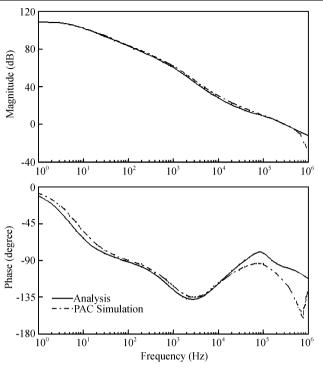

Fig. 5. Bode plots of the differential-mode sub-system.

integral compensator is

$$G_{\rm EA1}(s) = -\frac{1 + sR_{\rm f2}C_{\rm f1}}{sR_{\rm f1}C_{\rm f1}},\tag{7}$$

which has a pole " $p_1 = 0$ " and a zero " $z_1 = 1/R_{f2}C_{f1}$ ". Because of the limited area for on-chip capacitors and resistors,  $z_1$  is higher than  $p_0$ . For two poles at low frequency and zero compensation, large loop gain is needed to make the crossover frequency  $f_c$  much higher than  $z_1$ :

$$z_1 \ll 2\pi f_c \rightarrow R_{f2} \approx 1 \text{ M}\Omega, \ C_{f1} \approx 10 \text{ pF.}$$

(8)

The change of load resistors has little influence on the stability of the differential-mode loop. On the other hand, the maximum loop gain at the switching frequency is limited by the ramp slope of the sawtooth waveform to avoid sub-harmonic oscillation problems<sup>[6]</sup>.

$$|G_{\text{EA1}}(s)|_{\omega=2\pi f_{s}} < V_{\text{saw}} f_{s} \frac{C}{(m_{1}+m_{2})I_{1}},$$

(9)

where  $f_s$  is the switching frequency and  $V_{saw}$  is the voltage of the sawtooth waveform. Equation (9) decides the value of  $R_{f2}/R_{f1}$ .

A bode plot of the periodic AC (PAC) simulation in Spectre is shown by the dashed line in Fig. 5 (when  $V_g = 4 \text{ V}$ ,  $R_1 = 3 \Omega$ ,  $R_2 = 9 \Omega$ ), which demonstrates a phase margin of 85° and a crossover frequency of 145 kHz. From the bode plot, it is informed that the loop gain is important for stability and response.

#### 3.3. Common-mode sub-system

When the differential-mode loop is closed, according to the state space equation (5) and small signal model in Fig. 4,

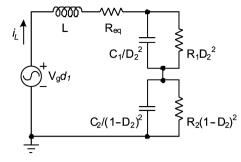

Fig. 6. AC decoupling model of the common-mode power stage.

the approximated transfer function from  $d_1$  to  $\tilde{i}_L$  and  $\tilde{v}_{CM}$  is given by:

$$F_{\rm CMi}(s) = \frac{V_{\rm g}}{sL + \frac{(D_2)^2 R_1}{1 + sR_1C_1} + \frac{(1 - D_2)^2 R_2}{1 + sR_2C_2} + R_{\rm eq}},$$

(10)

$$F_{\rm CMv}(s) = \left[\frac{m_1(D_2)^2 R_1}{1 + sR_1C_1} + \frac{m_2(1 - D_2)^2 R_2}{1 + sR_2C_2}\right] F_{\rm CMi}(s), \quad (11)$$

with  $R_{\rm eq} \approx \frac{V_2 - V_1}{I_{\rm L}} \left( D_2 - \frac{m_2}{m_1 + m_2} \right)$ . Equations (10) and (11) show that the power stage

Equations (10) and (11) show that the power stage of the common-mode sub-system behaves as a normal buck converter with the resonance frequency  $w = \sqrt{[D_2^2 + (1 - D_2)^2]/LC}$ . The closed-loop effect of the differential mode acts as an extra series resistor  $R_{eq}$ . The equivalent model is illustrated in Fig. 6.

Based on this conclusion, the compensation of the common-mode sub-system can be designed. Average current mode control is adopted to achieve good dynamic performance. The design of current mode control has been studied extensively in the literature<sup>[6,7]</sup>. There are also two control loops in the sub-system: the current loop and the voltage loop. The configurations of these two loops have been discussed in Ref. [8]. The inductor behaves as a current source in current mode control. Thus the compensation of the voltage loop is similar to that of the differential-mode loop ( $C_{f2} \approx 10$  pF), whose dominate pole in the power stage is related to the filter capacitors and load resistors.

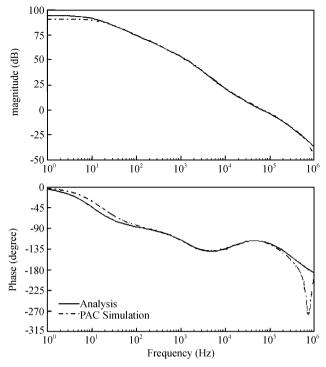

Figure 7 gives the outer loop simulation of the commonmode sub-system with current loop closed, which shows a phase margin of 52° and a crossover frequency of 120 kHz (when  $V_g = 4 \text{ V}$ ,  $R_1 = 3 \Omega$ ,  $R_2 = 9 \Omega$ ). Due to the current mode control, the system stability is insensitive to changes in load<sup>[8]</sup>.

#### 4. Circuit implementation

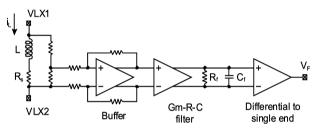

Average current mode control has the advantage of good stability and fast response, but it needs the information of the inductor current. Existing on-chip current detection techniques include using a series sensing resistor or mirror transistor<sup>[9]</sup>. However, they undergo problems of power loss, only half a side of inductor current, and inaccurate match on layout. Here a lossless, continuous, filter-based current detection method<sup>[10]</sup> is used. As shown in Fig. 8, the inductor current is sensed by filtering the voltage across the inductor.

Fig. 7. Bode plots of the common-mode sub-system.

Fig. 8. Diagram of a filter-based inductor current detector.

So, the output of this current detector can be expressed as:

$$V_{\rm F}(s) = V_{\rm L}(s)H(s) = I_{\rm L}(s)(sL + R_{\rm s})\frac{g_{\rm m}R_{\rm f}}{1 + sR_{\rm f}C_{\rm f}}K.$$

(12)

Actually it is not necessary to make the pole of the filter exactly equal to the zero of the inductor because the current loop only affects the system stability at high frequency<sup>[8]</sup>. Thus, Equation (12) can be written as:

$$V_{\rm F}(s)|_{\rm f\uparrow} = I_{\rm L}(s)\frac{g_{\rm m}L}{C_{\rm f}}K.$$

(13)

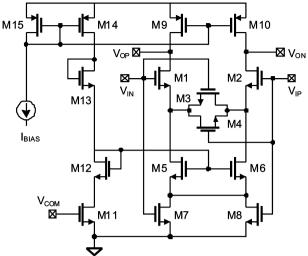

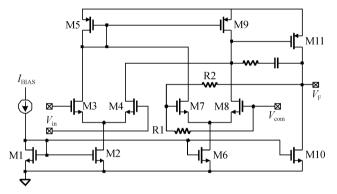

Therefore, the filter is feasible for on-chip implementation ( $C_f = 5 \text{ pF}$ ). In the SIDO converter, both sides of the inductor have switches, which gives rise to a large common mode noise at the input of the filter. The differential  $g_m$ opamp in Fig. 9 is used to suppress this noise<sup>[11]</sup>. The transconductance  $g_m$  is adjusted by transistors M3 and M4, which work as linear resistors.

A four-input-terminal two-stage opamp is used for differential-to-single-end conversion. The schematic is given in Fig. 10, which has high input impedance, and it is easy to adjust the gain and common mode voltage.

Fig. 9. Schematic of the full-differential  $g_m$  opamp.

Fig. 10. Schematic of a differential-to-single-end conversion circuit.

Fig. 11. Die micrograph of the SIDO chip.

#### 5. Measurement results

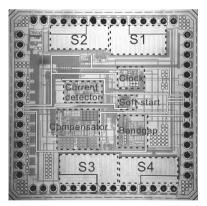

The SIDO converter was fabricated on a 0.25  $\mu$ m 2P4M CMOS process. The die micrograph is shown in Fig. 11. The chip area is 2.2 × 2.2 mm<sup>2</sup> with all pads.

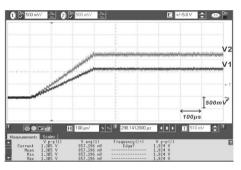

Figure 12 depicts the soft start process with the input voltage 4 V and load currents  $I_1 = 400$  mA,  $I_2 = 200$  mA. The output voltages ramp up smoothly in about 250  $\mu$ s. Both output voltages are stable with  $V_1 = 1.2$  V and  $V_2 = 1.8$  V.

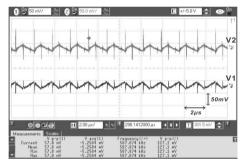

Figure 13 shows the detailed waveform of the ripples of two outputs, which correlates well with that from the analysis. The ripples are about 40 mV at a frequency of 600 kHz. It can be clearly seen that large glitches occur at the transition between output switches S3 and S4. The discontinuous current

| Parameter               | Ma <sup>[1]</sup> | Ma <sup>[2]</sup> | Trevisan <sup>[3]</sup> | Bonizzoni <sup>[4]</sup> | This work    |

|-------------------------|-------------------|-------------------|-------------------------|--------------------------|--------------|

| Process                 | 0.5 μm 1P3M       | 0.5 μm 1P3M       | FPGA                    | 0.35 µm 1P3M             | 0.25 μm 2P4M |

| Inductor (µH)           | 1                 | 1                 | 5                       | 22                       | 4.7          |

| Capacitors (µF)         | 33/40             | 33                | 10                      | 35                       | 22           |

| Oscillator (MHz)        | 1                 | 1                 | 0.5                     | 1                        | 0.6          |

| Efficiency (max)        | 88%               | 89%               | N/A                     | 93%                      | 95%          |

| Output voltage (V)      | 3.0/3.6           | 2.5/3.0           | 0.9–1.5                 | 1.2–Vbat                 | 1.2/1.8      |

| Load current (max) (mA) | 75/75             | 120/100           | 500/500                 | 200 (total)              | 400/200      |

| Output ripple (mV)      | 35/30             | 20/25             | 60/50                   | 31/24                    | 40/40        |

| Control method          | Voltage mode      | Voltage mode      | Digital PWM             | Voltage mode             | Current mode |

Table 1 Performance comparison of SIDO switching converters

Fig. 12. Output voltages of the soft start test.

Fig. 13. Ripples of two output voltages.

Fig. 14. Load response:  $I_1 = 400 \text{ mA}$ ,  $I_2 = 200 \text{ mA} \longrightarrow 0.1 \text{ mA}$ .

on the filter capacitor is the root cause of these glitches.

The converter efficiency at full load is 86%. The performance comparison of the SIDO switching converters is summarized in Table 1. Considering the output ripples are related to load currents, this SIDO converter shows the advantages of low ripple and fast response.

## 6. Conclusion

This paper presents an average current mode controlled SIDO buck converter. The system stability was investigated

and the decoupling analysis of this multi-loop system was proposed. A lossless, continuous filter-based current detector was used. Measurements on a test chip demonstrated low ripple, fast response and high efficiency. The SIDO converter is suitable for cost-effective power management of portable electronics.

## References

- Ma D, Ki W H, Tsui C Y, et al. Single-inductor multiple-output switching converters with time-multiplexing control in discontinuous conduction mode. IEEE J Solid-State Circuits, 2003, 38(1): 89

- [2] Ma D, Ki W H, Tsui C Y. A pseudo-CCM/DCM SIMO switching converter with freewheel switching. IEEE J Solid-State Circuits, 2003, 38(6): 1007

- [3] Le H P, Chae C S, Lee K C, et al. A single-inductor switching DC-DC converter with five outputs and ordered powerdistributive control. IEEE J Solid-State Circuits, 2007, 42(12): 2706

- [4] Trevisan D, Mattavelli P, Tenti P. Digital control of singleinductor dual-output DC-DC converters in continuous conduction mode. IEEE 36th Power Electronics Specialists Conference, 2005: 2616

- [5] Ki W H, Ma D. Single-inductor multiple-output switching converters. IEEE Proc Power Electronics Specialists Conf, 2001, 1: 226

- [6] Dixon L. Average current mode control of switching power supplies. Unitrode Power Supply Design Handbook, 1990

- [7] Sun C, Lehman B. Discussions on control loop design in average current mode control. IEEE Industry Applications Conference, 2000: 2411

- [8] Ridley R B, Cho B H, Lee F C Y. Analysis and interpretation of loop gains of multiloop-controlled switching regulators. IEEE Trans Power Electron, 1998, 3(4): 489

- [9] Lee C F, Mok P K T. A monolithic current-mode CMOS DC DC converter with on-chip current sensing techniques. IEEE J Solid-State Circuits, 2004, 39: 3

- [10] Dallago E, Passoni M, Sassone B. Lossless current sensing in low-voltage high-current DC/DC modular supplies. IEEE Trans Industrial Electron, 2000, 47(6): 1249

- [11] Raisanen-Ruotsalainen E, Lasanen K, Siljander M. A lowpower 5.4 kHz CMOS gm-C bandpass filter with on-chip center frequency tuning. IEEE International Symposium on Circuits and Systems, 2002: 651