Vol. 29 No. 11

# The Bipolar Field-Effect Transistor: VI. The CMOS Voltage Inverter Circuit (Two-MOS-Gates on Pure-Base) \*

Jie Binbin<sup>1,†</sup> and Sah Chih-Tang<sup>1,2,3,†</sup>

(1 Peking University, Beijing 100871, China) (2 University of Florida, Gainesville, Florida 32605, USA) (3 Chinese Academy of Sciences, Foreign Member, Beijing 100864, China)

Abstract: This paper reports the DC steady-state voltage and current transfer characteristics and power dissipation of the Complimentary Metal-Oxide-Silicon (CMOS) voltage-inverter circuit using one physical Bipolar Field-Effect Transistor (BiFET) of nanometer dimensions. The electrical characteristics are numerically obtained by solving the five partial differential equations for the transistor structure of two MOS-gates on the two surfaces of a thin pure silicon base layer with electron and hole contacts on both ends of the thin base. Internal and CMOS boundary conditions are used on the three potentials (electrostatic and electron and hole electrochemical potentials). Families of curves are rapidly computed using a dual-processor personal computer running the 64-bit FORTRAN on the Windows XP operating system.

Key words: bipolar field-effect transistor theory; surface channel; volume channel; CMOS inverter; CMOS-BiFET

**PACC:** 7340Q EEACC: 2560S; 2560B CLC number: TN386.1 Document code: A

Article ID: 0253-4177(2008)11-2079-09

### Introduction

Field-effect transistor (FET) was the intended name coined by Shockley and Pearson in their unsuccessful experiment 60 years ago in 1948 to obtain conductivity modulation of a silicon film by the application of a perpendicular electric field<sup>[1]</sup>. Conductivity modulation was used first by Lilienfeld 80 years ago in his field-effect transistor patents filed in 1926 and 1928<sup>[1]</sup>. Only one charge carrier type, the electrons, was considered. Also, only one region, the volume of the semiconductor, was considered. Lilienfeld did not know surface channel and electronic states on the surface. Shockley and Pearson failed because of them. In addition, only drift current was considered. These two earlier restrictions or limitations (one carrier type and one conduction region, the volume) were continued by Shockley 55 years ago in 1952 in his invention of the volume-channel field-effect transistor using p/ n junction gates to change the width of the volume channel and hence the conductance modulation of the volume channel, rather than conductivity modulation of the surface channel from changing the carrier concentration in the surface channel<sup>[1]</sup>. Shockley also stated explicitly, in the title of his 1952 invention paper, that it is unipolar, i. e. only the electrons or the holes are changed to give the modulation of conductance of the volume channel. Nevertheless, technology advances had enabled the manufacturing of electrical circuits using field-effect transistors with the MOS gate to control the conductivity of silicon surface, but still only either the electron or the hole channel on the surface under the gate oxide[1]. It was then reported in 1963 by Wanlass, Sah and Moore<sup>[2,3]</sup> that a very desirable (low power dissipation) voltage inverter can be obtained by connecting an unipolar p-surfaceinversion-channel MOS field-effect-transistor in series with an unipolar n-surface-inversion-channel MOS field-effect-transistor. It was recognized only 18 months ago in March 2007 from the experimental data of nanometer MOS field-effect transistors[4,5] that six current components can be simultaneously present in one physical field-effect transistor, which are: electron and hole channels, on the surface and volume of the semiconductor, and diffusion and drift. Electronhole generation-recombination-trapping is not included but is another, solely bipolar, mechanism. Thus, field-effect transistors are inherently bipolar (Bi-FET), although some of the bipolar currents can be suppressed by proper device design, but not eliminated. It was immediately recognized by us [4,5], based on our previous experiences<sup>[6]</sup>, that the bipolar nature

<sup>\*</sup> This investigation and Jie Binbin have been supported by the CTSAH Associates (CTSA), founded by the late Linda Su-Nan Chang Sah, in memory of her 70th year.

<sup>†</sup> Corresponding author. Email: bb\_jie@msn. com and tom\_sah@msn. com Received 23 October 2008, revised manuscript received 28 October 2008

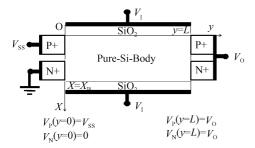

Fig. 1 The configuration of a BiFET with two MOS gates and a pure base under the CMOS voltage inverter circuit operation.

can be used to advantage for realizing of a circuit function in just one BiFET<sup>[4,5]</sup> such as the CMOS voltage inverter and the SRAM memory, which could give a factor of two jump of the Moore's law with existing technology. In this paper, we report for the first time, the calculated CMOS voltage inverter characteristics from one physical MOS BiFET, that were described earlier<sup>[4,5]</sup>.

## 2 CMOS Voltage Inverter Circuit Bias Configuration and Theory

Figure 1 shows the cross-sectional view of a nanmetal-oxide-silicon field-effect-transistor (MOSFET) with two identical MOS gates on a pure silicon base to illustrate the DC bias configuration for the voltage inverter circuit operation using one physical 2-MOS-gates Bipolar Field Effect transistor (Bi-FET). The physical realization of the voltage inverter function using two physical 1-MOS-gate Unipolar Field-Effect transistors (UniFET) had been reported by Wanlass, Moore and Sah some 45 years ago in  $1963^{[1\sim3]}$ . The two transistors of 1-MOS-gate had the two opposite base conductivity types and gate-voltageinduced surface inversion channels, the n-channel or electron-channel on the p-base and the p-channel or hole channel on the n-base. They coined this 2-transistor circuit in 1962 as the Complimentary Metal-Oxide-Silicon (CMOS) voltage inverter circuit. It was recently taught, in 1991, to college sophomore students as one of the two Basic Building Block (BBB) circuit<sup>[7]</sup>.

For this new 1-transistor BiFET CMOS voltage inverter, the contacts to the two ends of the pure-base layer, as schematically illustrated in Fig. 1, are the unique specialty of this first circuit realization of the CMOS voltage inverter by one 2-gate BiFET, namely, these contacts are the source and drain (or sink) of electrons and holes, such as the two electrically isolated semiconductor junctions, the p + Drain/pure-Base and n + D/pure-Base junctions for the two drain contacts and the p + Source/pure-Base and n + Source/pure-Base junctions for the two source contacts. For

our numerical computations, these contacts are assumed to cover the entire width and thickness of the two ends of the base layer or base sheet so that both electron and hole surface and volume channels are simultaneously present and conducting, which give the maximum geometry current. Such topology generalization offers device designers ingenuities to localize the current-carrying channels, hence quiescent state currents and power dissipation, and also peak switching current. To avoid symbol conflict between pure-Si and p-type-Si, we shall use the term intrinsic-Si or i-Si to denote pure-Si. Thus, these contacts to the purebase layer are the p + D/i-B and n + D/i-B junctions. We recognize that the term "intrinsic" covers much broader conditions than "pure", such as an impure and a defective silicon at a sufficiently high temperature that the intrinsic carrier concentration is much higher than the chemical impurity and physical defect concentrations,  $n_i \gg |N_{\rm DD} - N_{\rm AA}|$  and  $n_i \gg N_{\rm TT}^{[7]}$ .

For the CMOS voltage inverter, the two drain contacts, n + D/i-B and p + D/i-B, are tied together by a metallic short circuit such as the interconnect conductor metal, and this serves as the output terminal node, with the terminal voltage or output voltage designated by  $V_{DB} \equiv V_{OB} \equiv V_{O}$  where B is the referencenode of the applied voltage. The DC power supply voltages, 0 and  $V_{ss}$ , are applied to the two electrically isolated source contacts, with a positive voltage  $V_{\rm ss}>$ 0 applied to the p + S/i-B contact,  $V_{p+SB} = V_{SS} > 0$ , and a negative voltage or zero reference applied to the n + S/i-B contact,  $V_{n+SB} = V_{BB} \le 0$ . In our analysis, we use the asymmetrical or positive supply voltage, thus,  $V_{\rm BB}$  = 0. For balanced case, we would have  $V_{\rm BB}$  = -  $V_{\rm ss}$ . The two MOS gates are identical, i. e. with the same threshold voltage, and they are tied together to serve as the input terminal with the input voltage,  $V_{\rm I}$  $\equiv V_{\rm GB}$ . This CMOS bias configuration gives the following boundary conditions of the quasi-Fermi potentials of the MOS BiFET. In the mathematical analysis and numerical computations, all the potential variables, both internal and at the terminals, are normalized to the thermal voltage,  $k_B T/q$ , i. e.  $U_N = qV_N/q$  $k_{\rm B}T$ ,  $U_{\rm P} = qV_{\rm P}/k_{\rm B}T$  and  $U_{\rm IR} = qV_{\rm IR}/k_{\rm B}T$ , where I is electric potential represented by the intrinsic Fermi potential, R = Reference potential node,  $k_B$  = Boltzmann constant and T = lattice or thermal phonon temperature. Then, in the not-normalized forms, the boundary values are:

$$V_{\rm N}(y=0) = V_{\rm BB} = 0, V_{\rm P}(y=0) = V_{\rm SS}$$

(1)

$$V_{\rm N}(y=L) = V_{\rm P}(y=L) = V_{\rm OUTPUT} \equiv V_{\rm O}$$

(2)

The DC electrical characteristics are governed by three DC steady-state Shockley equations (Poisson and Electron and Hole Current Continuity Equations) with no electron-hole-generation-recombination-trapping. Five simultaneous DC MOS transistor equations were derived from the three Shockley equations  $^{[8]}$ , with the previously justified assumptions on (i) the x-independence of the electron and hole electrochemical potentials, (ii) the constancy and near thermal

equilibrium of the electron and hole mobilities and diffusivity,  $D_n$  (x, y, z, t,  $V_N$ ,  $V_P$ , V, T)  $\equiv D_n \equiv (k_B T/q)\mu_n$  for electrons and similarly for holes, and (iii) the omission of 2-dimential terms in the Poisson equation. These five equations are (Integration  $U = U_S$  to  $U_0$ ):

### The Voltage Equation:

$$U_{\rm GS} - U_{\rm S} = {\rm sign}(U_{\rm S} - U_{\rm 0}) \times (C_{\rm D}/C_{\rm O}) \times \left[\exp(U_{\rm S} - U_{\rm N}) - \exp(U_{\rm 0} - U_{\rm N}) + \exp(U_{\rm P} - U_{\rm S}) - \exp(U_{\rm P} - U_{\rm 0})\right]^{1/2}$$

(3) The Thickness Equation:

$$X_{\rm B} = 2 \int {\rm sign}(U - U_0) \partial_X U \div \left[ \exp(U - U_{\rm N}) - \exp(U_0 - U_{\rm N}) + \exp(U_{\rm P} - U) - \exp(U_{\rm P} - U_0) \right]^{1/2}$$

(4)

The Total Current Equation:

$$I_{N} = + qD_{n}n_{i}L_{D}(W/L)(\partial U_{N}/\partial Y)\exp(-U_{N})\int \exp(+U)\partial_{X}U \div \left[\exp(U-U_{N}) - \exp(U_{0}-U_{N})\right] + \exp(U_{P}-U) - \exp(U_{P}-U_{0})\right]^{1/2}$$

$$(5)$$

$$I_{P} = + qD_{p}n_{i}L_{D}(W/L)(\partial U_{P}/\partial Y)\exp(+U_{P})\int \exp(-U)\partial_{X}U \div \left[\exp(U-U_{N}) - \exp(U_{0}-U_{N}) + \exp(U_{P}-U) - \exp(U_{P}-U_{0})\right]^{1/2}$$

$$(6)$$

$$I_{\rm CH} = I_{\rm N} = -I_{\rm P} \tag{7}$$

The notations here are defined in [8] except that  $I_{\rm CH}$  is the channel current of the BiFET connected as the CMOS voltage inverter. The boundary or terminal values are:  $U_{\rm n+SR} = U_{\rm BR} = 0$ ,  $U_{\rm GR} = U_{\rm Gn+S} = U_{\rm GB} = U_{\rm INPUT} = U_{\rm I} = qV_{\rm I}/k_{\rm B}T$ , and  $U_{\rm DR} = U_{\rm Dn+S} = U_{\rm DB} = U_{\rm OUTPUT} = U_{\rm O} = qV_{\rm O}/k_{\rm B}T$ . Note subscript O here is for Output, not zero 0. In order to illustrate the device physics succinctly, we take  $D_{\rm n} = D_{\rm p} = D$  so that electron and hole are interchangeable.

It is very important to note a cardinal device physics feature in the CMOS voltage inverter application, that is, when both the input voltage and output voltages are forced to be at one half of the power supply voltage,  $U_{\rm I} = U_{\rm O} = U_{\rm ss}/2$ , the entire base region is at flatband, either a plane or a volume depending on solving the transistor as a 2-D or 3-D device. This flatband gives a very simple but most application important (maximum power dissipation solution) terminal

current-voltage equation, which, from symmetry considerations, is also the peak current that can flow in the two surface channels and one volume channel in the 2-MOS-gate BiFET in the CMOS voltage inverter circuit connection. Using this important feature, without and before solving the five simultaneous equations given above, the exact total (not area density) electron current,  $I_N$ , (which is the sum of its surface and volume channel currents, which we can also compute separately, if needed, by x-integration or U(x)-integration between the gate-oxide/base-silicon interface and defined surface/volume channel boundary) and the exact total hole current  $I_P$  at  $U_I = U_O = U_{SS}/2$  can be computed as follows where the device-physicsbased coordinate normalizations are given by  $X_{\rm B}$  =  $x_{\rm B}/L_{\rm D}$  and Y=y/L where  $L_{\rm D}$  is the Debye length in the pure base and L is the base length:

$$I_{N} = qD(Wx_{B})(N\partial U_{N}/\partial y) = qD(Wx_{B})n_{i} \times \exp(U_{SS}/2 - U_{N}) \times (\partial U_{N}/\partial y)$$

$$= qD(W/L)(n_{i}L_{D})X_{B} \times \exp(U_{SS}/2) \times \exp(-U_{N}) \times (\partial U_{N}/\partial Y)$$

$$I_{P} = qD(Wx_{B})(P\partial U_{P}/\partial y) = qD(Wx_{B})n_{i} \times \exp(U_{P} - U_{SS}/2)(\partial U_{P}/\partial y)$$

(8)

$$I_{P} = qD(WX_{B})(P\partial U_{P}/\partial y) = qD(WX_{B})n_{i} \times \exp(U_{P} - U_{SS}/2)(\partial U_{P}/\partial y)$$

$$= qD(W/L)(n_{i}L_{D})X_{B} \times \exp(U_{SS}/2) \times \exp(U_{P} - U_{SS}) \times (\partial U_{P}/\partial Y)$$

(9)

Using the boundary values of the electrochemical or quasi-Fermi potentials of electrons and holes given by (1) and (2) in the two total current equations given by (8) and (9)

$$U_{\rm N}(Y=0)=0$$

,

$$U_{\rm N}(Y=1)=U_{\rm P}(Y=1)=U_{\rm SS}/2 \text{ and } U_{\rm P}(Y=0)=U_{\rm SS}$$

, (10)

we obtain the exact channel current expression at  $U_1$  =  $U_0$  =  $U_{\rm SS}/2$  which is a very simple one, most appealing certainly for compact modeling purposes (We temporarily call this the CMOS Leakage Current

Peak Equation.):

$$I_{\text{CH}} = I_{\text{N}} = -I_{\text{P}} = (W/L)(qDn_{i}L_{\text{D}})X_{\text{B}} [\exp(U_{\text{SS}}/2) - 1]$$

(11)

This is also the peak current, a very important number in applications with the consideration of power dissipation in the integrated circuits containing many MOS transistors.

When the input voltage deviates from  $V_{\rm ss}/2$ , the output voltage and the channel current can only be obtained by numerically solving the simultaneous equations (3-7) with the boundary conditions (1-2).

It has been observed during our numerical calculation experiences, consistent with and expected from the well-known fact of the very steep or sharp-step in the voltage transfer characteristic of the CMOS voltage inverter circuit<sup>[7]</sup>, that when the input voltage is only slightly less or more than  $V_{\rm SS}/2$ , the output voltage is already very close to the power supply voltage or zero. The underlying device physics, readily proven by numerical calculations, is that when the input voltage is less than  $V_{\rm SS}/2$ , a hole surface channel is formed in series with an electron volume channel, since the hole surface channel has much higher conductivity, due to high surface hole concentration, than the electron volume channel which has only the very low intrinsic electron concentration, most of the power supply voltage drop occurs along the electron volume channel. Thus the output voltage is close to the power supply voltage. Similarly, when the input voltage is larger than  $V_{\rm ss}/2$ , a higher-conductivity electron surface channel is formed in series with the intrinsic-conductivity hole volume channel, most of the power supply voltage drop occurs along the hole volume channel, and thus the output voltage is close to the zero.

### 3 Analytical Solutions

### 3.1 Non-Recursive Solution

In order to obtain a fast numerical solution over

inverter application of the single Bipolar Field Effect transistor with 2-MOS gates, simplifications of the five simultaneous equations (3-7) must be made. (Thickness and purity of the base layer are only special considerations made here by us to simplify the illustration on how this circuit works; they are not the necessary conditions, i.e. the transistor could be thick and not very pure, i.e., then it would approach two 1gate bulk MOS transistors, and if for CMOS application, then the n-channel transistor and the p-channel transistor would require an abrupt or graded p/n junction or a buried oxide-or-insulator layer for isolation by dividing the base layer into two isolated base layers, but then without the most desirable consequences from the thin pure-base with simultaneous electron and hole surface and volume channels of our MOS Bi-FET.) To make these simplifications, four physical parameters are selected: (1) the surface potential at the source Y = 0,  $U_{so}$ , (2) the mid-plane potential at the source Y = 0,  $U_{00}$ , (3) the total (areal density) hole concentration at the source Y = 0,  $P_0$ , and (4) the total (areal density) electron concentration at the source Y = 0,  $N_0$ . They are computed from the following equations where the integration is from  $U = U_{00}$  to  $U_{\rm S0}$  .

the whole input voltage range of this CMOS voltage-

$$U_{I} - U_{S0} = \operatorname{Sign}(U_{I} - U_{SS}/2) \times (C_{D}/C_{O}) \times \left[ \exp(U_{SS} - U_{S0}) - \exp(U_{SS} - U_{00}) + \exp(U_{S0}) - \exp(U_{00}) \right]^{1/2} (12)$$

$$X_{B} = \operatorname{Sign}(U_{I} - U_{SS}/2) \times 2 \times \int \partial_{X} U \div \left[ \exp(U_{SS} - U) - \exp(U_{SS} - U_{00}) + \exp(U) - \exp(U_{00}) \right]^{1/2} (13)$$

$$P_{0} = \operatorname{Sign}(U_{I} - U_{SS}/2) \times 2 \times (n_{i}L_{D}) \times \int \exp(U_{SS} - U) \partial_{X} U \div \left[ \exp(U) - \exp(U_{00}) + \exp(U_{SS} - U) - \exp(U_{SS} - U) \right]^{1/2} (14)$$

$$- \exp(U_{SS} - U_{00}) \right]^{1/2} (14)$$

$$N_{0} = \operatorname{Sign}(U_{I} - U_{SS}/2) \times 2 \times (n_{i}L_{D}) \times \int \exp(U) \partial_{X} U \div \left[ \exp(U) - \exp(U_{00}) + \exp(U_{SS} - U) - \exp(U_{SS} - U) \right]^{1/2} (15)$$

When the input voltage is less than half of the power supply voltage, the output voltage is very close to the power supply voltage, thus the following approximations are made to simplify the hole and electron current integrals:

$$I_{P} = 2qDn_{i}W(L_{D}/L)\int(\partial_{Y}U_{P})\exp(+U_{P})\int\exp(-U)\partial_{X}U \div [\exp(U-U_{N}) - \exp(U_{0}-U_{N}) + \exp(U_{0}-U_{N}) - \exp(U_{P}-U_{0})]^{1/2}$$

$$\text{with integration ranges of } U_{P} = U_{SS} \text{ to } U_{O} \text{ and } U = U_{0} \text{ to } U_{S}$$

$$\approx 2qDn_{i}L_{D}(W/L)\int(\partial_{Y}U_{P})\exp(+U_{SS})\int\exp(-U)\partial_{X}U \div [\exp(U-0) - \exp(U_{00}-0) + \exp(U_{SS}-U) - \exp(U_{SS}-U_{00})]^{1/2}$$

$$\text{with integration ranges of } U_{P} = U_{SS} \text{ to } U_{O} \text{ and } U = U_{00} \text{ to } U_{SO}$$

$$= 2qDn_{i}L_{D}(W/L)(U_{O}-U_{SS})\int\exp(U_{SS}-U)\partial_{X}U \div [\exp(U) - \exp(U_{00}) + \exp(U_{SS}-U) - \exp(U_{SS}-U_{00})]^{1/2}$$

$$\text{with integration range of } U = U_{00} \text{ to } U_{SO}$$

$$I_{P} \approx + qD(W/L) \times (U_{SS}-U_{O}) \times P_{0}$$

$$(16)$$

$$I_{N} = 2qDn_{i}L_{D}(W/L) \times (\partial U_{N}/\partial Y)\exp(-U_{N})\int \exp(+U)\partial_{X}U \div [\exp(U-U_{N}) + \exp(U_{0}-U_{N}) + \exp(U_{P}-U) - \exp(U_{P}-U_{0})]^{1/2}$$

with integration range of  $U = U_{0}$  to  $U_{S}$

$$\approx 2qDn_{\rm i}L_{\rm D}(W/L)\times(\partial U_{\rm N}/\partial Y)\exp(-U_{\rm N})\Big[\exp(+U)\partial_XU\div[\exp(U-0)$$

$$-\exp(U_{00}-0) + \exp(U_{SS}-U) - \exp(U_{SS}-U_{00})]^{1/2}$$

with integration range of  $U = U_{00}$  to  $U_{S0}$

$$I_{N} \approx -qD(W/L)(\partial U_{N}/\partial Y)\exp(-U_{N}) \times N_{0}$$

(17)

Integrating (17) and using  $U_N(Y=0)=0$  and  $U_N(Y=1)=U_O$ , we get

$$1 - \exp(-U_0) = I_N \div \left[-qD \left(W/L\right) \times N_0\right] \tag{18}$$

Since  $I_{CH} = -I_P = I_N$ , combining (16) and (18)

$$1 - \exp(-U_0) = (U_{ss} - U_0) \times P_0 / N_0$$

(19)

Noting  $\exp(-U_0) \approx \exp(-U_{ss}) \ll 1$

$$U_{\rm ss} - U_{\rm o} = N_{\rm o}/P_{\rm o} \tag{20}$$

$$I_{\text{CH}} = qD(W/L) \times N_0 \tag{21}$$

When the input voltage is larger than half of the power supply voltage, the output voltage is very close to the zero voltage, thus the following approximations are made to simplify the electron and hole current integrals:

$$I_{N} = 2 q D n_{i} W(L_{D}/L) \int \partial_{Y} U_{N} \exp(-U_{N}) \int \exp(+U) \partial_{X} U \div [\exp(U-U_{N}) - \exp(U_{0} - U_{N}) + \exp(U_{P} - U) - \exp(U_{P} - U_{0})]^{1/2}$$

with integration ranges of  $U_{\rm N}=0$  to  $U_{\rm O}$  and  $U=U_{\rm 0}$  to  $U_{\rm S}$

$$\approx 2qDn_{i}L_{D}(W/L)\int \partial_{Y}U_{N}\exp(-0)\int \exp(+U)\partial_{X}U \div \left[\exp(U-0)-\exp(U_{00}-0)\right]$$

+

$$\exp(U_{SS} - U) - \exp(U_{SS} - U_{00})]^{1/2}$$

with integration ranges of  $U_{\rm N}=0$  to  $U_{\rm O}$  and  $U=U_{\rm 00}$  to  $U_{\rm S0}$

$$= 2 q D n_{i} L_{D}(W/L) \times U_{O} \times \left[ \exp(U) \partial_{X} U \div \left[ \exp(U) - \exp(U_{00}) + \exp(U_{SS} - U) - \exp(U_{SS} - U_{00}) \right]^{1/2} \right]$$

with integration range of  $U = U_{00}$  to  $U_{s0}$

$$I_{\rm N} \approx qD(W/L) \times U_{\rm O} \times N_{\rm 0} \tag{22}$$

$$I_{P} = 2qDn_{i}W(L_{D}/L)(\partial U_{P}/\partial Y)\exp(U_{P})\int \exp(-U)\partial_{X}U \div \left[\exp(U-U_{N}) + \exp(U_{0}-U_{N})\right] + \exp(U_{P}-U) - \exp(U_{P}-U_{0})$$

with integration range of  $U = U_0$  to  $U_s$

$$\approx 2qDn_{\rm i}L_{\rm D}(W/L)(\partial U_{\rm P}/\partial Y)\exp(U_{\rm P})\int\!\exp(-U)\partial_X U\,\div\left[\exp(U-0)-\exp(U_{\rm 00}-0)\right]$$

$$+\exp(U_{ss}-U)-\exp(U_{ss}-U_{00})]^{1/2}$$

with integration range of  $U = U_{00}$  to  $U_{80}$

$$= 2qDn_{i}L_{D}(W/L)(\partial U_{P}/\partial Y)\exp(U_{P}-U_{SS})\Big[\exp(U_{SS}-U)\partial_{X}U \div [\exp(U)-\exp(U_{00})]\Big]$$

$$+\exp(U_{SS}-U)-\exp(U_{SS}-U_{00})]^{1/2}$$

with integration range of  $U = U_{00}$  to  $U_{80}$

$$I_{P} \approx qD(W/L) \times (\partial U_{P}/\partial Y) \exp(U_{P} - U_{SS}) \times P_{0}$$

(23)

Integrating (23) and using  $U_P(Y=0) = U_{ss}$  and  $U_P(Y=1) = U_{os}$

$$\exp(U_0 - U_{ss}) - 1 = I_P / [qD(W/L) \times P_0]$$

(24)

Since  $I_{CH} = -I_P = I_N$ , combining (22) and (24)

$$\exp(U_{\rm O} - U_{\rm SS}) - 1 = -U_{\rm O} \times N_0 / P_0 \tag{25}$$

Noting  $\exp(U_0 - U_{ss}) \approx \exp(-U_{ss}) \ll 1$

$$U_0 = P_0/N_0 \tag{26}$$

$$I_{\text{CH}} = qD \left( W/L \right) \times P_0 \tag{27}$$

The equations (12-15), (20-21) and (26-27), taken together, is the non-recursive approximate solution of the BiFET in the CMOS voltage inverter bias configuration which are derived from the recursive exact solution given by the five simultaneous equations (3-7).

#### 3. 2 Close-Form Solution

It is obvious that the equations (12-15) for four physical parameters,  $U_{00}$ ,  $U_{80}$ ,  $P_{0}$ , and  $N_{0}$  are still sufficiently too complicated for compact modeling. The following derivation is to simplify these equations further by use of the Taylor series expansion. To make the algebra easy, the following variable transformations are made:

$$u_1 = U_1 - U_{SS}/2, u_S = U_{S0} - U_{SS}/2, u_0 = U_{00} - U_{SS}/2, u = U - U_{SS}/2$$

(28)

Equations (12-15) can then be rewritten as follows with the integration range of  $u = u_0$  to  $u_s$

$$u_{1} - u_{S} = \operatorname{Sign}(u_{1}) \times (C_{D}/C_{O}) \times \exp(U_{SS}/4) \times \left[\exp(-u_{S}) - \exp(-u_{0}) + \exp(u_{S}) - \exp(u_{0})\right]^{1/2}$$

(29)

$$X_{\rm B} = \operatorname{Sign}(u_{\rm I}) \times 2 \times \exp(-U_{\rm SS}/4) \left[ \partial_X u \div \left[ \exp(-u) - \exp(-u_{\scriptscriptstyle 0}) + \exp(u) - \exp(u_{\scriptscriptstyle 0}) \right]^{1/2} \right]$$

(30)

$$P_0 = n_1 L_D \times \text{Sign}(u_1) \times 2 \times \exp(U_{ss}/4) \int \exp(-u) \partial_x u \div [\exp(-u) - \exp(-u_0) + \exp(u) - \exp(u_0)]^{1/2}$$

(31)

$$N_0 = n_i L_D \times \text{Sign}(u_1) \times 2 \times \exp(U_{SS}/4) \int \exp(+u) \partial_X u \div [\exp(-u) - \exp(-u_0) + \exp(u) - \exp(u_0)]^{1/2}$$

(32)

The second order Taylor expansion gives:

$$\exp(-u) - \exp(-u_0) + \exp(u) - \exp(u_0) \approx u^2 - u_0^2$$

(33)

From the thickness equation (30),

$$X_{\rm B} \approx 4 \, \exp(-U_{\rm SS}/4) \times \left[ (u_{\rm S} - u_{\rm 0})/(2u_{\rm 0}) \right]^{1/2} \times \left[ 1 - (1/3)(u_{\rm S} - u_{\rm 0})/(4u_{\rm 0}) \right]$$

(34)

Let  $t = [(u_s - u_0)/(2u_0)]^{1/2} < 1$ , then (34) can be rearranged as follows:

$$t = (X_{\rm B}/4) \times \exp(U_{\rm SS}/4) + (1/6) \times t^3 \tag{35}$$

From the voltage equation (29),

$$u_0 \approx u_1 \div \left[ (C_D/C_0) \times \exp(U_{SS}/4) \times 2t \times (1+t^2)^{1/2} + 2t^2 + 1 \right]$$

(36)

The total (areal density) hole concentration, (31), is approximated by

$$P_0 \approx (n_i L_D) 4 \times \exp[(U_{SS}/4) - u_0] \times [1 - (1 + 0.25/u_0)/3 \times (2t^2 u_0)]t$$

(37)

From the total (areal density) electron concentration equation (32),

$$N_0 \approx (n_{\rm i} L_{\rm D})4 \times \exp[(U_{\rm SS}/4) + u_0] \times [1 + (1 - 0.25/u_0)/3 \times (2t^2 u_0)]t$$

(38)

The simplified approximation equations (35-38), (20-21), and (26-27) give a compact solution for the current-voltage and voltage-voltage characteristics of the 2-MOS-gate thin pure-base Bipolar Field-Effect transistor as wired for the CMOS voltage inverter operation.

## 4 Computed Transfer Characteristics

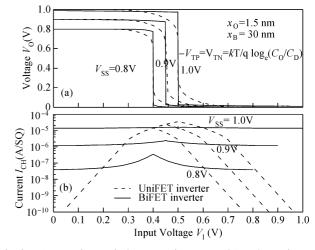

# 4. 1 Comparison of the 1-BiFET and 2-UniFET CMOS Voltage Inverters

It is very important for us to provide a comparison of this novel one-BiFET (1-Transistor or 1-T) CMOS voltage inverter with the two-UniFET (2-Transistor or 2-T) CMOS voltage inverter which was first demonstrated and reported by Wanlass, Moore and Sah<sup>[2,3]</sup> in 1963. For this comparison, we use the ideal 2-T CMOS voltage inverter which was described by the 1964-Sah drift-current-only model, given by Equations (672.15) to (672.22) in section 672 of FSSE<sup>[7]</sup>. Based on the discussion of the threshold voltage of a BiFET in [9], we will assume that the p-UniFET has a threshold voltage  $V_{\rm TP} = -kT/q \log_{\rm e}(C_{\rm O}/C_{\rm D})$  while the n-UniFET has  $V_{\rm TN} = kT/q \log_{\rm e}(C_{\rm O}/C_{\rm D})$ . In addition, the diffusion current in the subthreshold range of the two UniFETs, neglected in the

UniFET CMOS example given by Fig. 672.24 on page 631 of FSSE<sup>[7]</sup> are now taken into account using the subthreshold diffusion-current approximation given by section 682 and Fig. 682. 1 on page 655 of FSSE<sup>[7]</sup>.

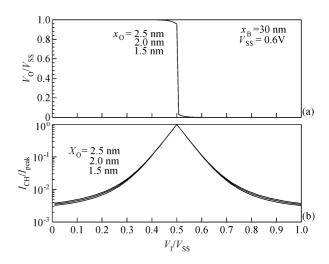

Figure 2 (a) shows that the one-BiFET CMOS voltage inverter (solid line) has a much sharper transition at transition voltage  $V_{\rm TR} = V_{\rm SS}/2$  than that of the two-UniFET CMOS voltage inverter (dash lines). Figure 2 (b) shows that (i) the channel current peak,  $I_{\rm TR}$ , of the 2-T UniFET CMOS voltage inverter have

Fig. 2 Comparison of the one-BiFET CMOS voltage inverter and the two-UniFET CMOS voltage inverter.

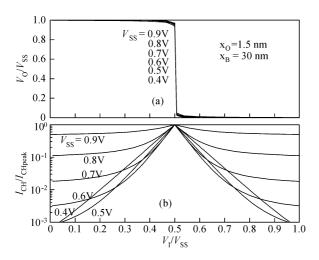

Fig. 3 Normalized transfer characteristics of a BiFET with two MOS gates and pure base under the CMOS voltage inverter circuit operation, with  $V_{\rm SS}$  varied.

slower rise with the power supply voltage,  $V_{ss}$ , than that of the 1-T BiFET CMOS voltage inverter; and (ii) the current in the 2-T UniFET CMOS voltage inverter has a sharper or exponential drop-off with the input voltage at the nearly ideal slope of 60mV per decay of a subthreshold surface inversion channel, while the current in the 1-T BiFET CMOS voltage inverter has a bell-shaped characteristic leveling off at the volume channel leakage current. These differences are accounted for analytically. For the 2-UniFET CMOS inverter Equation (672. 19) of FSSE<sup>[7]</sup> gave  $I_{\rm TR} \sim V_{\rm SS}^2$ , and at the transition voltage, one saturated surface inversion p-channel and one saturated surface inversion n-channel are in series. For the 1-BiFET CMOS inverter, Equation (11) of this paper gave  $I_{TR}$  $\sim$ exp( $V_{ss}/2$ ), and at the transition voltage, one volume p-channel and one volume n-channel are in series. Thus, the 2-UniFET CMOS inverter at both of

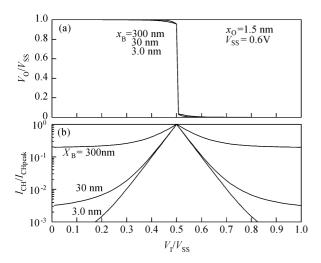

Fig. 4 Normalized transfer characteristics of a BiFET with two MOS gates and pure base under the CMOS voltage inverter circuit operation, with  $X_{\rm B}$  varied.

Fig. 5 Normalized transfer characteristics of a BiFET with two MOS gates and pure base under the CMOS voltage inverter circuit operation, with  $X_{\rm O}$  varied.

the two quiescent states,  $V_{\rm INPUT}=0$  or  $V_{\rm SS}$ , has a subthreshold surface inversion channel (electron or hole) which leads to exponentially very small channel current that is exponentially dependent on the input voltage; while the 1-BiFET CMOS inverter at the two quiescent states,  $V_{\rm INPUT}=0$  or  $V_{\rm SS}$ , has a volume channel which leads to large channel current, but only nearly linear dependence on the power supply voltage applied to a thin intrinsic or pure silicon resistance with its width slightly modulated by the width of the two surface channels.

# 4. 2 Dependences of the 1-BiFET CMOS Voltage Inverter Characteristics on $V_{SS}$ , $X_{B}$ and $X_{O}$

The power supply voltage dependence of the voltage transfer and current transfer characteristics are computed using the recursive algorithm to investigate the power-supply voltage dependences,  $V_{\rm SS}$ , and the dependences on the pure-base thickness,  $X_{\rm B}$ , and gate oxide thickness,  $X_0$ . These are presented respectively in Figs. 3,4, and 5, in normalized scales in order to show the salient features. Figures 3(a),4(a) and 5 (a) indicate that the sharp voltage transition shape is hardly affected by these three variables. Figure (b)'s show that the current decays exponentially with increasing  $V_{\rm I} = V_{\rm INPUT}$  but overtaken quickly by the volume channel leakage current, while the quiescent state current increases with channel thickness as  $X_{\mathrm{B}}^{2}$  (in the 3nm to 300nm range) but nearly independent of the oxide thickness  $X_0$  (in the 1.5nm to 2.4nm range). These are consistent with that expected from the device equations and device physics.

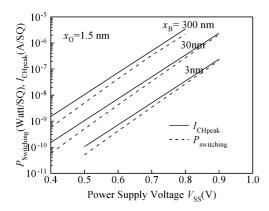

### 4.3 Current Peak and Switching Power Dissipation

Peak current and switching power dissipation are

Fig. 6 Channel current peak value,  $I_{\rm CHpeak}$ , and power dissipation,  $P_{\rm switching}$ , of a BiFET with two MOS gates and pure base under the CMOS voltage inverter circuit operation, as a function of  $V_{\rm SS}$  with  $X_{\rm B}$  varied. Note that  $I_{\rm CHpeak}$  and  $P_{\rm switching}$  are independent of  $X_{\rm O}$ .

Fig. 7 Percentage deviation of channel current and output voltage of the close-form solution from the non-recursive solution, with  $V_{\rm SS}$  varied.

the most important characteristics in circuit applications. Figure 6 shows the dependences of these characteristics on the power supply voltage,  $V_{\rm ss}$ , with base thickness in the range of 3nm to 300nm and oxide thickness of 1.5nm since they are relatively insensitive to the latter. The computed curves show the expected linear dependence on the base layer thickness  $X_{\rm B}$  from the leakage current through the width of the pure silicon base. They both show the exponential dependence on the power supply voltage  $V_{\rm ss}$  with a slope (or voltage swing per decade of currents) between the two ideal limits of  $k_{\rm B}T/q$  at 60mV and  $2k_{\rm B}T/q$  at 120mV per decade of current change.

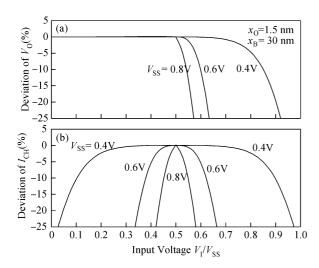

### 4.4 Deviations of the Compact Solution

The deviations of the compact solution of the output voltage,  $V_{\rm O}$ , and the channel current,  $I_{\rm CH}$ , from their corresponding non-recursive solutions are

shown in Figs. 7 (a) and 7 (b). The increasing  $V_{\rm O}$  deviations occur when  $V_{\rm I}$  is closer to  $V_{\rm SS}$  and when  $V_{\rm O}$  approaches zero. Similarly, the increasing percentage-deviation of  $I_{\rm CH}$  occurs when  $V_{\rm I}$  approaches the quiescent voltages, 0 and  $V_{\rm SS}$ , where the current is small. Thus, deviations of the compact solution should not be serious when design applications require the use of the much faster compact solution.

### 5 Summary

We have presented in this paper the current-voltage and voltage-voltage transfer characteristics and power-dissipation-vs-supply-voltage characteristics of the 1-BiFET CMOS voltage inverter circuit. We also investigated the deviation of the compact solution from the recursive-iteration solution and compared the CMOS voltage inverter circuit using 1-BiFET with that using 2-UniFET.

Acknowledgment We thank Professor Wang Yangyuan of Peking University, Academician of Chinese Academy of Sciences, for his supports which have enabled us to undertake this study.

### References

- [1] Chih-Tang Sah, "Evolution of the MOS Transistor from Conception to VLSI," Proceedings of the IEEE, 76(10), 1280-1326, October, 1988. For Shockley-Pearson field-effect experiment, see descriptions in the text citing reference [18]. See text describing Figs. 1-3 for Lilienfeld's 1926-1928 patents of field effect transistors based on the conductivity modulation principle which he explicitly stated in the patents. See text description for reference [30] on Shockley's invention of the unipolar field-effect transistor based on conductance modulation via the volume channel thickness by the two p/n junction gates.

- [2] Frank Wanlass and Chih-Tang Sah, "Nanowatt Logic Using Field-Effect Metal-Oxide Semiconductor Triodes", IEEE Solid-State Circuit Conference Proceedings, 32-33, February 20, 1963.

- [3] Gordon E. Moore, Chih-Tang Sah, Frank Wanlass, "Metal-Oxide-Semiconductor Field-Effect Devices for Micropower Logic Circuitry," 41-55, in Micropower Electronics, Edited by Edward Keonjian, New York: Pergamon Press, 1964.

- [4] Chih-Tang Sah and Bin B. Jie, "Double-Gate Thin-Base MOS Transistor: The Correct Theory," and Bin B. Jie and Chih-Tang Sah, "Double-Gate Thin-Base MOS Transistor: Characteristics for the Short Channel," Late-News Papers presented on May 23, 2007 at the Workshop on Compact Modeling (WCM2007) of the NSTI Nanotechnology Conference and Trade Show, May 22-24, 2007, hosted by the Nano Science and Technology Institute, Cambridge, MA02139, USA. http://www.nsti.org/Nanotech2007/WCM2007/.

- [5] Chih-Tang Sah and Bin B. Jie, "Bipolar Theory of MOS Field-Effect Transistors and Experiments," Chinese J. Semiconductors, 28(10),1497-1502,October,2007.

- [6] H.S. Fu and Chih-Tang Sah, "A distributed-gate bistable MOS transistor", Solid-State Electronics, 14(9), 799-804, September, 1971.

- [7] Chih-Tang Sah, Fundamentals of Solid-State Electronics, Singa-

- pore: World Scientific Publishing Company, 1991. For CMOS, see pages 624-631. For the two BBB circuits, see section 663 on pages 583 to 595 on the charge transfer gate, and section 672 on pages 614-631 on the MOS inverters.

- [8] Chih-Tang Sah and Bin B. Jie, "The Theory of Field-Effect Transistors: XI. The Bipolar Electrochemical Currents (1-2-MOS-

- Gates on Thin-Thick Pure-Impure Base)," Journal of Semiconductors, 29(3), 397-409, March 2008.

- [9] Chih-Tang Sah and Bin B. Jie, "The Bipolar Field-Effect Transistor Theory: I. Electrochemical Current Theory (Two-MOS-Gates on Pure-Base)," Chinese Journal of Semiconductors, 28 (11),1661-1673, November 2007.

## 双极场引晶体管: VI. CMOS 电压倒相电路(双 MOS 栅纯基)\*,\*\*

揭斌斌1, 薩支唐1,2,3,

(1 北京大学,北京 100871) (2 佛罗里达大学,佛罗里达州 Gainesville, FL 32605,美国) (3 中国科学院外籍院士,北京 100864)

摘要:本文报告了硅互补金属氧化层硅(CMOS)电压倒相电路的直流稳态电压和电流转移特性和功率耗散.这电路用一只实际的、纳米尺度的双极场引晶体管(BiFET)实现.通过数字求解五个偏微分方程,可获得这些电学特性.方程是基于这种器件结构:在薄纯硅基层的两表面上各有一个 MOS 栅,在这薄基的两端都有电子和空穴接触.内部条件和 CMOS 边界条件用于三种势(静电势和电子及空穴电化学势).用一台装有 Windows XP-PRO下的 64 位 FORTRAN 语言的双核个人计算机,快速地计算出一系列曲线.

关键词:双极场引晶体管理论;表面沟道;体积沟道;CMOS 倒相器;CMOS-BiFET

PACC: 7340Q EEACC: 2560S; 2560B

中图分类号: TN386.1 文献标识码: A 文章编号: 0253-4177(2008)11-2079-09

<sup>\*</sup>该研究及揭斌斌由 CTSAH Associates (CTSA) 资助. CTSA 由萨故夫人张淑南创建. 记念她第七十年.

<sup>\*\*</sup>萨支唐写成此摘要基于揭斌斌的现代语初稿.感谢潘胜和北京大学原物理系教师赵立群和潘桂明的修改建议.

<sup>†</sup>通信作者.Email:bb\_jie@msn.com and tom\_sah@msn.com