# CMOS current controlled fully balanced current conveyor\*

Wang Chunhua(王春华)<sup>†</sup>, Zhang Qiujing(张秋晶), and Liu Haiguang(刘海广)

(School of Computer and Communication, Hunan University, Changsha 410082, China)

**Abstract:** This paper presents a current controlled fully balanced second-generation current conveyor circuit (CF-BCCII). The proposed circuit has the traits of fully balanced architecture, and its X–Y terminals are current controllable. Based on the CFBCCII, two biquadratic universal filters are also proposed as its applications. The CFBCCII circuits and the two filters were fabricated with chartered 0.35- $\mu$ m CMOS technology; with ±1.65 V power supply voltage, the total power consumption of the CFBCCII circuit is 3.6 mW. Comparisons between measured and HSpice simulation results are also given.

**Key words:** current mode circuits; fully balanced; differential; second-generation current conveyor; filters **DOI:** 10.1088/1674-4926/30/7/075009 **EEACC:** 2570D

## 1. Introduction

As current-mode active devices, second generation current conveyors (CCIIs) are versatile building blocks for a variety of circuits<sup>[1-6]</sup>. Many modifications<sup>[7-11]</sup> have been introduced to increase the versatility of the CCII element. Differential difference current conveyors (DDCCs)<sup>[7]</sup>, differential voltage current conveyors (DVCCs)<sup>[8]</sup>, and fully differential second generation current conveyors (FDCCIIs)<sup>[9]</sup> are a few examples of these elements. In modern VLSI applications, balanced-mode structures are increasingly used. This is because non-ideal signals are generated in A/D mixed-mode circuits, and digital sections are the most serious source of noise due to clock feedthrough and charge injection. Moreover, in a balanced circuit, the output common-mode signal is kept constant, and it is entirely independent of the input signal. Therefore, performance of the circuit, such as dynamic range, noise restraining, and harmonic distortion can be greatly improved. A typical example of a balanced circuit, presented by Alzaher<sup>[10]</sup>, is a fully balanced second generation current conveyor (FBCCII), which has a great effect on restraining the common-mode signals.

In a conventional CCII and also in its modifications there is a relatively significant voltage tracking error from terminal Y to terminal X because of the parasitic resistor in terminal X, which leads to transfer function errors in the application circuits. Moreover, these elements lack electronic programmability which is a key feature in recent applications. In 2006, Minaei proposed a new electronically tunable CCII (ECCII)<sup>[12]</sup> which employed continuous tuning between X and Z terminals. However, voltage tracking errors still exist in the circuit. In 1996, Fabre<sup>[13]</sup> proposed a current controlled current conveyor (CCCII) constructed by a bipolar translinear loop; by introducing an intrinsic resistor, this circuit could rectify the transfer error between X and Y terminals, and at the same time, the intrinsic resistor in the X terminal could be adjusted by the bias current. However, it has a crucial disadvantage of having only one high input voltage terminal, and when differential or floating signals are to be handled, this disadvantage becomes evident.

In 2007, Wang presented a differential current controlled CCII with multiple outputs (MO-DCCCII)<sup>[14]</sup>. In this circuit, the voltage relationship between the differential input Y and the terminal X can be tuned by the extra bias current, and the transconductance linear loop is composed of four bipolar transistors. This circuit has advantages of low noise and high operating frequency, but the proposed structure is not compatible with CMOS VLSI technology. The CMOS differential current-controlled CCII proposed in Ref. [15] can be integrated conveniently as it is totally composed of CMOS transistors. However, there is a fabrication limitation in the CMOS translinear circuit and its practical applications are rather restricted. In addition, neither of the two circuits<sup>[14, 15]</sup> is fully balanced, as the X terminals of the circuits are single-ended.

In this paper, a CMOS current controlled fully balanced second-generation current conveyor (CFBCCII) circuit is proposed. This circuit has continuous current tuning possibilities of its port characteristics, in addition to the merits of FBCCII. Consequently, its application circuits are electronically adjustable.

## 2. CFBCCII circuit realization

#### 2.1. Circuit symbol and port characteristics

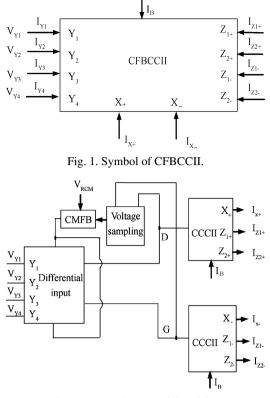

The circuit symbol of CFBCCII is shown in Fig. 1. It exhibits high input resistance at the Y terminals.  $Y_1$ ,  $Y_2$ ,  $Y_3$ , and  $Y_4$  are the two pairs of differential input terminals.  $X_+$  and  $X_-$  behave as voltage tracking terminals, and the current at the *Z* port is a replica of the current at the X port. Here, plus and minus signs denote the directions of currents in the Z port.  $I_B$  is the bias current of CFBCCII. The CFBCCII is represented

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (No. 60676021).

<sup>†</sup> Corresponding author. Email: wch1227164@sina.com

Received 8 January 2009, revised manuscript received 22 February 2009

Fig. 2. Frame diagram of CFBCCII.

mathematically by

$$\begin{cases} I_{Y1} = I_{Y2} = I_{Y3} = I_{Y4} = 0, \\ V_{X+} - V_{X-} = (V_{Y1} - V_{Y2}) + (V_{Y3} - V_{Y4}) + (I_{X+} - I_{X-})R_x, \\ I_{Z+} - I_{Z-} = I_{X+} - I_{X-}. \end{cases}$$

(1)

$R_{\rm X} = f(I_{\rm B})$  denotes the current controlled resistance which can be tuned by  $I_{\rm B}$ . A circuit frame diagram of the CFBCCII is given in Fig. 2. The circuit is made up of four stages: differential voltage input stage, current controlled current conveyor, voltage-sampling circuit, and common-mode feedback circuit (CMFB). The feedforward path consists of a differential input stage and two CCCIIs. Input voltage signals are added to the differential input stage, and their voltage differences are transferred to points D and G. Current controlled current conveyors are employed to transfer  $V_{\rm D}$  and  $V_{\rm G}$  to the output terminals. The feedback path consists of a voltage sampling circuit and a CMFB circuit. The voltages of points D and G will be sampled in the voltage sampling module, where the commonmode (CM) voltage is generated. The CMFB circuit is employed to restrain the CM signals; by comparing  $V_{\rm m}$  and  $V_{\rm RCM}$ ,  $V_{\rm m}$  is forced to follow  $V_{\rm m} = V_{\rm RCM}$ . In this way, the CM signal can be effectively suppressed.

## 2.2. CFBCCII circuit configuration

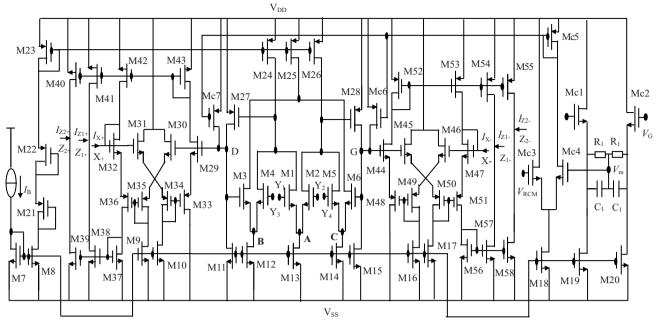

The proposed CMOS fully balanced current controlled current conveyor circuit is depicted in Fig. 3. Transistors M1– M6 constitute three pairs of differential inputs. The input voltages are applied to the circuit by the gates of the MOS transistors, so  $I_{Y1} = I_{Y2} = I_{Y3} = I_{Y4} = 0$ . Following the analysis in Ref. [18], the following equations can be obtained:  $I_{M1} = I_{M3} = I_{M5}$ ,  $I_{M2} = I_{M4} = I_{M6}$ . Assuming that all transistors operate in their saturation region, and channel-length modulation effects are not taken into consideration, the relationship between the drain current  $I_{\rm M}$  of the transistor and the gate-source voltage is given by  $I_{\rm M} = (K'W/2L)(V_{\rm GS} - V_{\rm T})^2$ , where K' is the transconductance parameter, W and L are the width and length of the drain channel respectively, and  $V_{\rm T}$  is the threshold voltage. When the channel dimensions of M1–M6 satisfy the following equations:  $W_1/L_1 = W_3/4L_3 = W_5/4L_5$ ,  $W_2/L_2 = W_4/4L_4 = W_6/4L_6$ , it can be obtained that:  $(V_{\rm GS1} + V_{\rm T})/2 = V_{\rm GS3} = V_{\rm GS5}$ ,  $(V_{\rm GS2} + V_{\rm T})/2 = V_{\rm GS4} = V_{\rm GS6}$ . According to the circuit shown in Fig. 3, one can obtain:  $(V_{\rm Y1} - V_{\rm A} + V_{\rm T})/2 = V_{\rm D} - V_{\rm B} = V_{\rm Y4} - V_{\rm C}$ ,  $(V_{\rm Y2} - V_{\rm A} + V_{\rm T})/2 = V_{\rm Y3} - V_{\rm B} = V_{\rm G} - V_{\rm C}$ . Then the expressions for  $V_{\rm D}$  and  $V_{\rm G}$  become  $V_{\rm D} = V_{\rm Y3} + (V_{\rm Y1} - V_{\rm Y2})/2$ ,  $V_{\rm G} = V_{\rm Y4} - (V_{\rm Y1} - V_{\rm Y2})/2$ .

Considering that the CCCII circuit proposed by Fabre<sup>[13]</sup> is not compatible for VLSI integration and the circuit in Ref. [16] has a fabrication limitation<sup>[17]</sup>, in this paper, the CCCII proposed by Wang is used to make up the circuit<sup>[17]</sup>. In Fig. 3, M29-M36 and M44-M51 respectively constitute two translinear loops, M29-M36 transfer the voltage from point D to  $X_{+}$  and M44–M51 transfer the voltage from point G to  $X_{-}$ . Now consider the translinear loop of M29-M36, following the analysis in Ref. [17], when the channel aspect ratios W/L of the NMOS transistors and PMOS transistors are identical, the voltage-current relationships are  $I_{\rm X} = (2\sqrt{2K_{\rm eff}I_{\rm B}})V_{\rm XY} =$  $R^{-1}V_{\rm XY}, R_{\rm X} = (2\sqrt{2K_{\rm eff}I_{\rm B}})^{-1}. R_{\rm X}$  denotes the equivalent resistance of port X which is inversely proportional to the square root of bias current  $I_{\rm B}$ . The voltages at points D and G are transferred to  $X_+$  and  $X_-$ , so the relationships can be written as:  $V_{X+} = V_{Y3} + (V_{Y1} - V_{Y2})/2 + I_{X+}R_X$ ,  $V_{X-} = V_{Y4} - (V_{Y1} - V_{Y2})/2 + I_{X+}R_X$  $V_{Y2}$ /2 +  $I_{X-}R_X$ . So the differential voltage at port X can be obtained as

$$V_{X+} - V_{X-} = (V_{Y1} - V_{Y2}) + (V_{Y3} - V_{Y4}) + (I_{X+} - I_{X-})R_X.$$

(2)

M37–M39, M40–M42, M53–M55, and M56–M58 form four current mirrors, then  $I_{Z1+} = I_{Z2+} = I_{X+}, I_{Z1-} = I_{Z2-} = I_{X-}$ , so  $I_{Z+} - I_{Z-} = I_{X+} - I_{X-}$ . From the aforementioned analysis, it is clear that the proposed CFBCCII satisfies the characteristics shown in Eq. (1).

In the fully balanced system, it is necessary to include a common mode feedback circuit to prevent drifting of the common mode output. In Fig. 3, the common mode feedback circuit consists of Mc1–Mc8 in addition to two resistors (R) and two capacitors (C). The operation of the CMFB circuit is explained in Ref. [10] in detail.

#### **3.** Applications

#### 3.1. Universal filter based on a single CFBCCII

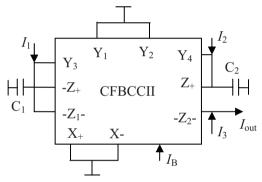

From the wealth of knowledge on RC active filters, it is known that it is possible to design filter biquads using a single active element, two resistors and two capacitors. Such filters are known as the minimum component count circuits. By virtue of the characteristics of the CFBCCII, the filter depicted in Fig. 4 does not need any resistors, so the proposed filter is only composed of a single CFBCCII and two capacitors. This

Fig. 3. The realization of the CFBCCII circuit.

Fig. 4. Universal filter based on a single CFBCCII.

circuit has the advantages of lower cost and power dissipation. As the figure shows, there are several extended terminals:  $-Z_+$ ,  $-Z_{1-}$ , and  $-Z_{2-}$ , the current relationship is:  $I_{-Z_+} = -I_{X_+}$ ,  $I_{-Z_{1-}} = I_{-Z_{2-}} = -I_{X_-}$ . Circuit analysis yields the following filter transfer functions:

$$I_{\text{out}} = \frac{I_3 s^2 R_X^2 C_1 C_2 + I_3 s R_X C_2 - I_2 s R_X C_1 + I_3 - I_1 - I_2}{s^2 R_X^2 C_1 C_2 + s R_X C_2 + 1}.$$

(3)

Numerous filtering functions can be obtained depending on the status of the input current. Table 1 shows the five statuses of the proposed filter. The  $\omega_0$  and Q values of the filter are given by  $\omega_0 = \frac{1}{R_X} \sqrt{\frac{1}{C_1C_2}}$ ,  $Q = \sqrt{\frac{C_1}{C_2}}$ . It is clear that  $\omega_0$  and Q are orthogonally adjustable.

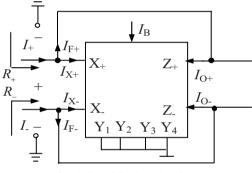

#### 3.2. Current-controlled second-order universal filter

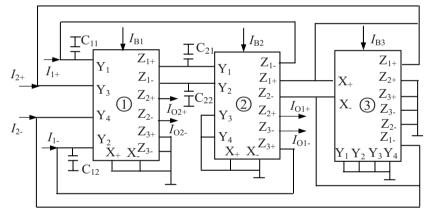

A CFBCCII based current controlled differential filter is proposed shown in Fig. 6. This circuit employs only three CFBCCIIs and two capacitors. The third CFBCCII is configured as two active resistors, whose configuration is shown in Fig. 5, and its resistance is equal to  $R_+ = R_- = \frac{1}{2}R_X = \frac{1}{2}(2\sqrt{2K_{\text{eff}}T_{\text{B}}})^{-1}$ . Circuit analysis yields the following filter transfer functions:

Fig. 5. CFBCCII based resistor.

$$I_{O1+} - I_{O1-} = \frac{2(I_{1+} - I_{1-}) + sC_1R_{X3}(I_{2+} - I_{2-})}{2s^2C_1C_2R_{X1}R_{X2} + sC_1R_{X3} + 2}, \quad (4)$$

$$I_{O2+} - I_{O2-} = \frac{2sC_2R_{X2}(I_{1+} - I_{1-}) + s^2C_1C_2R_{X3}R_{X2}(I_{2+} - I_{2-})}{2s^2C_1C_2R_{X1}R_{X2} + sC_1R_{X3} + 2}. \quad (5)$$

According to the two equations above, the transfer functions of the filter can be obtained. Table 2 shows the three statuses of the filter.

So the quality factor and the natural frequency  $\omega$  of the filter can be written as  $\omega = \sqrt{\frac{1}{R_{X1}R_{X2}C_1C_2}}, Q = \frac{2}{R_{X3}}\sqrt{\frac{R_{X1}R_{X2}C_2}{C_1}}.$

From the above expressions, it is clear that the natural frequency  $\omega$  and the quality factor can be orthogonally tuned by varying the bias current of the CFBCCII.

### 4. Simulation and measurement results

The CFBCCII circuit, the single CFBCCII based filter, and the fully differential second-order filter based on three CF-BCCIIs are fabricated in chartered 0.35- $\mu$ m CMOS technology. A photomicrograph of these three blocks occupying an area of  $2.41 \times 1.05$  mm<sup>2</sup> is shown in Fig. 7. The dimensions of the CFBCCII transistors are listed in Table 3. The supply voltages of the CFBCCII and the filter based on a single CF-BCCII are ±1.65 V, while the supply voltage of the filter based

| Table 1. Five statuses of the single CFBCCII based filter. |                                    |                        |                                                                                                                                  |  |

|------------------------------------------------------------|------------------------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| Туре                                                       | Input status                       | Value of the capacitor | Transfer function                                                                                                                |  |

| Low-pass                                                   | $I_1 = I_{\rm in}, I_2 = I_3 = 0$  |                        | $\frac{I_{\rm out}}{I_{\rm in}} = -\frac{1}{s^2 R_{\rm X}^2 C_1 C_2 + s R_{\rm X} C_2 + 1}$                                      |  |

| Band-pass                                                  | $I_1 = -I_2 = I_{\rm in}, I_3 = 0$ | $C_1 = C_2 = C$        | $\frac{I_{\text{out}}}{I_{\text{in}}} = \frac{sR_{\text{X}}C}{(sR_{\text{X}}C)^2 + sR_{\text{X}}C + 1}$                          |  |

| High-pass                                                  | $I_2 = I_3 = I_{\rm in},  I_1 = 0$ | $C_1 = C_2 = C$        | $\frac{I_{\rm out}}{I_{\rm in}} = \frac{(sR_{\rm X}C)^2}{(sR_{\rm X}C)^2 + sR_{\rm X}C + 1}$                                     |  |

| Band-reject                                                | $-I_1 = I_2 = I_3 = I_{\rm in}$    | $C_1 = C_2 = C$        | $\frac{I_{\text{out}}}{I_{\text{in}}} = \frac{(sR_{\text{X}}C)^2 + 1}{(sR_{\text{X}}C)^2 + sR_{\text{X}}C_2 + 1}$                |  |

| All-pass                                                   | $-I_1 = I_2 = 2I_3 = 2I_{\rm in}$  | $C_1 = C_2 = C$        | $\frac{I_{\text{out}}}{I_{\text{in}}} = \frac{(sR_{\text{X}}C)^2 - sR_{\text{X}}C + 1}{(sR_{\text{X}}C)^2 + sR_{\text{X}}C + 1}$ |  |

Table 1 Five statuses of the single CEPCCII based filter

| Table (  | 2          | Three | statuses | $\mathbf{of}$ | the | cinale | CFBCCII | hased | filter |

|----------|------------|-------|----------|---------------|-----|--------|---------|-------|--------|

| 1 auto 4 | <i>_</i> . | THILL | statuses | O1            | unc | Single | CIDCCII | Dascu | mu.    |

| Туре      | Input status                                                             | Output status               | Transfer function                                                                                         |

|-----------|--------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------|

| Low-pass  | $I_{1+} - I_{1-} = I_{\text{in}+} - I_{\text{in}-}, I_{2+} - I_{2-} = 0$ | $I_{\rm O1+} - I_{\rm O1-}$ | $\frac{2}{2s^2C_1C_2R_{X1}R_{X2} + sC_1R_{X3} + 2}$                                                       |

| Band-pass | $I_{2+} - I_{2-} = I_{\text{in}+} - I_{\text{in}-}, I_{1+} - I_{1-} = 0$ | $I_{\rm O1+} - I_{\rm O1-}$ | $\frac{sC_1R_{X3}}{2s^2C_1C_2R_{X1}R_{X2} + sC_1R_{X3} + 2}$                                              |

| High-pass | $I_{2+} - I_{2-} = I_{\text{in}+} - I_{\text{in}-}, I_{1+} - I_{1-} = 0$ | $I_{\rm O2+} - I_{\rm O2-}$ | $\frac{R_{X3}}{2R_{X1}} \frac{2s^2 C_1 C_2 R_{X1} R_{X2}}{2s^2 C_1 C_2 R_{X1} R_{X2} + s C_1 R_{X3} + 2}$ |

Fig. 6. CFBCCII based current controlled differential filter.

Table 3. Channel sizes of MOS transistors in the CFBCCII circuit.

| MOS transis- | $W/L (\mu m)$ | MOS transis- | $W/L$ ( $\mu$ m) |

|--------------|---------------|--------------|------------------|

| tors         |               | tors         |                  |

| M1, M2       | 2/0.35        | M3-M6        | 8/0.35           |

| M7-M17       | 16/0.35       | M21–M22,     | 10/0.35          |

|              |               | M19-M20      |                  |

| M23-M26      | 14/0.35       | M27, M28     | 20/0.35          |

| M29–M32,     | 10/0.35       | M33–M36,     | 40/0.35          |

| M44–M47      |               | M48-M51      |                  |

| M40-M43,     | 80/0.35       | M37–M39,     | 4/0.35           |

| M52–M55,     |               | M56-M58      |                  |

| M18          |               |              |                  |

| Mc1-Mc4      | 1/0.35        | Mc5–Mc7      | 2/0.35           |

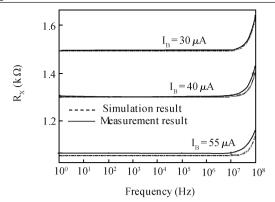

on three CFBCCIIs is  $\pm 1.8$  V, and all the capacitors in the two filters are set to be 40 pF. The total power consumption of the CFBCCII circuit is 3.6 mW. To verify the performance of the three circuits, measurements are made on the chip. The measured relationship between  $R_x$  and

Fig. 7. Die photo of CFBCCII and CFBCCII filters.

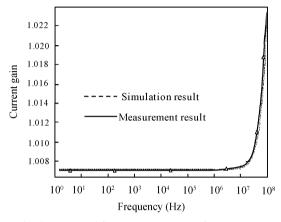

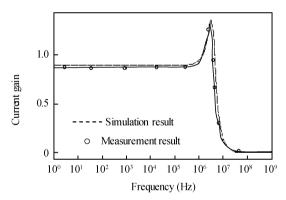

$I_{\rm B}$  of the CFBCCII compared with the HSpice simulation result is displayed in Fig. 8. Terminals  $X_+$ ,  $X_-$ , and terminals  $Z_{1+}$ ,  $Z_{2+}$ ,  $Z_{1-}$ , and  $Z_{2-}$  are all connected to grounded resistors of 1 k $\Omega$ . The curves represent  $R_{\rm X}$  with three different values of  $I_{\rm B}$ : 30, 40, and 55  $\mu$ A. According to Eq. (2), the theoretical values of  $R_{\rm X}$  would be 1.5, 1.3, and 1 k $\Omega$  respectively. Figure 9 illustrates the measured and simulated frequency response of the Z–X current. Both figures show that the measurement results are in accordance with the simulation results. It is seen that in the frequency range 0–40 MHz, the differential output current ( $I_{Z+}-I_{Z-}$ ) is consistent

Fig. 8. Measured relationship between  $R_x$  and  $I_B$ .

Fig. 9. Measured frequency response of Z-X current.

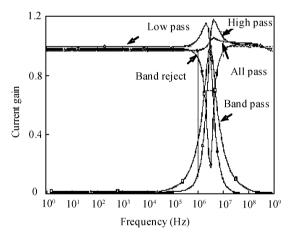

Fig. 10. Measured frequency response of the filter based on a single.

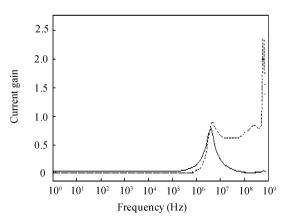

Fig. 11. Simulated frequency characteristics of BP and HP responses of the proposed filter.

$10^{4}$

Frequency (Hz)

105 106

107 108

Current gain

$10^{\circ}$   $10^{\circ}$

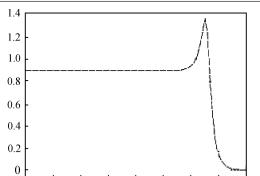

Fig. 12. Simulated frequency characteristic of the LP response of the proposed filter.

10<sup>2</sup> 10<sup>3</sup>

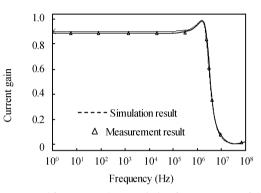

Fig. 13. Measured frequency characteristic of LP response of the filter based on a single CFBCCII.

Fig. 14. Measured frequency characteristic of LP response of the filter based on three CFBCCIIs.

with the differential input current  $(I_{i+}-I_{i-})$ . Figures 10, 11 and 12 are the simulated ac frequency responses of the filtering responses of the two CFBCCII based filters. The ac frequency responses of these filters are also measured. For simplicity, only the low-pass filtering responses of the two filters are given. Figure 13 shows the measured frequency characteristic of the LP response of the filter based on a single CFBCCII, while Figure 14 gives a comparison of the simulated and measurement results of the filter based on three CFBCCIIs.

#### 5. Conclusion

The design and implementation of a fully balanced current controlled current conveyor (CFBCCII) is presented. Its fully differential architecture and current controllability makes this element more attractive in analog applications using modern VLSI technology. The CFBCCII realization is implemented in a  $2.41 \times 1.05 \text{ mm}^2$  CMOS chip, and its characteristics are experimentally verified in the lab. Application examples in designing CFBCCII based filters are also presented.

## References

- Fabre A, Saaid O, Boucherron C. High frequency applications based on a new current controlled conveyor. IEEE Trans Circuits Syst I, 1996, 43(2): 82

- [2] Khan A A, Bimal S, Dey K K. Novel RC sinusoidal oscillator using second-generation current conveyor. IEEE Trans Instrumentation and Measurement, 2005, 54(6): 2402

- [3] Abuelma'atti M T, Celma S, Martinez P. Minimal realization for single resistor controlled sinusoidal oscillator using CCII. Electron Lett, 1992, 28(13): 1264

- [3] Chang C M, P C Chen. Universal active current filter with three inputs and one output using current conveyors. International Journal of Electronics, 1991, 71(4): 817.

- [4] Fabre A, Alami M. Universal current mode biquad implemented from two second generation current conveyors. IEEE Trans Circuits Syst I, 1995, 42(7): 383

- [5] Keskin A Ü, Cam U. Insensitive high-output impedance minimum configuration SITO-type current-mode biquad using dualoutput current conveyors and grounded passive components. AEU International Journal of Electronics and Communications, 2007, 61(4): 341

- [6] Chiu W, Liu S I, Tsao H W, et al. CMOS differential difference current conveyors and their applications. IEE Proceedings G: Circuits Devices Systems, 1996, 43(2): 91

- [7] Elwan H O, Soliman A M. Novel CMOS differential voltage current conveyor and its applications. IEE Proceedings G: Cir-

cuits Devices Systems, 1997, 144(2): 195

- [8] El-Adawy A A, Soliman A M, Elwan H O. A novel fully differential current conveyor and applications for analog VLSI. IEEE Trans Circuits Syst II, 2000, 47(3): 306

- [9] Alzaher H A, Elwan H, Ismail M. A CMOS fully balanced second-generation current conveyor. IEEE Trans Circuits Syst II, 2003, 50(6): 278

- [10] Mahmoud S A, Hashiesh M A, Soliman A M. Low-voltage digitally controlled fully differential current conveyor. IEEE Trans Circuits Syst I, 2005, 52(10): 2055

- [11] Minaei S, Sayin O K, Kuntman H. A new CMOS electronically tunable current conveyor and its application to current-mode filters. IEEE Trans Circuits Syst I, 2006, 53(7): 1448

- [12] Fabre A, Saaid O, Wiest F, et al. High frequency applications based on a new current controlled conveyor. IEEE Trans Circuits Syst I, 1996, 43(2): 82

- [13] Wang C H, Li J, Zhang Q J. A new differential currentcontrolled current conveyor and its differential ladder currentcontrolled current-mode filter. Proc International Workshop on Electro Devices and Semiconductor Technology, Beijing, 2007: 198

- [14] Wang C H, Li J. A CMOS differential current-controlled second generation current conveyor. Proc 6th International Conference on ASIC, Shanghai, 2005, 1: 447

- [15] Ling Xieting, Qin Wei, Hu Bo. CMOS current controlled conveyor and its applications. Chinese Journal of Electronics, 1999, 27(8): 34

- [16] Wang C H, She Z X, Liu H G. New CMOS current-controlled second generation current conveyors. Proc 4th IEEE International Conference on Circuits and Systems for Communications, 2008: 333

- [17] Wang C H, Liu H G, Zhang Q J, et al. A fully differential current-controlled second generation current conveyor. Journal of Hunan University (Natural Sciences), 2008, 35(3): 80