# A low power high gain UWB LNA in 0.18-µm CMOS\*

Cai Li(蔡力), Fu Zhongqian(傅忠谦)<sup>†</sup>, and Huang Lu(黄鲁)

(Department of Electronic Science and Technology, University of Science and Technology of China, Hefei 230027, China)

**Abstract:** A low power high gain differential UWB low noise amplifier (LNA) operating at 3–5 GHz is presented. A common gate input stage is used for wideband input matching; capacitor cross coupling (CCC) and current reuse techniques are combined to achieve high gain under low power consumption. The prototypes fabricated in 0.18- $\mu$ m CMOS achieve a peak power gain of 17.5 dB with a –3 dB bandwidth of 2.8–5 GHz, a measured minimum noise figure (NF) of 3.35 dB and –12.6 dBm input-referred compression point at 5 GHz, while drawing 4.4 mA from a 1.8 V supply. The peak power gain is 14 dB under a 4.5 mW power consumption (3 mA from a 1.5 V supply). The proposed differential LNA occupies an area of 1.01 mm<sup>2</sup> including test pads.

**Key words:** UWB; LNA; high gain; low power **DOI:** 10.1088/1674-4926/30/11/115004 **EEACC:** 1205; 1220

### 1. Introduction

UWB is a new wireless technology which is able to transmit data over short distances with high data rates and low power consumption. The Federal Communication Committee (FCC) has set aside the 3.1–10.6 GHz band for commercial use since 2002<sup>[1]</sup>. This whole band can be divided into two sub-bands, 3.1–5 GHz for the lower band and 6–10.6 GHz for the upper band. It is the lower band that is used in our UWB system.

Design of a broadband low noise amplifier (LNA) across 3.1–5 GHz is critical for the UWB receiver, as it should achieve high gain, low return loss and a low noise figure over the 2 GHz bandwidth, while keeping a strict limit on power consumption and die area. Many structures of UWB LNA have been fabricated in CMOS technology, such as an inductively degenerated common source amplifier with a multi-section LC band-pass filter for input wideband matching<sup>[1]</sup> and resistive feedback<sup>[2]</sup> structures. As a wideband input match can be easily obtained by setting the transconductance of the common gate topology<sup>[3]</sup> without extra passive components, it is also popular for realizing a wideband LNA.

This paper presents a novel differential common gate UWB LNA with CCC and current reuse techniques to reduce the noise figure and improve the power gain.

### 2. Circuit design and analysis

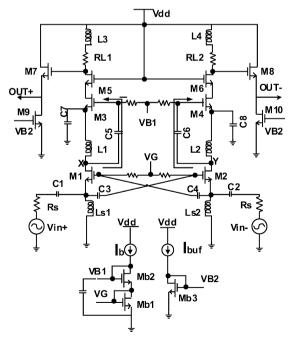

Figure 1 shows the proposed CMOS UWB LNA circuit utilizing the CCC<sup>[3]</sup> and current reuse techniques. It is proved in Ref. [3] that the CCC technique is able to reduce the noise figure and power consumption and improve the effective transconductance of the conventional common-gate LNA, while maintaining wideband input matching. But the gain and bandwidth of the CCC LNA in Ref. [3] cannot meet the gain and bandwidth specifications of the UWB LNA without extra bandwidth extension techniques. In the proposed LNA, L1,2 is used as the shunt peaking load of the input stage; it is also used to conduct DC current and block RF signal to implement the current reuse technique for the second cascode stage (M3,4 & M5,6) with shunt peaking<sup>[4]</sup>. Therefore a larger gain and wider bandwidth can be achieved without increasing the DC current of the LNA. M7,8 is a source follow buffer only for measurement purposes, and will not be presented when applied in the UWB receiver.

#### 2.1. Noise figure

The NF of a multi-stage structure is dominated by the first stage. In the proposed UWB LNA, the NF is dominated

Fig. 1. Proposed UWB LNA topology.

© 2009 Chinese Institute of Electronics

<sup>\*</sup> Project supported by the National High Technology Research and Development Program of China (No. 2007AA01Z2b2).

<sup>†</sup> Corresponding author. Email: zqfu@ustc.edu.cn Received 12 May 2009, revised manuscript received 13 July 2009

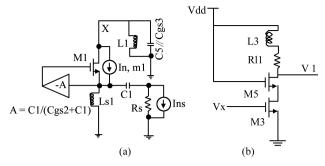

Fig. 2. (a) Equivalent circuit of the first stage; (b) Equivalent circuit of the second stage.

by the common gate input stage [Fig. 2(a)]. As gate induced noise is always negligibly small in a common gate LNA<sup>[3]</sup>, the NF of this circuit is dominated by channel current noise  $i_{n,m1}$ . The calculated NF is<sup>[5]</sup>:

$$F = 1 + \frac{i_{\rm nd}^2 \{1/[1 + (1 + A)g_{\rm m1}R_{\rm s}]\}^2}{\overline{i_{\rm ns}^2} \{(1 + A)g_{\rm m1}R_{\rm s}/[1 + (1 + A)g_{\rm m1}R_{\rm s}]\}^2}$$

$$= 1 + \frac{\overline{i_{\rm nd}^2}}{\overline{i_{\rm ns}^2}} [1/(1 + A)g_{\rm m1}R_{\rm s}]^2, \qquad (1)$$

where

$$\overline{i_{nd}^2} = 4kT\gamma g_{d0}\Delta f, \ \overline{i_{ns}^2} = 4kTR_s^{-1}\Delta f, \ \alpha = g_{m1}/g_{d0},$$

$$A = \frac{1/C_{gs}s}{1/C_{gs}s + 1/C_1s} = \frac{C_1}{C_1 + C_{gs}} \approx 1(C_1 \gg C_{gs}).$$

Equation (1) can be reduced to:

$$F = 1 + \frac{4kT\gamma g_{d0}\Delta f}{4kTR_{\rm s}^{-1}\Delta f} \left(\frac{1}{2g_{\rm m1}R_{\rm s}}\right)^2 = 1 + \frac{\gamma}{4\alpha g_{\rm m1}R_{\rm s}}.$$

(2)

Under perfect matching, the input impedance of the first stage is:

$$Z_{\rm in} \approx 1/(1+A)g_{\rm m1} \approx 1/2g_{\rm m1} = R_{\rm s}.$$

It can be further reduced to<sup>[5]</sup>:

$$F = 1 + \frac{\gamma}{2\alpha}.$$

(3)

This indicates that the CCC common gate LNA can achieve a better noise performance compared with a conventional common gate LNA ( $F = 1 + \frac{\gamma}{\alpha}^{[4]}$ ), while the current to achieve the same input matching is reduced. For  $\gamma/\alpha = 2$ , the calculated NF is about 3 dB.

#### 2.2. Wideband and high gain

In a one stage amplifier with shunt peaking is difficult to get 3 dB bandwidth over 2 GHz with high gain; therefore, two stages are cascaded to improve gain and bandwidth. In the proposed topology, the current of the common gate input stage is reused for the following cascode amplifier through the inductor L1,2. The large inductor L1,2 (8 nH in this design) shows high impedance for a high frequency signal, so the signal is blocked from the dc path from M1 to M3 and then is amplified by the subsequent cascode stage shown in Fig. 2(b). In

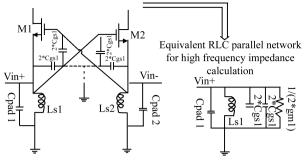

Fig. 3. Input network and its equivalent circuit.

addition, L1,2 is the load of M1,2 to extend the bandwidth of the first stage. It is designed to resonate at the lower frequency limit of 3.1–5 GHz. The second stage also employs the shunt peaking technique (L3,4) [Fig. 2(b)]; resistors  $Rl_{1,2}$  are used to lower the quality factor of L3,4 to further extend the bandwidth and maintain gain flatness. Proper design of L3,4 makes the gain of the second stage peak at a frequency near 6 GHz, leaving a little design margin over bandwidth.

# 2.3. Wideband input matching

The input network and its equivalent RLC network are shown in Fig. 3.

$$Z_{in}(s) = L_{s1}s / \frac{1}{2g_{m1}} / \frac{1}{(2c_{gs1} + 2c_{gs2} + c_{pad1})s}$$

$$= \frac{1}{1/(L_{s1}s) + (4c_{gs1} + c_{pad1})s + 2g_{m1}}.$$

(4)

The resonant frequency  $\omega_o$  is set at 4 GHz, which is the center of the 3–5 GHz band,  $Z_{in}(j\omega_o) = \frac{1}{2g_{m1}} = 50 \ \Omega$ . In addition, the quality factor of the RLC parallel network can be expressed as<sup>[3]</sup>:

$$Q_{\rm in} = \omega_{\rm o} \frac{1}{2g_{\rm m1}} (c_{\rm pad1} + 4c_{\rm gs1}) < 1.$$

<sup>(5)</sup>

The low quality factor of the input shunt resonant tank indicates that it is applicable for wideband input matching. The above equations are enough to determine input transistor size and inductance for a first order approximation; accurate calculation should take the inductor's parasitic resistor and capacitance into account.

### 2.4. Low power design

The proposed circuit exploits the capacitor cross coupling and current reuse techniques to save power consumption. Capacitor cross coupling boosts the effective transconductance of the input stage, and therefore it is able to use less current to obtain the same gain. The current reuse technique, which is implemented by inductor L1 and AC coupling capacitance C5, makes the power consumption even less for the required power gain and bandwidth.

#### 2.5. Inductor design and optimization

From the above analysis, the inductors are the key components to obtain high gain, ultra-wideband and power reduction, so they should be designed with special attention and

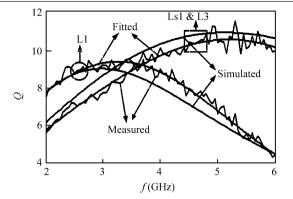

Fig. 4. Quality factor of the inductors.

modeled exactly. Moreover, performances such as gain or die area will be improved by optimizing the geometric parameters of the inductors<sup>[6]</sup>.

At 4 GHz, the skin depth  $\delta$  for our technology is 1.3  $\mu$ m, so a narrow track width is feasible at high frequencies. In the proposed circuit, a track width of 4  $\mu$ m is used to tune the peak quality factor of inductors at the frequency in the 3–5 GHz frequency range; the minimum spacing between tracks has been set to maximize the quality of the inductors; a narrow track width will also help to save die area and reduce substrate coupling through inductors. In the proposed circuit, L1 is designed to have a peak quality factor near 3 GHz, and L3 is designed to have a peak quality factor near 5 GHz. Ls1 has the same size as L3. All the inductors used in this circuit are fabricated with their corresponding test structures, and the simulated and measured results are presented in Section 3.

#### 2.6. ESD protection considerations for the LNA

In a CG LNA, the ESD problem is less sensitive since the RF input is connected to the source of the transistor where a parasitic diode exists (consisting of the n+ region of the M1 source and the p- region of the substrate) to carry the charges for a negative pulse to ground<sup>[7]</sup>. In addition, the inductor at the source which is used to tune out parasitic capacitance plays another important role for ESD protection as it provides a bidirectional path for ESD current to ground<sup>[7]</sup>. This kind of inductive ESD protection is especially effective in high frequency applications, as the inductor provides a low impedance path to ground for the ESD pulse ( $f_{ESD} < 1 \text{ GHz}$ )<sup>[8]</sup> but a high impedance for the RF signal ( $f_o = 3-5 \text{ GHz}$ ). It should be noted that it is implemented without additional components and therefore without degrading the circuit performance, compared with capacitive ESD protection.

### 3. Measurement results

All the inductors used in the proposed circuit are fabricated with open-short de-embedding structures. Figure 4 shows the simulated, measured and fitted quality factor of the inductors.

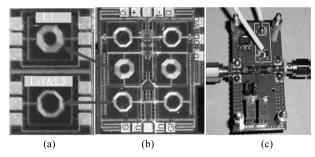

The proposed circuit has been fabricated in SMIC 0.18- $\mu$ m CMOS technology. Photographs of the circuit and inductors are shown in Fig. 5. The die area of the LNA is 840

Fig. 5. Photographs of (a) inductors, (b) chip, and (c) PCB.

Marker Frequency 3.000000000 GHz

Fig. 7. Measured S parameters.

$\times$  900  $\mu$ m<sup>2</sup> excluding test pads.

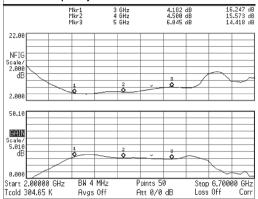

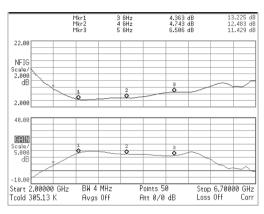

The proposed chip is mounted on an FR-4 PCB test board (COB) for measurements. The differential input and output signals are converted into a single-ended signal by a passive balun (BD3150N50100A00) with 0.6 B insertion loss. The measured current is 4.4 mA for the differential cores under a 1.8 V supply. An Agilent 8975A noise figure analyzer is used to measure the gain and NF of the differential LNA. Figure 6 shows the measured gain and NF of the LNA. The maximum measured power gain is 17.5 dB at 3.5 GHz. The power gain is 14.4–17.5 dB from 2.8 to 5.4 GHz. The measured NF is 3.95–6.0 dB from 3 to 5.4 GHz. It should be noted that the gain is measured without de-embedding 1.2 dB loss from baluns and 6 dB loss from the output buffer. The NF is 3.35 to 5.4 from 3 to 5.4 GHz as 0.6 dB loss from the input balun should be subtracted from the measured NF<sup>[9]</sup>.

| Reference | Gain (dB)          | Power (mW) <sup>c)</sup> | BW <sub>3dB</sub> (GHz) | $S_{11}$ (dB) | $NF (dB)^{d}$     | iCP (dBm)     | Area (mm <sup>2</sup> ) <sup>e)</sup> | Technology                       |

|-----------|--------------------|--------------------------|-------------------------|---------------|-------------------|---------------|---------------------------------------|----------------------------------|

| Ref. [1]  | 10.4 <sup>a)</sup> | 9                        | 2.3–9.2                 | < -9.4        | 4.2               | –18 @ 6 GHz   | 1.1                                   | $0.18\mu\mathrm{m}\mathrm{CMOS}$ |

| Ref. [2]  | 9.8 <sup>a)</sup>  | 12.6                     | 2–4.6                   | < -9          | 2.3 <sup>g)</sup> | NA            | 0.9                                   | $0.18\mu{ m m}{ m CMOS}$         |

| Ref. [10] | 9.7 <sup>a)</sup>  | 20                       | 1.2–11.9                | < -10         | 4.5               | –16 @ 6 GHz   | 0.59                                  | $0.18\mu{ m m}{ m CMOS}$         |

| Ref. [11] | 9.5 <sup>a)</sup>  | 16.5 <sup>f)</sup>       | 2–4.6                   | < -10         | 3.5               | 6 @ 3.1 GHz   | 1.08                                  | $0.13 \mu m  CMOS$               |

| Ref. [12] | 16                 | 38 <sup>f)</sup>         | 5.9                     | < -9          | 4.7               | -24           | 0.24                                  | $0.13 \mu m  CMOS$               |

| This work | 17.5 <sup>b)</sup> | 7.9 <sup>f)</sup>        | 2.8–5                   | < -8.5        | 3.35              | –12.6 @ 5 GHz | 1.01                                  | $0.18\mu{ m m}{ m CMOS}$         |

| This work | 14 <sup>b)</sup>   | 4.5 <sup>f)</sup>        | 2.8–5                   | < -10         | 3.6               | NA            | 1.01                                  | $0.18\mu{ m m}{ m CMOS}$         |

Table 1. Comparisons of the proposed wideband LNA with previously published work.

<sup>a)</sup> Maximum gain, approximately 6 dB loss due to output buffer; <sup>b)</sup> Maximum gain, approximately 6 dB loss from output buffer and 1.2 dB loss from baluns; <sup>c)</sup> Excluding output buffer; <sup>d)</sup> Minimum NF in the pass band; <sup>e)</sup> Including test pads; <sup>f)</sup> Differential designs; <sup>g)</sup> With external inductor.

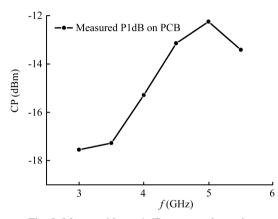

Fig. 8. Measured input 1 dB compression point.

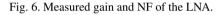

An Agilent 8722ES vector network analyzer was used to measure the *S* parameters; the results are shown in Fig. 7. The measured  $S_{11}$  stays below -8.5 dB and  $S_{22}$  remains below -10 dB over 2.8–5.4 GHz. Reverse isolation  $S_{12}$  < -40 dB from 2 to 6 GHz, which indicates good stability performance.

Figure 8 shows the measured input-referred 1 dB compression point, which shows –12.6 dBm at 5 GHz.

The above-mentioned test results show that the circuit is able to obtain high gain (17.5 dB) under low power consumption (7.9 mW) due to its novel architecture. To further explore its potential for low power operation, the supply is reduced to 1.5 V, the bias current  $I_b$  is adjusted to set core current consumption to 3 mA, and the gain and NF are measured and shown in Fig. 9. The measured gain under 4.5 mW remains larger than 10 dB across 2.7–5.6 GHz. The NF is 3.6–6.0 dB (0.6 dB balun loss is subtracted) from 3–5 GHz. Measured *S* parameters are shown in Fig. 10.

Table 1 summarizes the measurement results and compares them with previously published work.

# 4. Conclusion

A low power and high gain differential UWB LNA for a 3.1–5 GHz UWB receiver has been designed in this paper. By utilizing the capacitor cross coupling and currentreuse techniques along with proper design of on-chip inductors, high gain (17.5 dB) and low NF (3.35 dB) can be achieved under extremely low power consumption (7.9 mW). COB

Fig. 9. Measured gain and NF under 4.5 mW power consumption.

measurement results show that the proposed LNA can operate at 4.5 mW to provide 14 dB power gain. Moreover, the proposed LNA has the potential to be well protected from ESD pulses although this has not been tested. Due to the narrow track width of the inductors, the proposed differential circuit occupies an area of 1.01 mm<sup>2</sup> including test pads.

# Acknowledgement

The authors would like to thank Wen Jincai at HDU for measurements of the inductors and Li Wei at SEU for measurements of the LNA.

# References

- Bevilacqua A, Niknejad A M. An ultra-wide-band CMOS lownoise amplifier for 3.1 to 10.6-GHz wireless receiver. IEEE J Solid-State Circuits, 2004, 39(12): 2259

- [2] Kim C W, Kang M S, Anh P T, et al. An ultra-wide-band CMOS low-noise amplifier for 3–5-GHz UWB system. IEEE J Solid-State Circuits, 2005, 40(2): 544

- [3] Allstot D J, Li X, Shekhar S. Design considerations for CMOS low-noise amplifiers. Proc IEEE Radio Frequency Integrated Circuits Symp, 2004: 97

- [4] Lee T H. Design of CMOS radio-frequency integrated circuits. 1st ed. New York: Cambridge University Press, 1998

- [5] Li X, Shekhar S, Allstot D J. Gm-boosted common-gate LNA and differential Colpitts VCO/QVCO in 0.18-μm CMOS. IEEE J Solid-State Circuits, 2005, 40(12): 2609

- [6] Sia C B, Ong B H, Chan K W, et al. Physical layout design opti-

mization of integrated spiral inductors for silicon-based RFIC. IEEE Trans Electron Devices, 2005, 52(12): 2559

- [7] Leroux P. LNA-ESD co-design for fully integrated CMOS wireless receiver. Springer, 2005

- [8] Linten D, Thijs S, Natarajan M I, et al. A 5-GHz fully integrated ESD-protected low-noise amplifier in 90-nm RF CMOS. IEEE J Solid-State Circuits, 2005, 40(7): 1434

- [9] Razavi B. RF microelectronics. Prentice Hall PTR, 1998: 46

- [10] Liao C F, Liu S I. A broadband noise-canceling CMOS LNA

for 3.1–10.6-GHz UWB receiver. IEEE J Solid-State Circuits, 2004, 42(2): 329

- [11] Bevilacqua A, Sandner C, Gerosa A, et al. A fully integrated differential CMOS LNA for 3–5-GHz ultrawideband wireless receivers. IEEE Microw Wireless Compons Lett, 2006, 16(3): 134

- [12] Gharpurey R. A broadband low-noise front-end amplifier for ultra wideband in 0.13- $\mu$ m CMOS. IEEE J Solid-State Circuits, 2005, 40(9): 1983