# Design and application of a depletion-mode NJFET in a high-voltage BiCMOS process

Liu Yong(刘勇)<sup>1,2</sup>, Tang Zhaohuan(唐昭焕)<sup>1,†</sup>, Wang Zhikuan(王志宽)<sup>1</sup>, Yang Yonghui(杨永晖)<sup>1,2</sup>, Yang Weidong(杨卫东)<sup>1,2</sup>, and Hu Yonggui(胡永贵)<sup>1,2</sup>

(1 Sichuan Institute of Solid-State Circuits, CETC, Chongqing 400060, China) (2 National Laboratory of Analog ICs, Chongqing 400060, China)

**Abstract:** A novel depletion-mode NJFET compatible high-voltage BiCMOS process is proposed and experimentally demonstrated with a four-branch 12-bit DAC (digital-to-analog converter). With this process, an NJFET with a pinch-off voltage of about -1.5 V and a breakdown voltage of about 16 V, an NLDDMOS (N-type lightly-dosed-drain in MOS) with a turn-on voltage of about 1.0 V and a breakdown voltage of about 35 V, and a Zener diode with a reverse voltage of about 5.6 V were obtained. Measurement results showed that the converter had a reference temperature coefficient of less than  $\pm 25$  ppm/°C, a differential coefficient error of less than  $\pm 0.3$  LSB, and a linear error of less than  $\pm 0.5$  LSB. The depletion-mode NJFET and its compatible process can also be widely used for high-voltage ADCs or DACs.

Key words: depletion-mode NJFET; high-voltage BiCMOS process; ADC; DAC; temperature coefficient DOI: 10.1088/1674-4926/31/8/084006 PACC: 0130Q; 0750

### 1. Introduction

With the rapid development of information technology, requirements for ADC (analog-to-digital converter) and DAC (digital-to-analog converter) design in high-voltage BiCMOS processes are becoming more and more stringent<sup>[1, 2]</sup>. To meet the demand, it is necessary to develop a new process that enables ADCs and DACs to operate at  $\pm 15$  V supply voltage.

Generally speaking, a JFET has the advantages of high input-impedance, low 1/f noise (channel in bulk), low temperature drift, and so on<sup>[3-6]</sup>. In particular, there is a very low offset voltage; when a depletion-mode NJFET is used in the input stage of an amplifier for an ADC or DAC, it can commendably ensure conversion accuracy<sup>[1, 4]</sup>. Also, an NJFET can be directly used to design startup circuits of reference voltage for converters. Therefore, the depletion-mode NJFET is one of the key devices in the high-voltage BiCMOS process.

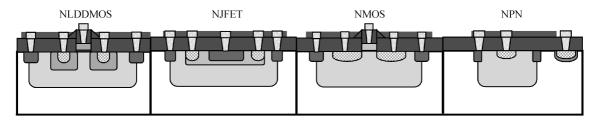

In this paper, a new depletion-mode NJFET compatible high-voltage BiCMOS process is proposed. The difficulty in designing the NJFET is that the breakdown voltage will decline, while the pinch-off voltage will rise, if the N-type impurity in the channel is high enough; otherwise, the device will be an enhanced-mode NJFET. So, a tradeoff should be made between breakdown voltage and pinch-off voltage. Figure 1 shows cross sections of the NJFET compatible CMOS and bipolar devices merged in this process.

# 2. Design and optimization

To make a depletion-mode NJFET for ADC and DAC working at  $\pm 15$  V, whose  $V_{\text{TH}}$  (pinch-off voltage) is  $-1.5 \pm 0.5$  V, the BV<sub>DSS</sub> (drain to source breakdown voltage) must exceed 15 V, and the typical value is 16 V. In particular, the process for the JFET has to be compatible with the high-voltage BiCMOS process.

#### 2.1. Device structure

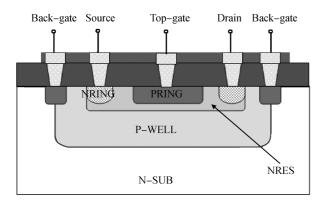

As shown in Fig. 1, there are several PN junctions in the high-voltage BiCMOS process, such as P-WELL to N-SUB (N-substrate), LDD to P-WELL or N-SUB, P<sup>+</sup> (PRING) to N-SUB and drain/source to P-WELL or N-SUB. The depth of P-WELL is about 7  $\mu$ m, and P<sup>+</sup> is about 1  $\mu$ m, so P<sup>+</sup> is chosen to form the top-gate of the NJFET, in which NRES (the resistor is fabricated by lightly doping implantation of PHOS (phosphorus)) is used for the channel of the NJFET, as shown in Fig. 2.

#### 2.2. Parameter optimization

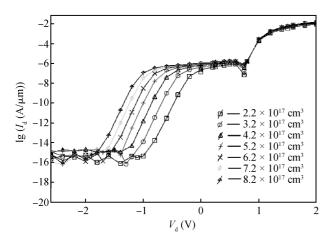

In fabrication of an NJFET using a high-voltage BiCMOS process, the difficulty is to find the tradeoff between the pinchoff voltage and breakdown voltage. Figure 3 shows simulated transfer characteristics of the NJFET with NRES doping varying from  $2.2 \times 10^{17}$  to  $8.2 \times 10^{17}$  cm<sup>-3</sup> in steps of  $1.0 \times 10^{17}$  cm<sup>-3</sup>.

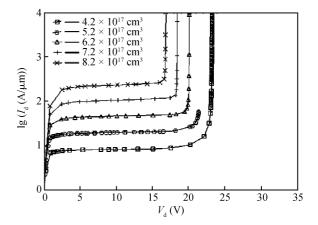

As shown in Fig. 3, when channel doping changed from  $4.2 \times 10^{17}$  to  $8.2 \times 10^{17}$  cm<sup>-3</sup>, the pinch-off voltage dropped to -1 and -2 V and the breakdown voltage changed from 23 to 15 V, as shown in Fig. 4.

From Fig. 4, it can be seen that, as doping varies from  $4.2 \times 10^{17}$  to  $8.2 \times 10^{17}$  cm<sup>-3</sup>, the breakdown voltage of the NJFET falls. It can also be seen that, as the channel doping varies between  $6.2 \times 10^{17}$  and  $8.2 \times 10^{17}$  cm<sup>-3</sup>, the breakdown voltage and pinch-off voltage change from 19 and -1 to 16 V and -2 V, respectively.

In order to optimize the breakdown voltage, the drain of the PMOS combined with RESURF is used to fabricate the topgate of the NJFET, and the channel doping is changed to  $3.2 \times 10^{17}$  cm<sup>-3</sup>. Simulation results show that the breakdown voltage of the NJFET reaches 35 V, as shown in Fig. 5.

<sup>†</sup> Corresponding author. sisc\_tang@163.com

Received 27 November 2009, revised manuscript received 2 April 2010

Fig. 1. Cross section of depletion-mode NJFET, CMOS and bipolar devices.

Fig. 2. Cross section of the proposed NJFET.

Fig. 3. Simulated transfer characteristics of the NJFET.

#### 2.3. Device realization

The depletion-mode NJFET compatible high-voltage Bi-CMOS process is as follows:

Initial oxide  $\rightarrow$  P-WELL photo/etch  $\rightarrow$  thin oxide  $\rightarrow$  boron implant  $\rightarrow$  P-WELL drive  $\rightarrow$  thin oxide  $\rightarrow$ PLDD photo  $\rightarrow$  PLDD boron implant  $\rightarrow$  NLDD photo  $\rightarrow$ NLDD PHOS implant  $\rightarrow$  NBASE photo  $\rightarrow$  PHOS implant  $\rightarrow$  [NRES photo  $\rightarrow$  PHOS implant  $\rightarrow$  annealing]  $\rightarrow$  PENH photo  $\rightarrow$  boron implant  $\rightarrow$  drive  $\rightarrow$  remove all oxide  $\rightarrow$  thin oxide  $\rightarrow$  [P + photo  $\rightarrow$  high boron implant]  $\rightarrow$  N+(NRING) photo  $\rightarrow$  high PHOS implant  $\rightarrow$  deposit SiO<sub>2</sub>  $\rightarrow$  annealing  $\rightarrow$ ACTIVE photo/etch  $\rightarrow$  light boron implant  $\rightarrow$  low boron implant  $\rightarrow$  gate oxide  $\rightarrow$  deposit POLY (Poly-Silicon)  $\rightarrow$  POLY doping  $\rightarrow$  POLY photo/etch  $\rightarrow$  PSD (drain and source of PMOS) photo  $\rightarrow$  high boron implant  $\rightarrow$  NSD (drain and source)

Fig. 4. Simulated breakdown voltage of the NJFET with doping changed from  $4.2 \times 10^{17}$  to  $8.2 \times 10^{17}$  cm<sup>-3</sup> in  $1.0 \times 10^{17}$  cm<sup>-3</sup> steps.

Fig. 5. Simulated breakdown voltage of the NJFET.

of NMOS) photo  $\rightarrow$  high PHOS implant  $\rightarrow$  deposit SiO<sub>2</sub>  $\rightarrow$  annealing  $\rightarrow$  LCONT photo/etch  $\rightarrow$  Metallization.

For the NJFET, no additional step is needed. NRES photo and PHOS implant are used to obtain both the phosphorous implanted resistor and the NJFET channel. In particular, P+ photo and heavy boron implant are used to form the top-gate and PN junction isolation.

## 3. Results and application

Using the process steps described above, high-performance NJFETs are implemented, and based on the device, a 12-bit digital-to-analog converter is fabricated. Test results show that

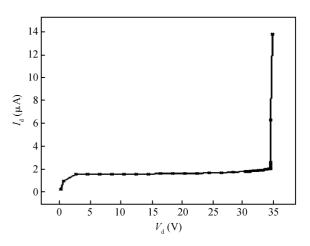

Fig. 6. Measured transfer characteristics of the NJFET.

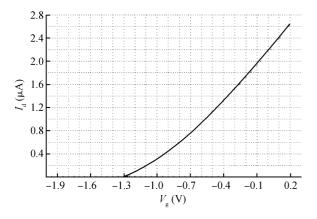

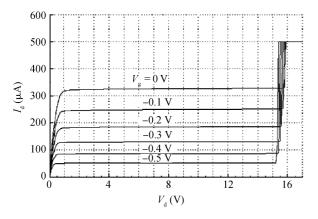

Fig. 7. Measured output characteristics of the NJFET.

Table 1. Performance of devices using the high-voltage BiCMOS process.

| Device      | Performance                      | Performance         |

|-------------|----------------------------------|---------------------|

| NLDDMOS     | BV <sub>DSS</sub> > 35 V         | 0.8–1.2 V           |

| PLDDMOS     | $BV_{DSS} < -35 V$               | -0.8 to -1.2 V      |

| NMOS        | $BV_{DSS} > 18 V$                | 0.8–1.2 V           |

| PMOS        | $BV_{DSS} < -18 V$               | –0.8 to –1.2 V      |

| VNPN        | $BV_{CEO} > 35 V$                | $\beta = 200 - 300$ |

| VPNP        | $BV_{CEO} < -35 V$               | $\beta = 20 - 40$   |

| NJFET       | $BV_{DSS} = 16 V$                | −1 to −2 V          |

| Zener diode | $V_{\rm F} = 5.4 - 5.6  {\rm V}$ | —                   |

the NJFET has a pinch-off voltage of about -1.5 V and a breakdown voltage of about 16 V, as shown in Figs. 6 and 7, respectively. Some other devices are also fabricated in the highvoltage BiCMOS process. Table 1 is a summary of the measured parameters of devices fabricated in the process.

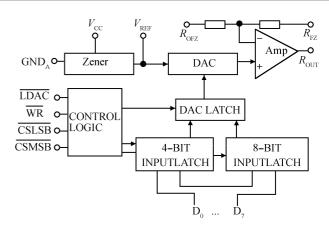

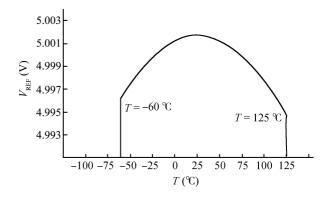

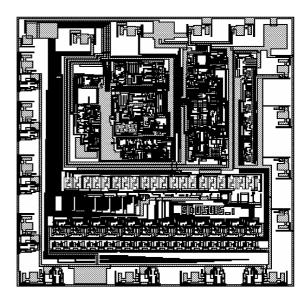

Figures 8–10 show a block diagram of the 12-bit DAC, its reference voltage curve (the temperature varies from –60 to 125 °C in 25 °C steps) and a microphotograph of the chip, respectively. Some parameters of the circuit are listed in Table 2.

Figure 9 shows that reference voltage of the DAC has an excellent temperature performance. The reason for this is that one of the two SiCr resistors in the reference will be trimmed with a laser to compensate for the variation if the temperature coefficient is positive, and the other resistor will be trimmed if the coefficient is negative. It can be seen from Table 2 that the

Fig. 8. Block diagram of the 12-bit DAC.

Fig. 9. Reference voltage curve of the DAC with temperature varying from -60 to 125 °C in 25 °C steps.

Fig. 10. Chip photo of the fabricated DAC.

DAC has a reference temperature coefficient of less than  $\pm 25$  ppm/°C, a differential coefficient error below  $\pm 0.3$  LSB, and a linear error of less than  $\pm 0.5$  LSB.

Table 2. Some parameters of the 12-bit D/A converter.

| Parameter                         | Symbol                | Value       |

|-----------------------------------|-----------------------|-------------|

| Resolution                        | R <sub>ES</sub>       | 12 bits     |

| Positive supply current           | $I_{\rm DD}$          | 8.5 mA      |

| Negative supply current           | $I_{\rm SS}$          | 3 mA        |

| Differential error                | $E_{\rm DL}$          | ±0.3 LSB    |

| Unipolar offset error             | $E_{\rm OU}$          | ±1 LSB      |

| Full range error                  | $E_{ m G}$            | ±3 LSB      |

| Linear error                      | $E_{\mathrm{L}}$      | ±0.5 LSB    |

| Reference output                  | $V_{\text{REF(OUT)}}$ | 4.99–5.01 V |

| Reference temperature coefficient | $\alpha V_{\rm REF}$  | ±25 ppm/°C  |

| Settling time                     | ts                    | $4 \mu s$   |

## 4. Conclusion

A novel high-voltage BiCMOS process compatible with a depletion-mode NJFET is developed. Based on the NJFET and its compatible process, a four-channel 12-bit DAC is implemented, which, operating at +15 V and  $\pm$ 15 V, has a reference temperature coefficient of less than  $\pm$ 25 ppm/°C, a differential coefficient error of less than  $\pm$ 0.3 LSB, and a linear error below  $\pm$ 0.5 LSB. The proposed device and compatible process are applicable for other high voltage ADCs/DACs.

## References

[1] Yang Weidong, Li Ruzhang, Liu Yong, et al. Investigation into

technology for a 12-bits D/A converter. Microelectronic, 2008, 38(1): 64 (in Chinese)

- [2] Gao Feng, Liu Yukui, Liu Yong. Development of a new BiCMOS technology for A/D, D/A converter with broad voltage range. Microelectronic, 2007, 37(1): 21 (in Chinese)

- [3] Sze S M. Physics of semiconductor devices. 2nd ed. New York: Willey, 1981: 222

- [4] Shui Guohua, Tang Zhaohuan, Wang Zhikuan, et al. Design of a high-performance PJFET for the input stage of the integrated operational amplifier. Journal of Semiconductors, 2010, 31(1): 014004

- [5] Arnaboldi C, Boella G, Panzeri E, et al. JFET transistors for lownoise applications at low frequency. IEEE Trans Nucl Sci, 2004, 51(6): 2975

- [6] Wang Ling, Zheng Shanxian. Noise of the JFET amplifier. Journal of Circuits and Systems, 2003, 8(3): 132

- [7] Godoy A, Jimenez-Tejada J A, Palma A, et al. Optimum design in a JFET for minimum generation-combination noise. Microelectronics Reliability, 2000, 40: 1965

- [8] Levinzon F A. Ultra-low-noise high-input impedance amplifier for low-frequency measurement applications. IEEE Trans Circuits Syst, 2008, 55(7): 1815

- [9] Fiorini C, Frizzi T, Longoni A, et al. A CMOS readout circuit for silicon drift detectors with on-chip JFET and feedback capacitor. IEEE Trans Nucl Sci, 2006, 53(4): 2196

- [10] Amon S, Vrtacinik D, Resnik D, et al. Self-aligned gate JFET modeling and characterisation. IEEE AFRICON, 5th Africaon Conference in AFrica, 1999: 1163