# A novel wideband low phase noise 2 : 1 frequency divider

Lei Xuemei(雷雪梅)<sup>1,2</sup>, Wang Zhigong(王志功)<sup>1,†</sup>, Wang Keping(王科平)<sup>1</sup>, and Li Wei(李伟)<sup>1</sup>

(1 Institute of RF- & OE-ICs, Southeast University, Nanjing 210096, China) (2 Inner Mongolia University, Hohhot 010021, China)

**Abstract:** This paper describes a novel low-power wideband low-phase noise divide-by-two frequency divider. Hereby, a new D-latch topology is introduced. By means of conventional dynamic source-coupled logic techniques, the divider demonstrates a wideband with low phase noise by adding a switch transistor between the clock port and the couple node of the input NMOS pair in the D latch. The chip was fabricated in the 90-nm CMOS process of IBM. The measurement results show that the frequency divider has an input frequency range from 0.05 to 10 GHz and the phase noise is -159.8 dBc/Hz at 1 MHz offset from the carrier. Working at 10 GHz, the frequency divider dissipates a total power of 9.12 mW from a 1.2 V supply while occupying only 0.008 mm<sup>2</sup> of the core die area.

Key words: frequency divider; wideband; low phase noise DOI: 10.1088/1674-4926/31/6/065005 EEACC: 2570

## 1. Introduction

Frequency dividers are required for many applications, such as frequency synthesis in high speed wireless communication systems, quadrature signal generators, and clock recovery circuits. The commonly used architectures of high speed frequency dividers are source-coupled logic (SCL) dividers, regenerative dividers, and injection locked dividers. Although the latter two architectures can achieve a high speed with low power consumption, they are inherently narrow band<sup>[1]</sup>, so this is not suitable for wideband systems. In comparison with them, SCL is a configuration with high speed, wideband, and appropriate power consumption. So the SCL architecture is widely applied in high speed wideband wireless communications. However, when the supply voltage drops below 1 V, the performance of SCL degrades significantly, and some of them even fail to function<sup>[2]</sup>. So Razavi's structure<sup>[3]</sup> is widely applied in the low supply voltage. The disadvantage of the structure is that the bandwidth is not wide enough to work at low frequency. On the other hand, a high spectrum purity divider with wideband is more and more important for many applications, such as software radio. So the traditional SCL structure should be improved to fit the demands of low supply voltage, high spectrum purity, and wideband.

In this paper, a 1.2 V, 0.05–10 GHz low phase noise divideby-two frequency divider is designed with a novel D-latch topology and designed in a 90-nm CMOSLP process. The circuit of the designed divider principle is briefly explained. A theoretical analysis of the bandwidth and phase noise is described.

## 2. Principle of the designed frequency divider

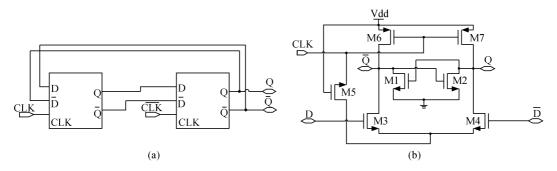

Figure 1(a) shows a block diagram of the divide-by-two frequency divider. It consists of two D latches which are crosscoupled with each other. It is based on master and slave latches connected in series. All the latch data signals are differential and the clock signals are pseudo differential. Each D latch is triggered by one clock signal, CLK or  $\overline{\text{CLK}}$ . These two D latches always operate periodically and alternately between the sampling mode and holding mode. So the cross connection between the output of the slave latch and the input of the master latch causes the clock frequency to be divided by two. Figure 1(b) shows the schematic of the designed D latch. The crosscoupled NMOS pair (M1, M2) is used as a positive feedback to hold the output signals in the holding mode. The input NMOS pair (M3, M4) is implemented to sample the input signals in the sampling mode. The pair of PMOS transistors (M6, M7) is implemented to the dynamic loading and an NMOS transistor (M5) is used as a switch in order to expand the bandwidth.

The operating principle of the design is based on the dynamic sampling and alternating operations of the D latches. In the sampling mode, the PMOS loading transistors are operated in a linear region and the switching transistor (M5) turns on. The turn-on resistance of the load is very small, thus achieving a small RC time constant at the output node. Then, the charge up or charge down current is very large. Such a small RC time constant and large current make the NMOS pair (M3, M4) sample the D input and charge-discharge the output nodes at the maximum speed. In the holding mode, the PMOS loading transistor and switching transistors (M5) are turned off and achieve a large RC output time constant in the output node. At the same time, the charge-discharge down current is very small. Such a large RC time constant and small current make the cross-coupled NMOS pair (M1, M2) hold the output state of the D latch at the maximum time. Thus, the dynamic load technique and switching transistor greatly increases the range of the frequency divider's operating frequency.

### 3. Bandwidth analysis

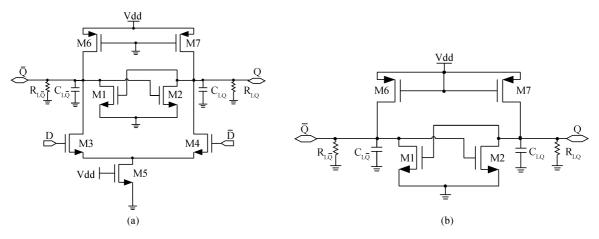

The operating frequency of the designed frequency divider is determined by the sampling and holding time. To predict the operating frequency, simplified schematics of the two modes are shown in Fig. 2, respectively.

<sup>†</sup> Corresponding author. Email:zgwang@seu.edu.cn

Received 28 November 2009, revised manuscript received 27 January 2010

Fig. 1. (a) Block schematic of the divide-by-two SCL frequency divider. (b) Schematic of the designed D latch.

Fig. 2. Simplified schematic of the D latch. (a) In sampling mode. (b) In holdling mode.

Figure 2(a) shows a simplified schematic of the D latch in sampling mode. The speed of sampling is limited by the RC time constant and the charge-discharge current. If CLK is at the low level, the D latch is in sampling state. It is supposed that at the beginning, D and  $\overline{Q}$  ports are at the high level, then  $\overline{D}$  and Q ports are at the low level. Thus, M3 is turned on, and M4 is turned off. The charge-down time constant ( $\tau_{s\overline{Q}}$ ) is given by

$$\tau_{s\overline{Q}} \approx (C_{\text{GDM6}} + C_{\text{GSM2}} + C_{\text{GDM2}} + C_{\text{L}\overline{Q}}) \\ \times \left[ r_{\text{on6}} || \left( r_{\text{on3}} + r_{\text{on5}} \right) || R_{\text{L}\overline{Q}} \right], \tag{1}$$

and the charge-up time constant  $(\tau_{sQ})$  is given by

$$\tau_{\rm sQ} \approx \left( C_{\rm GDM7} + C_{\rm GSM1} + C_{\rm LQ} \right) \left( r_{\rm on7} ||r_{\rm on2}||R_{\rm LQ} \right), \quad (2)$$

where  $r_{on2}$  is the on-resistance of M2,  $r_{on3}$  is the on-resistance of M3,  $r_{on5}$  is the on-resistance of M5,  $r_{on6}$  is the on-resistance of M6 and  $r_{on7}$  is the on-resistance of M7;  $L_{L\overline{Q}}$  and  $R_{LQ}$  include parasitic and load resistance;  $C_{L\overline{Q}}$  and  $C_{LQ}$  include load and parasitic capacitance.

According to the characteristics of the RC charge-up or charge-down circuit, the rise and fall times are determined by the time constant and charge-up or charge-down current. In the sampling mode, the current charge-up is supplied by M6 or M7, which are approximately equal; at the same time, the current of the charge-down is equal to  $i_{M5} - i_{M6}$  or  $i_{M5} - i_{M7}$ . The two time constants and the current are different, so the rise and the fall time are not equal. Finally, the sampling time is determined by the maximum of the rise time and fall time.

Figure 2(b) shows the schematic and equivalent circuit of the D latch in holding mode. The holding time is limited by the RC time constant and the leakage current. When CLK is at the high level, the D latch is in holding mode. It is supposed that at first time D and  $\overline{Q}$  ports are at the high level,  $\overline{D}$  and Q ports are at the low level. At the holding mode, the time constant ( $\tau_{h\overline{Q}}$ ) is given by

$$\tau_{\rm h\overline{O}} \approx (C_{\rm GDM6} + C_{\rm GDM1} + C_{\rm GSM2} + C_{\rm GDM2} + C_{\rm L\overline{O}})R_{\rm L\overline{O}}, (3)$$

and the time constant  $(\tau_{hQ})$  is given by

$$\tau_{\rm hQ} \approx (C_{\rm GDM7} + C_{\rm GDM1} + C_{\rm GSM1} + C_{\rm GDM2} + C_{\rm LQ})R_{\rm LQ}.$$

(4)

At the holding mode, the current only contains the small leakage current, it does not vary with the level of D and the time constant of the two ports is same, so the holding current is determined by the technology.

Compared to the divider which was designed by Razavi in Ref. [3], the holding time of the novel frequency divider is larger while sharing the same sampling time at the same condition. So the designed divider has a wider bandwidth.

### 4. Phase noise analysis

In Fig. 1(a), the jitter at the output of this divider is not affected by the noise of the first latch, since the output signals is not controlled by the latch. Thus, only the noise sources of the second latch need to be considered in the output jitter assessment. The time jitter can be computed from the variance of

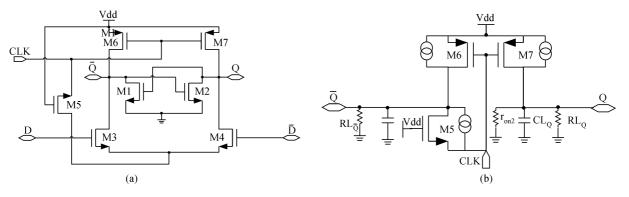

Fig. 3. (a) Schematic of the designed D latch. (b) Simplified schematic of the same circuit with a noise source.

output voltage  $\hat{V}_0^2$  as in Ref. [4]:

$$\sigma_{t_0}^2 = \frac{\hat{V}_o^2}{S_L^2},$$

(5)

where  $S_L$  is the slope of the output voltage at the zero crossings. The period jitter ( $\sigma_{Tout}^2$ ) is computed as

$$\sigma_{T_{\text{out}}}^2 = \sigma_{t_{\text{H0}}}^2 + \sigma_{t_{\text{L0}}}^2.$$

(6)

According to the expression  $\phi = 2\pi f_{out}t_0$ , the phase of the output signal is sampled at  $f_{out} = 1/T_{out}$  and it is proportional to the switching instant. The sampling process folds back any noise component at frequency higher than  $f_{out}/2$  and the phase spectrum is defined in the Nyquist band  $0-f_{out}/2$ . Then, the time jitter can be written in terms of the integral of the single-sided power spectral density (PSD) of the phase within the Nyquist band<sup>[5]</sup>:

$$\sigma_{t_0}^2 = \frac{1}{4\pi^2 f_{out}^2} \int_0^{f_{out}/2} S_{\phi}(f) df.$$

(7)

For proper operation of the divider, the D signals of the second latch have already switched completely before the CLK signal starts to switch. Therefore, M3 is off and M4 is in the triode region. The same happens to the transistors M1 and M2. Thus, the circuit in Fig. 3(a) can be further simplified as shown in Fig. 3(b).

From the schematic in Fig. 3(b), we can simply estimate the time delay between the input clock switching and the zerocrossing instant of the output signals Q and  $\overline{Q}$ . Both of the transient signals Q and  $\overline{Q}$  have an approximately exponential waveform with the different time constant  $(R_{LQ}||r_{on7}||r_{on2}) C_{LQ}$  and  $(R_{L\overline{Q}}||r_{on5}||r_{on6}) C_{L\overline{Q}}$ . The noise sources affecting the output zero crossing are also represented in Fig. 3(b). Therefore, the noise sources are a pair of PMOS transistors (M6, M7) and NMOS switching transistor (M5).

### 4.1. White phase noise

For white noise,  $S_{\phi}(f) = W$  is constant and Equation (6) gives the link between the jitter and the phase spectrum. The single-side-band-to-carrier ratio (SSCR or L) is

$$l_{\rm w} = \frac{W}{2} = 4\pi^2 f_{\rm out} \sigma_{t_0, \, \rm total}^2.$$

(8)

The linear dependence of  $l_w$  on the output frequency is in accordance with the model designed by Kroupa<sup>[4, 6]</sup>.

#### 4.1.1. Dynamic load transistors

In practice, the level of the CLK signal is low and the transistors of M6 and M7 work in the linear region when the CLK signal starts to switch. So the output noise currents of M6 and M7 are

$$\hat{i}_{o6}^{2} = 4kT \left[ \alpha \gamma \left( g_{m6} | V_{ds6} = 0 \right) \right] \cdot BW = kT \left[ \alpha \gamma \mu_{n} C_{ox} \frac{W_{6}}{L_{6}} \left( V_{GS6} - V_{TH} \right) \right] \frac{1}{\left( R_{L\overline{Q}} || r_{on6} || r_{on5} \right) C_{L\overline{Q}}},$$

(9)

$$\hat{i}_{o7}^{2} = 4kT \left[ \alpha \gamma \left( g_{m7} |_{V_{dS7}} = 0 \right) \right] \cdot BW = kT \left[ \alpha \gamma \mu_{n} C_{ox} \frac{W_{7}}{L_{7}} \left( V_{GS7} - V_{TH} \right) \right] \frac{1}{\left( L_{LQ} ||r_{on7}||r_{on2} \right) C_{LQ}},$$

(10)

where  $\gamma$  and  $\alpha$  are the noise factor and the constant relating to technology, respectively. Their current noise is alternatively injected into nodes Q and  $\overline{Q}$ . From the schematic in Fig. 3(b), the variance voltage of Q port and  $\overline{Q}$  port are

$$\hat{V}_{Q}^{2}(t) = \left(R_{LQ}||r_{on7}||r_{on2}\right)^{2} \hat{i}_{07}^{2} e^{-\frac{2t}{(R_{LQ}||r_{on7}||r_{on2})C_{LQ}}}, \quad (11)$$

$$\hat{V}_{\overline{Q}}^{2}(t) = \left(R_{\mathrm{L}\overline{Q}}||r_{\mathrm{on5}}||r_{\mathrm{on6}}\right)^{2} \hat{i}_{\mathrm{o6}}^{2} \mathrm{e}^{-\frac{2t}{\left(R_{\mathrm{L}\overline{Q}}||r_{\mathrm{on5}}||r_{\mathrm{on6}}\right)C_{\mathrm{L}\overline{Q}}}}.$$

(12)

Without considering the noise effect, we assume that Q is at low level and  $\overline{Q}$  is at high level. The transient voltages of Q and  $\overline{Q}$  are

$$V_{\rm Q}(t) = \frac{V_{\rm DD}}{r_{\rm on7}} \left( R_{\rm LQ} || r_{\rm on7} || r_{\rm on2} \right) \left( 1 - e^{-\frac{t}{\left( R_{\rm LQ} || r_{\rm on7} || r_{\rm on2} \right) C_{\rm LQ}}} \right) + V_{\rm Q} \left( 0_{-} \right), \tag{13}$$

$$V_{\overline{Q}}(t) = \left(\frac{v_{\mathrm{DD}}}{r_{\mathrm{on6}}} - \frac{v_{\mathrm{DD}}}{r_{\mathrm{on5}}}\right) \left(R_{\mathrm{L}\overline{Q}}||r_{\mathrm{on5}}||r_{\mathrm{on6}}\right)$$

$$\times \mathrm{e}^{-\frac{t}{\left(R_{\mathrm{L}\overline{Q}}||r_{\mathrm{on5}}||r_{\mathrm{on6}}\right)C_{\mathrm{L}\overline{Q}}}} + V_{\overline{\Omega}}\left(0_{-}\right). \tag{14}$$

Thus, at the zero crossings, the slopes of Q port voltage and  $\overline{Q}$  port voltage are equal to

$$S_{\rm LQ} = \frac{V_{\rm DD}}{C_{\rm LQ}r_{\rm on7}},\tag{15}$$

J. Semicond. 2010, 31(6)

$$S_{\mathrm{L}\overline{\mathrm{Q}}} = \left(\frac{V_{\mathrm{DD}}}{r_{\mathrm{on5}}} - \frac{V_{\mathrm{DD}}}{r_{\mathrm{on6}}}\right) \frac{1}{C_{\mathrm{L}\overline{\mathrm{O}}}}.$$

(16)

Taking Eq. (5) into account, at the moment of t = 0, the jitter due to the dynamic load transistor noise can be written as:

$$\sigma_{t_{0},Q}^{2} = \frac{\left(R_{LQ}||r_{\text{on7}}||r_{\text{on2}}\right)^{2}\hat{i}_{07}^{2}}{\left(S_{LQ}\right)^{2}} = \left(\frac{C_{LQ}r_{\text{on7}}}{V_{\text{DD}}}\right)^{2} \left(R_{LQ}||r_{\text{on7}}||r_{\text{on2}}\right)^{2}\hat{i}_{07}^{2}, \quad (17)$$

$$\sigma_{t_0,\overline{Q}}^2 = \frac{\left(R_{\rm L}\overline{Q}||r_{\rm on6}||r_{\rm on5}\right)^2 \hat{i}_{06}^2}{\left(S_{\rm L}\overline{Q}\right)^2} \\ = \left(\frac{C_{\rm L}\overline{Q}r_{\rm on6}r_{\rm on5}}{V_{\rm DD}(r_{\rm on6}-r_{\rm on5})}\right)^2 \left(R_{\rm L}\overline{Q}||r_{\rm on6}||r_{\rm on5}\right)^2 \hat{i}_{06}^2.$$

(18)

The two random processes described by Eqs. (8) and (9) are uncorrelated, so Equations (16) and (17) are uncorrelated. We can get

$$\sigma_{t_0, \text{ total}}^2 = \sigma_{t_0, Q}^2 + \sigma_{t_0, \overline{Q}}^2.$$

(19)

#### 4.1.2. Switching transistors

M5 works in the linear region when the CLK signal starts to switch. Thus, the output noise current of M5 is

$$\hat{i}_{o5}^{2} = 4kT \left[ \alpha \gamma \left( g_{m5} |_{V_{ds5}} = 0 \right) \right] \cdot BW$$

$$= kT \left[ \alpha \gamma \mu_{n} C_{ox} \frac{W_{5}}{L_{5}} \left( V_{GS5} - V_{TH} \right) \right] \frac{1}{\left( R_{L\overline{Q}} ||r_{on6}||r_{on5} \right) C_{L\overline{Q}}}.$$

(20)

The current noise is injected into node  $\overline{Q}$ . So the variance voltage across  $\overline{Q}$  port is

$$\hat{V}_{\overline{Q}}^{2}(t) = \left(R_{\mathrm{L}\overline{Q}}||r_{\mathrm{on5}}||r_{\mathrm{on6}}\right)^{2}\hat{i}_{\mathrm{o5}}^{2}\left(1 - \mathrm{e}^{-\frac{2t}{\left(R_{\mathrm{L}\overline{Q}}||r_{\mathrm{on5}}||r_{\mathrm{on6}}\right)C_{\mathrm{L}\overline{Q}}}\right).$$

(21)

At the moment of t = 0,  $\hat{V}_{\overline{Q}}^2(0) = 0$ . So the switching transistor noise has no effect on the port  $\overline{Q}$ .

### 4.1.3. Total white phase noise

The total jitter is obtained from the three noise contributions of Eqs. (17) and (18). The correspondent phase noise level follows from Eqs. (8) and (19), and it is

$$l_{\text{total, }W} = 2\pi \alpha \gamma \mu_{\text{n}} C_{\text{ox}} \frac{W_{6}}{L_{6}} \left( V_{\text{GS6}} - V_{\text{TH}} \right) \frac{r_{\text{on7}}^{2} C_{\text{LQ}}}{V_{\text{DD}}^{2}} \times \left[ R_{\text{LQ}} ||r_{\text{on7}}||r_{\text{on2}} + \left( R_{\text{LQ}} ||r_{\text{on6}}||r_{\text{on5}} \right) \left( \frac{r_{\text{on5}}}{r_{\text{on6}} - r_{\text{on5}}} \right)^{2} \right] f_{\text{out}}.$$

(22)

Notes:  $V_{\text{GS6}} = V_{\text{GS7}}, r_{\text{on6}} \approx r_{\text{on7}}, C_{\text{LQ}} \approx C_{\text{L}\overline{\text{Q}}} \text{ and } R_{\text{LQ}} \approx R_{\text{L}\overline{\text{Q}}}$

## 4.2. Flicker phase noise

Because of the sampling effect, the flicker noise is convenient to analyze in the frequency domain. The output voltage noise at frequency  $(kf_{out} \pm f_m)$  (with k = 0, 1, ... and

Lei Xuemei *et al.*

$f_{\rm m} < f_{\rm out}/2$ ) can be represented as a signal with amplitude  $V_{\rm m}$  and random phase. Because of sampling, this voltage signal causes a phase variance  $\phi_{\rm m}$  at  $f_{\rm m}$ , it can be calculated as

$$\phi_{\rm m} = 2\pi f_{\rm out} \frac{V_{\rm m}}{S_{\rm L}}.$$

(23)

Hence, the phase noise spectrum can be written as

$$\ell_{\rm w} = \frac{2\pi^2 f_{\rm out}^2}{S_L^2} S_{\rm V}^{\rm folded}(f_{\rm m}), \tag{24}$$

where  $S_V^{\text{folded}}(f_m)$  is the PSD of the output voltage noise folded in the Nyquist band from 0 to  $f_{\text{out}}/2$ .

If the corner frequency of the voltage spectrum is lower than  $f_{out}/2$ , the flicker component undergoes no folding and  $S_V^{folded}(f_m)$  in Eq. (24) can be substituted by the unfolded spectrum  $S_V(f_m)$ . As a result, the phase noise in the flicker region is proportional to the square of the output frequency  $f_{out}$ . This dependence has been experimentally verified in Ref. [6].

Once the PSD of the output voltage  $S_V(f_m)$  has been expressed in the terms of the noise source, Equation (24) can be used to estimate the phase noise of a frequency divider in the flicker region.

### 4.2.1. Dynamic load transistors

In practice, the level of the CLK signal is low and the transistors begin to work on the triode region when the CLK signal starts to switch. So the output noise currents of M6 and M7 respectively are

$$\hat{i}_{o6,f}^{2} = \frac{K_{f} (g_{m6}|_{V_{ds6}} = 0)^{2}}{W_{6}L_{6}C_{ox}} \frac{BW}{f}$$

$$= \frac{K_{f}W_{6}C_{ox} [kT\alpha\gamma\mu_{n} (V_{GS6} - V_{TH})]^{2}}{L_{6}^{3}}$$

$$\times \frac{1}{f} \frac{1}{4 (R_{L\overline{O}}||r_{on5}) C_{L\overline{O}}},$$

(25)

$$\hat{i}_{o7,f}^{2} = \frac{K_{f} (g_{m7} | v_{ds7} = 0)^{2}}{W_{7} L_{7} C_{ox}} \frac{BW}{f}$$

$$= \frac{K_{f} W_{7} C_{ox} [k T \alpha \gamma \mu_{n} (V_{GS7} - V_{TH})]^{2}}{L_{7}^{3}}$$

$$\times \frac{1}{f} \frac{1}{4 (R_{LQ} || r_{on7} || r_{on2}) C_{LQ}},$$

(26)

where  $K_{\rm f}$  is a constant relating to the technology.

In the frequency domain, the transfer function between the flicker noise current spectrum and the output noise voltage spectrum is

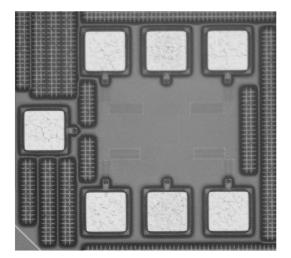

Fig. 4. Chip photograph of the designed frequency divider.

$$\begin{aligned} \left| Z_{\rm Q}(f) \right|^2 &= \frac{1}{4\pi^2 f^2 C_{\rm LQ}^2 + \left( \frac{1}{R_{\rm LQ}} + \frac{1}{r_{\rm on7}} + \frac{1}{r_{\rm on2}} \right)^2} \\ &\times \left[ \sum_{n=0}^{\infty} Sa(\frac{n\pi}{2}) \delta(2\pi f - 2n\pi f_{\rm out}) \right] \\ &= \frac{1}{2} \sum_{n=-\infty}^{\infty} \left\{ Sa\left(\frac{n\pi}{2}\right) \times \left[ 4\pi^2 (f - nf_{\rm out})^2 C_{\rm LQ}^2 + \left( \frac{1}{R_{\rm LQ}} + \frac{1}{r_{\rm on7}} + \frac{1}{r_{\rm on2}} \right)^2 \right]^{-1} \right\}, \end{aligned}$$

(27)

$$S_{\rm V,Q}^{\rm folded}(f) = \left| Z_{\rm Q}(f) \right|^2 \hat{i}_{\rm o7,\,f}^2.$$

(28)

In order to simplify the analysis, we assume the corner frequency of the voltage spectrum is lower than  $f_{out}/2$ . Thus, the phase noise can be written as

$$\ell_{Q,F}(f) = \frac{\pi^2}{2} \frac{f_{out}^2}{S_{LQ}} \frac{K_f C_{ox} W_7 \left[ k T \alpha \gamma \mu_n \left( V_{GS7} - V_{TH} \right) \right]^2}{L_7^3} \\ \times \frac{1}{f} \frac{1}{\left( R_{LQ} || r_{on7} || r_{on2} \right) C_{LQ}} \\ \times \frac{1}{4\pi^2 f^2 C_{LQ}^2 + \left( \frac{1}{R_{LQ}} + \frac{1}{r_{on7}} + \frac{1}{r_{on2}} \right)^2},$$

(29)

$$\ell_{\overline{Q},F}(f) = \frac{\pi^2}{2} \frac{f_{\text{out}}^2}{S_{\text{L}\overline{Q}}} \frac{K_{\text{f}} C_{\text{ox}} W_6 \left[ k T \alpha \gamma \mu_n \left( V_{\text{GS6}} - V_{\text{TH}} \right) \right]^2}{L_6^2} \\ \times \frac{1}{f} \frac{1}{\left( R_{\text{L}\overline{Q}} || r_{\text{on6}} || r_{\text{on5}} \right) C_{\text{L}\overline{Q}}} \\ \times \frac{1}{4\pi^2 f^2 C_{\text{L}\overline{Q}}^2 + \left( \frac{1}{R_{\text{L}\overline{Q}}} + \frac{1}{r_{\text{on6}}} + \frac{1}{r_{\text{on5}}} \right)^2}.$$

(30)

Fig. 5. Measured output voltage of single port (a) with 1.2-V-peak input signal at 10 GHz and (b) with 1.2-V-peak input signal at 50 MHz.

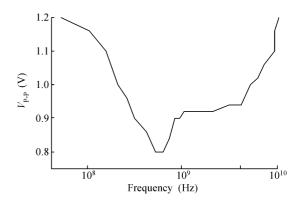

Fig. 6. Measurement of the sensitivity of the designed frequency divider.

#### 4.2.2. Total flicker phase noise

The flicker noise of M5 has no effect on port  $(\overline{Q})$  due to the analysis in 4.1.2. According to Eqs. (6) and (7), the total flicker phase noise spectrum can be written as:

$$\ell_{\text{total},F}(f) = \ell_{Q,F}(f) + \ell_{\overline{O},F}(f).$$

(31)

## 5. Measurement results analysis

The divide-by-two dividers have been implemented in the 90-nm CMOS process of IBM. The chip photograph is shown in Fig. 4. The chip area is  $360 \times 380 \,\mu\text{m}^2$  including the test circuits. The output waveforms are plotted in Fig. 5 for 10 GHz

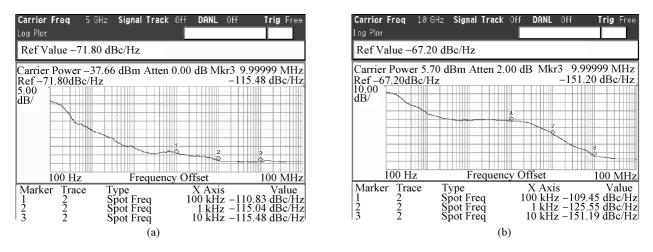

Fig. 7. Measured phase noise of single output port (a) with 1.2-V-peak input signal at 10 GHz and (b) 1.2-V-peak input signal at 10 GHz.

| Table 1. I | Phase noise | of single port | output signal | with input | signal at 10 GHz. |

|------------|-------------|----------------|---------------|------------|-------------------|

|            |             |                |               |            |                   |

| Frequency offset | PN <sub>total</sub> (dBc/Hz) | $PN_{in} + PN_m (dBc/Hz)$ | $PN_{fd} + PN_{tc} + PN_{sp} (dBc/Hz)$ | $PN_{fd} + PN_{tc} (dBc/Hz)$ |

|------------------|------------------------------|---------------------------|----------------------------------------|------------------------------|

| 100 kHz          | -110.83                      | -112.45                   | -123.90                                | -139.83                      |

| 1 MHz            | -115.04                      | -128.56                   | -123.24                                | -159.83                      |

| 10 MHz           | -115.48                      | -154.19                   | -123.48                                | -179.83                      |

| Table 2. Comparison with published results. |                                         |          |                   |       |  |  |  |  |

|---------------------------------------------|-----------------------------------------|----------|-------------------|-------|--|--|--|--|

| Technology                                  | Operating frequency Phase noise @ 1 MHz |          | Power consumption | FOM   |  |  |  |  |

|                                             | range (GHz)                             | (dBc/Hz) | (mW)              | (dB)  |  |  |  |  |

| 90 nm CMOS SOI, Ref. [8]                    | 13–34                                   | -127     | 60                | 115   |  |  |  |  |

| 90 nm CMOS SOI, Ref. [9]                    | 5–66                                    | -102     | 51                | 89    |  |  |  |  |

| 90 nm CMOS, Ref. [1]                        | 2-35.5                                  | -124.6   | 28.8              | 109.2 |  |  |  |  |

| 90 nm CMOS SOI, Ref. [10]                   | 65-81                                   | -112.6   | 2.75              | 87    |  |  |  |  |

| 90 nm CMOS, this work                       | 0.05–11                                 | -159.8   | 9.12              | 139.4 |  |  |  |  |

and 50 MHz input sinusoid signals with 1.2-V peak. The measured minimum input sensitivity  $V_{P-P}$  versus the input frequency of the frequency divider is plotted in Fig. 6. Above the minimum input voltage reliable operation is guaranteed. The minimum input voltage of the frequency dividers is less than 1.2 V in the frequency range of 0.05–10 GHz. The 1.2-V-peak input signal at the maximum operating frequency and minimum operating frequency are needed for the frequency divider. The measured power dissipation changes from 6.48 to 9.12 mW with the input signal frequency from 50 MHz to 10 GHz.

The phase noise of the output signal and input signal is measured by means of a spectrum analyzer. The measured results are shown in Fig. 7. From Fig. 7(a), we can see that the phase noise does not always decrease with increasing offset frequency. The results of measuring include the phase noise of the input signal ( $PN_{in}$ ), the phase noise of the sampling effect ( $PN_{sp}$ ), the phase noise of the measuring instrument ( $PN_{mi}$ ), the phase noise of test circuits of the designed frequency divider ( $PN_{fd}$ ). Among them,  $PN_{fd}$ ,  $PN_{in}$  and  $PN_{tc}$  strictly increase with increasing operating frequency, the effect of  $PN_{sp}$  increases with decreasing operating frequency, and  $PN_{mi}$  is constant. The relationship between them is

$$PN_{total} = PN_{fd} + PN_{in} + PN_{sp} + PN_{mi} + PN_{tc}.$$

(32)

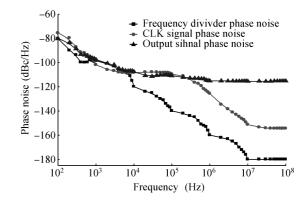

Fig. 8. Measured phase noise with 1.2-V-peak input signal at 10 GHz.

In practice, we cannot isolate  $PN_{tc}$  from  $PN_{fd}$ , thus, the result of the analysis contains  $PN_{tc}$  and  $PN_{fd}$ . On further analysis of the measured results of phase noise, the measured phase noise floor is equal to the sum of the essential phase noise floor replication. The essential floor phase noise is white noise and uncorrelated with frequency offset according to the analysis of part 4. Based on the analysis of Ref. [7], we can estimate the phase noise floor. From Fig. 7(a) and Eqs. (29)–(31), we can see the slope of the phase noise is approximately –20 dBc/dec and the frequency corner is nearby 10 MHz. Thus, we get Fig. 8 and Table 1. From Fig. 8, we can see the output signal phase

noise is 4.6 dB less than the clk signal phase noise at 100 Hz offset. The more the frequency offset increases, the larger the phase noise of the sampling effect is. Thus, the phase noise of the output signal begins to be larger than the phase noise of the CLK signal at 1 MHz offset nearby and the output signal phase noise reaches the floor phase noise at 1 MHz offset.

## 6. Conclusion

A modified frequency divider architecture employing a novel D latch is designed and realized. The D latch requires only a single clock signal and uses a switch transistor with dynamic loading to increase the bandwidth at low supply voltage. The frequency divider prototype achieves an operating frequency range of 50 MHz to 10 GHz at 1.2 V supply voltage using the IBM 90-nm CMOS process. The frequency divider consumes only a power of 9.12 mW. The phase noise of the frequency divider is -159.83 dBc/Hz at 1 MHz offset from the 5 GHz carrier. A useful analytical expression to accurately predict the bandwidth and phase noise is presented and validated by measurement. The design presents a viable solution to realize the high spectrum purity and wideband divider with low supply voltage. This technique is still not realized with the existing divider design. Compared with other recently published results using the 90-nm CMOS process, the designed frequency divider shows the best FOM<sup>[4]</sup>, as shown in Table 2. The presented frequency divider is particularly suited for ultra wideband, low phase noise and low power applications.

### Acknowledgement

The authors would like to thank Yan Zhao for the help and

support. Technology access from IBM is also appreciated.

## References

- Cheema H M, Mahmoudi R, van Roermund A, et al. A Ka band, static, MCML frequency divider, in standard 90 nm CMOS LP for 60 GHz applicatons. IEEE Radio Frequency Integrated Circuit Symposium, 2007: 541

- [2] Wong J M C, Cheung V S L, Luong H C. A 1-V 2.5-mW 5.2-GHz frequency divider in a 0.35-µm CMOS Process. IEEE J Solid-State Circuits, 2003, 38(10): 1643

- [3] Razavi B, Lee K F, Yan R H. A 13.4-GHz CMOS frequency divider. ISSCC Dig Tech, Feb 1994: 176

- [4] Levantino S, Romano L, Pellerano S, et al. Phase noise in digital frequency dividers. IEEE J Solid-State Circuits, 2004, 39(5): 775

- [5] Egan W F. Modeling phase noise in frequency dividers. IEEE Trans Ultrason, FErroelectr, Freq Contr, 1990, 37: 307

- [6] Kroupa V F. Jitter and phase noise in frequency dividers. IEEE Trans Instrum Measure, 2001, 50: 1241

- [7] Apostolidou M, Baltus P G M, Vaucher C S. Phase noise in frequency divider circuits. IEEE International Symposium on Circuits and Systems, 2008: 2538

- [8] Sanduleanu M A T, Ionita R, Vladimirescu A. A 34 GHz/1 V prescalar in 90 nm CMOS SOI. Proceedings of the 31st European Solid-State Circuits Conference, Sept 2005: 109

- [9] Plouchart J O, Kim J, Karam V, et al. Performance variations of a 66 GHz static CML divider in 90 nm CMOS. IEEE International Solid-State Circuits Conference, Feb 2006: 526, 671

- [10] Plouchart J O, Kim D, Kim J, et al. A 1.2 V 15.6 mW 81 GHz 2 : 1 static CML frequency divider with a band-pass load in a 90 nm SOI CMOS technology. IEEE Compound Semiconductor Integrated Circuit Symposium, 2007: 1