# Effect of trapped charge accumulation on the retention of charge trapping memory\*

Jin Rui(金锐), Liu Xiaoyan(刘晓彦)<sup>†</sup>, Du Gang(杜刚), Kang Jinfeng(康晋锋), and Han Ruqi(韩汝琦)

(Institute of Microelectronics, Peking University, Beijing, 100871, China)

**Abstract:** The accumulation process of trapped charges in a TANOS cell during P/E cycling is investigated via numerical simulation. The recombination process between trapped charges is an important issue on the retention of charge trapping memory. Our results show that accumulated trapped holes during P/E cycling can have an influence on retention, and the recombination mechanism between trapped charges should be taken into account when evaluating the retention capability of TANOS.

**Key words:** charge accumulation; charge trapping memory; retention characteristic **DOI:** 10.1088/1674-4926/31/12/124016 **EEACC:** 7220J; 7340N

### 1. Introduction

Conventional floating gate flash memory is approaching scaling limits beyond 45 nm generation for its cell-to-cell interference and decreased coupling ratio. Due to its desirable features with CMOS processes compatibility, pinhole immunity, good retention capability, and scalability, charge trapping memory (CTM) is an attractive candidate for next generation non-volatile memory. As one of the most promising CTM structures, TaN/Al2O3/SiN/SiO2/Si (TANOS) has received much attention in recent years<sup>[1,2]</sup>. In TANOS, due to the use of high-k blocking oxide  $(Al_2O_3)$ , the electric field across the tunnel oxide increases and relatively thicker tunnel oxide can be used to improve data retention. Moreover, TaN metal with high work function and a high-k blocking oxide reduces the gate injection current. So the TANOS structure can achieve longer data retention and lower program/erase voltage than the conventional Si/SiO<sub>2</sub>/SiN/SiO<sub>2</sub>/Si (SONOS) structure. However, reliability characteristics, including data retention and endurance, are still a problem. The characteristic degradation of CTM after P/E cycling is one of the major issues for its further mass production. In order to improve TANOS performance and to design an optimized cell, a comprehensive investigation of the physical mechanisms responsible for the reliability issues is necessary. In this work, the accumulation process of trapped charges in the TANOS cell during P/E cycling is investigated. With a trapped charge recombination mechanism implemented in our simulator<sup>[3]</sup>, the influence of trapped charge, especially trapped holes, during P/E cycles on TANOS retention is evaluated. An understanding of the effect of trapped charge accumulation and recombination on the retention properties is helpful to understand the reliability characteristics of CTM and allows the optimization of CTM.

## 2. Device structure and simulation method

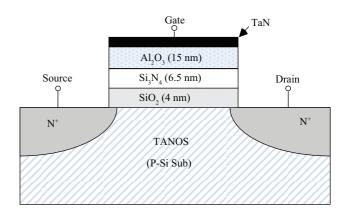

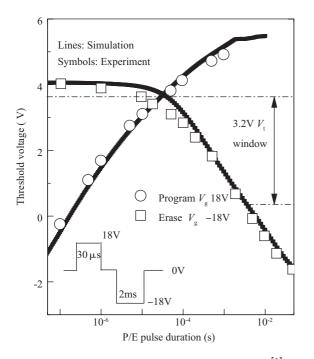

Figure 1 shows the TANOS structure used in the simulation. The tunnel oxide (SiO<sub>2</sub>), charge storage layer (Si<sub>3</sub>N<sub>4</sub>) and blocking oxide (Al<sub>2</sub>O<sub>3</sub>) are 4, 6.5 and 15 nm, respectively. The physical model parameters used for simulation are verified and calibrated by the experimental data<sup>[1]</sup> and are shown in Fig. 2. The trap density is 4.2 and  $0.8 \times 10^{19}$  cm<sup>-3</sup> for electrons and holes, respectively, and the trap depth for both electrons and holes is 1.9 V. Other physical parameters are the same as in Ref. [3].

To investigate the accumulation process of trapped charges in a TANOS cell after P/E cycles, we first determined the gate voltage P/E pulse sequences. According to the NAND SONOS memory operation rule, every erase operation is preceded by a program operation to bring all of the cells in the same block

Fig. 1. Cross section of the TANOS structure with  $Al_3O_3$  (15 nm)/  $Si_3N_4$  (6.5 nm)/SiO<sub>2</sub> (4 nm) and a TaN gate.

Received 2 February 2010, revised manuscript received 29 July 2010

© 2010 Chinese Institute of Electronics

The programming, erasing and retention characteristics of TANOS are simulated by combining the device simulation tool DESSIS and a self-consistent CTM simulator developed in our previous work<sup>[3]</sup>. Various physical models accounting for carrier transport, tunneling, trapping/detrapping are implemented in the CTM simulator, including DT/F-N tunneling<sup>[4]</sup>, trap assisted tunneling<sup>[5]</sup>, charge capture<sup>[6]</sup>, recombination<sup>[7]</sup>, thermal excitation<sup>[8]</sup>, Poole-Frenkel effect<sup>[9]</sup> and local accumulated free carriers<sup>[10]</sup>. A self-consistent method is employed to refresh the barrier shape by solving the Poisson equation during simulation of all types of operations of CTM devices efficiently.

<sup>\*</sup> Project supported by Samsung Electronics Co. Ltd. (Nos. 20060001050, 2006CB302705).

<sup>†</sup> Corresponding author. Email: xyliu@ime.pku.edu.cn

Fig. 2. Comparing the simulation and experimental data<sup>[1]</sup> of P/E operation of TANOS. The corresponding programming and erasing pulses are 30  $\mu$ s and 2 ms, respectively, when the V<sub>t</sub> window is 3.2 V.

to the same state. In other words, every cell in the same block is always erased to a low threshold state before programming operation. After the erasing operation, the cell is programmed to H state by a high gate voltage or to L state by a 0 V gate voltage. Here the H state and L state correspond to a high threshold state and a low threshold state.

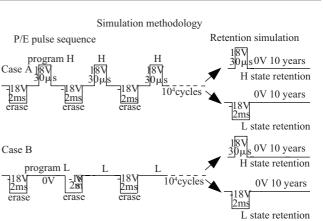

During simulation, the threshold voltage ( $V_t$ ) window is fixed to 3.2 V, which corresponds to a 30  $\mu$ s, 18 V programming pulse and 2 ms, -18 V erasing pulse, as shown in Fig. 2. Two extreme operation of P/E cycles, case A and B, as shown in Fig. 3, are used to simulate the P/E accumulation process of trapped charges in the TANOS cell, which correspond to the cell always being programmed H and L states, respectively.

For case A of the P/E cycle, as shown in Fig. 3, the cell is always programmed to a high threshold state (H) after each erasing, and various numbers of P/E cycles are simulated up to  $10^4$  times. For case B of the P/E cycle, as shown in Fig. 3, the cell is always programmed to a low threshold state (L) after each erasing, and various numbers of P/E cycles are simulated up to  $10^4$  times. The number of trapped electrons and holes after each P/E cycle, in both cases, are calculated and saved as the initial state for the following P/E operation.

The data retention properties after  $10^4$  P/E cycles are investigated and compared with the fresh case with only 1 P/E cycle. Due to different trapped charge densities after different cases of P/E cycles, the effect of the accumulation process of trapped charges in the TANOS cell on the retention can be evaluated.

#### 3. Results and discussion

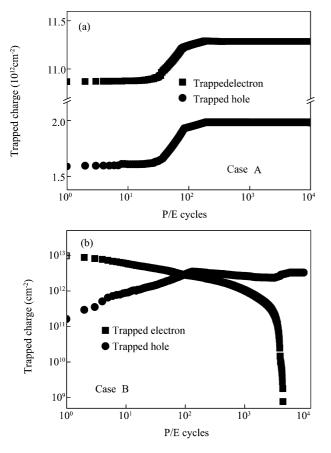

Trapped charge accumulation processes with various P/E cycles in case A and case B are illuminated in Fig. 4. In case A, the TANOS cell is always programmed to the H state after erasing. It is clear from the figure that the density of trapped elec-

Fig. 3. Two kinds of P/E pulse sequence in the simulation. Case A: the cell is always programmed to the H state. Case B: the cell is always programmed to the L state. After  $10^4$  P/E cycles, the cell is programmed to the H state or L state to simulate the retention property.

trons and holes increases with the P/E operation number until reaching saturation. This can be explained by the fact that some trapped electrons and trapped holes are always left in the charge storage layer (CTL) after every P/E cycle. When all of the trapped states in CTL are occupied, the trapped charge density stops increasing and shows saturation. In case B the TANOS cell is always programmed to the L state and sequential erasing pulses are performed on the gate before 0V programming operation. During the erasing operation, trapped electrons in the CTL recombine with injected holes and trapped holes. So in Fig. 4, after 10<sup>4</sup> erasing pulses, a large number of trapped holes accumulate in the CTL and there are almost no trapped electrons left.

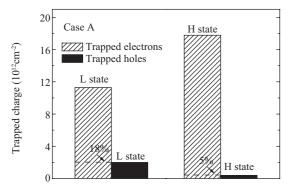

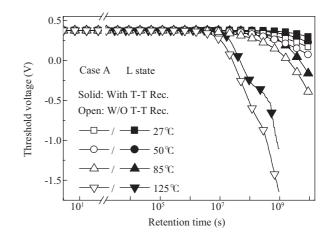

After 10<sup>4</sup> P/E cycles, the TANOS cell is programmed to the H or L state, as shown in Fig. 3, and then trapped charge densities are saved as the initial state to evaluate the retention property of the H or L state. Figure 5 shows the density of the trapped charges at the H and L state after 10<sup>4</sup> P/E cycles in case A. From the comparison in the figure, the trapped hole density in the CTL after 10<sup>4</sup> P/E cycles is up to 18% of trapped electrons at the L state. Thus the recombination process between trapped electrons and holes become unneglectable when evaluating the cell retention after P/E cycles. This can also be understood in Fig. 6, which shows the retention characteristic in the L state and its temperature effect. The effect of the recombination process between trapped electrons and holes is obvious, which weakens the effect of de-trapping. From the comparison, without considering recombination, leads to underestimation of the retention capability. Due to its temperature effect, recombination is more important, especially at high temperatures. Hence, due to the accumulation of trapped charges, the effect of the recombination process between the trapped charges on the L state retention capability is important. While in the H state after  $10^4$  P/E cycles, trapped holes are only 5% of trapped electrons, which is shown in Fig. 5. This is the result of the recombination process during programming. Thus the probability of recombination between trapped charges is much less than in the L state and there is no obvious change for the H state retention after P/E cycles.

When evaluating the retention characteristic after a P/E cy-

Fig. 4. Trapped charge accumulation processes with various P/E cycles for cases A and B.

Fig. 5. Trapped charge density in case A at the H state and the L state after  $10^4$  P/E cycles.

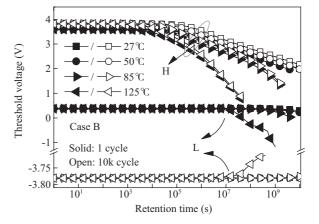

cle of case B, the TANOS cell is also programmed to the H or L state after P/E cycles, as shown in Fig. 3. At the L state, after  $10^4$  erasing operation, only trapped holes are left in the CTL. The recombination process between the trapped charges is not so important here as in case A. On the other hand, the accumulated holes during the P/E cycles affect the L state threshold obviously. The retention characteristic of case B is shown in Fig. 7. By comparison between the retention after 1 cycle and  $10^4$  cycles, it is shown that the L state threshold voltage decreases and the Vt window after  $10^4$  P/E cycles is about 4 V larger than the initial one. The reason is the net charge density variety due to the accumulation of trapped holes. This phenomenon is a potential cause of program and read failure. To prevent un-

Fig. 6. L state retention characteristic at various temperatures with/without recombination after  $10^4$  P/E cycles of case A.

Fig. 7. TANOS retention characteristic at different baking temperatures with 1 and  $10^4$  P/E cycles for case B where the cell always stores L.

wanted erasing operation and threshold voltage shift, the periphery circuits should be optimized for threshold verification and a programming/erasing algorithm. While in the H state, accumulated trapped holes have no effect on the H state programming. Because the recombination process during the programming operation is included, most trapped holes recombine with injected electrons. So there is no obvious change between the H state retention of 1 cycle and  $10^4$  cycles.

## 4. Conclusion

In this work, numerical simulation work is performed to evaluate the effect of trapped charge accumulation and its effect on the retention of the TANOS cell. Through two kinds of P/E pulse test, the impacts of trapped charge accumulation under extreme conditions on CTM retention characteristics are investigated. Our results show that accumulated trapped holes during P/E cycling can have an influence on the retention and recombination mechanism between trapped charges, which should be taken into account when evaluating the retention capability of TANOS.

#### References

[1] Park Y, Choi J, Kang C, et al. Highly manufacturable 32 Gb

multi-level NAND flash memory with 0.0098  $\mu$ m<sup>4</sup> cell size using TANOS (Si–oxide–Al<sub>2</sub>O<sub>3</sub>–TaN) cell technology. IEDM Tech Dig, 2006: 29

- [2] Lee C H, Choi J, Park Y, et al. Highly scalable NAND flash memory with robust immunity to program disturbance using symmetric inversion-type source and drain structure. VLSI Tech Dig, 2008 : 118

- [3] Song Y C, Liu X Y, Wang Z Y, et al. Evaluating the effects of physical mechanisms on the program, erase and retention in the charge trapping memory. Proc SISPAD, 2008: 41

- [4] Schenk A, Herser G. Modeling and simulation of tunneling through ultra-thin gate dielectrics. J Appl Phys, 1997, 81(12): 7900

- [5] Wu J, Register L F, Rosenbaum E. Trap-assisted tunneling current through ultra-thin oxide. Proc IPRS, 1999: 389

- [6] McWhorter P J, Miller S L, Dellin T A. Modeling the memory retention characteristics of silicon-nitride-oxide-silicon nonvolatile transistors in a varying thermal environment. J Appl Phys, 1990, 68: 1902

- [7] Song Yuncheng, Liu Xiaoyan, Du Gang, et al. Carriers recombination processes in charge trapping memory cell by simulation. Chinese Physics B, 2008, 17(7): 2678

- [8] Wang Y, White M H. An analytical retention model for SONOS nonvolatile memory devices in the excess electron state. Solid-State Electron, 2005, 49: 97

- [9] Manzini S. Electronic process in silicon nitride. J Appl Phys, 1987, 62: 3278

- [10] Song Yuncheng, Liu Xiaoyan, Zhao Kai, et al. Investigation of local accumulated free carriers in charge trapping memory. Silicon Nanoelectronics Workshop, 2008