# A low-voltage low-power CMOS voltage reference based on subthreshold MOSFETs

Wang Honglai(王洪来)<sup>1,†</sup>, Zhang Xiaoxing(张小兴)<sup>1</sup>, Dai Yujie(戴宇杰)<sup>1</sup>, Lü Yingjie(吕英杰)<sup>1</sup>, Toshimasa Matsuoka<sup>2</sup>, Wang Jun<sup>2</sup>, and Kenji Taniguchi<sup>2</sup>

<sup>1</sup>Institute of Microelectronics, Nankai University, Tianjin 300457, China

<sup>2</sup>Department of Electrical, Electronic and Information Engineering, Osaka University, 2-1 Yamadaoka, Suita, Osaka, 565-0871, Japan

**Abstract:** This paper describes a CMOS voltage reference using only resistors and transistors working in weak inversion, without the need for any bipolar transistors. The voltage reference is designed and fabricated by a 0.18  $\mu$ m CMOS process. The experimental results show that the proposed voltage reference has a temperature coefficient of 370 ppm/°C at a 0.8 V supply voltage over the temperature range of -35 to 85 °C and a 0.1% variation in supply voltage from 0.8 to 3 V. Furthermore, the supply current is only 1.5  $\mu$ A at 0.8 V supply voltage.

Key words: bandgap reference; CMOS; subthreshold DOI: 10.1088/1674-4926/32/8/085009 EEACC: 2570D

# 1. Introduction

A precision voltage reference circuit is very important in the design of many mixed-signal and analog integrated circuits, such as oscillators, comparators, low-dropout regulators (LDOs) and data converters. The voltage references are required to be stabilized over process, voltage, and temperature variations and are also expected to be implemented in the standard fabrication process.

Undoubtedly, a bandgap voltage reference, which was firstly proposed by Widlar<sup>[1]</sup> and was further developed by Kuijk<sup>[2]</sup>, is the most popular high performance voltage reference used in integrated circuits today. Moreover, the bandgap references that are less than 1 V are used more and more in low voltage applications. Therefore, many researchers have also developed bandgap voltage references that are less than 1 V. Banba and Leung<sup>[3,4]</sup> proposed two bandgap voltage references. The concept is basically a current-mode method to scale down the bandgap reference voltage by a factor defined by a resistor ratio. Jiang<sup>[5]</sup> proposed a bandgap reference using a transimpedence amplifier. However, all of the above bandgap voltage references require big area diodes or parasitic bipolar junction transistors (BJTs). In this paper, we introduce a new low-voltage low-power voltage reference based on subthreshold MOSFETs. The proposed bandgap voltage reference can operate from a supply as low as 0.8 V and the supply current is only 1.5  $\mu$ A.

## 2. Conventional bandgap voltage reference

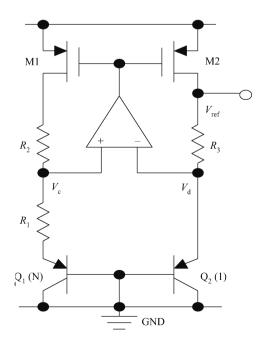

Figure 1 shows the structure of the conventional bandgap reference. M1 and M2 have the same transistor size. The input voltages of the error amplifier,  $V_c$  and  $V_d$ , are controlled to keep the same voltage and there is  $R_2 = R_3$ .

So the voltage across the resistor  $R_1$ , which is the forward voltage difference between the two bipolar transistors  $Q_1$  and  $Q_2$ , can be shown as

$$\Delta V_{\rm be} = V_{\rm be2} - V_{\rm be1} = V_{\rm t} \ln N. \tag{1}$$

The output reference voltage  $V_{ref}$  can be expressed as

$$V_{\rm ref} = V_{\rm be2} + \frac{R_3}{R_1} V_{\rm t} \ln N.$$

(2)

Here, N is the emitter area ratio and  $V_t$  is the thermal voltage. The  $V_t \ln(N) R_3/R_1$  term is proportional to the absolute

Fig. 1. The conventional bandgap reference circuit.

© 2011 Chinese Institute of Electronics

<sup>†</sup> Corresponding author. Email: wanghonglai@mail.nankai.edu.cn Received 18 November 2010, revised manuscript received 25 April 2011

Fig. 2. Structure of the proposed bandgap reference.

temperature (PTAT), which is used to cancel the negative temperature coefficient of  $V_{be}$ . Therefore, we can choose a proper ratio of resistors to obtain an output reference voltage with low temperature coefficient.

# 3. Circuit design of the proposed bandgap voltage reference

Recently, a study of the MOSFET temperature behavior pointed out clearly that below a certain technology-dependent bias point, the gate–source voltage of a MOSFET, biased with a fixed drain current, decreases with temperature in a quasilinear fashion<sup>[6, 7]</sup>. For the MOSFET operating in the weakinversion region, with the condition of  $V_{\rm DS} \ge 3V_{\rm t}$ , its drain current can be given as

$$I_{\rm d} = K \mu V_{\rm t}^2 \sqrt{\frac{q \varepsilon_{\rm si} N_{\rm ch}}{2\phi_{\rm s}}} \exp \frac{V_{\rm GS} - V_{\rm TH} - V_{\rm OFF}}{n V_{\rm t}}, \qquad (3)$$

where  $K = W_{\text{eff}}/L_{\text{eff}}$  is the transistor aspect ratio,  $\mu$  is the mobility of the carrier in the channel,  $\varepsilon_{\text{si}}$  is the permittivity of silicon,  $N_{\text{ch}}$  is the channel doping concentration,  $\phi_{\text{s}}$  is the surface potential, *n* is the subthreshold slope factor,  $V_{\text{OFF}}$  is a corrective constant term used in BSIM3v3 models<sup>[8]</sup> and  $V_{\text{TH}}$  is the threshold voltage. Furthermore, for a given drain current, the relation between gate–source voltage  $V_{\text{GS}}$  and  $V_{\text{TH}}$  as a function of temperature is

$$V_{\rm GS}(T) = V_{\rm TH}(T) + V_{\rm OFF} + \frac{n(T)}{n(T_0)} \times \left[ V_{\rm GS}(T_0) - V_{\rm TH}(T_0) - V_{\rm OFF} \right] \frac{T}{T_0}.$$

(4)

The threshold voltage, which has a negative temperature coefficient, can be expressed as<sup>[9]</sup>

$$V_{\rm TH}(T) = V_{\rm TH}(T_0) + \alpha_{\rm VT}(T - T_0)$$

=  $V_{\rm TH}(T_0) + \alpha_{\rm VT}T_0\left(\frac{T}{T_0} - 1\right)$

=  $V_{\rm TH}(T_0) + K_{\rm T}\left(\frac{T}{T_0} - 1\right),$  (5)

where  $\alpha_{VT}$  is the temperature coefficient of the threshold voltage and it is generally between -4 and -1 mV/°C. Assuming that n(T) has small variations with temperature, we can get

$$V_{\rm GS}(T) \approx V_{\rm GS}(T_0) + [K_{\rm T} + V_{\rm GS}(T_0) - V_{\rm TH}(T_0) - V_{\rm OFF}] \left(\frac{T}{T_0} - 1\right).$$

(6)

From Eq. (6), we can see that  $V_{\rm GS}$  decreases with temperature and has a similar temperature performance to  $V_{\rm be}$ , so we can generate the reference voltage with the  $V_{\rm GS}$  voltage instead of using the  $V_{\rm be}$  voltage.

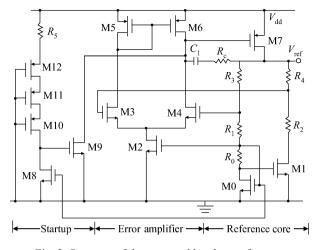

Figure 2 shows the complete schematic of the proposed voltage reference. The startup circuit is composed of M8–M12 and  $R_5$ . M2–M6 form the error amplifier. M0, M1 and  $R_0-R_4$  are the core circuit, which can generate the reference voltage, and there is  $R_3 = R_4$ .  $C_1$  and  $R_C$  are the compensation capacitor and resistor. From Eq. (3), the drain current of M0 and M1 can be expressed as

$$I_{\rm d0} = K_0 \mu_{\rm n} V_{\rm t}^2 \sqrt{\frac{q\varepsilon_{\rm si} N_{\rm ch}}{2\phi_{\rm s}}} \exp{\frac{V_{\rm GS0} - V_{\rm TH} - V_{\rm OFF}}{nV_{\rm t}}}, \quad (7)$$

$$I_{\rm d1} = K_1 \mu_{\rm n} V_{\rm t}^2 \sqrt{\frac{q \varepsilon_{\rm si} N_{\rm ch}}{2\phi_{\rm s}}} \exp{\frac{V_{\rm GS1} - V_{\rm TH} - V_{\rm OFF}}{nV_{\rm t}}}, \quad (8)$$

where  $K_0 = W_0/L_0$ ,  $K_1 = W_1/L_1$  and  $K_1 = NK_0$ . Because the current  $I_{d0} = I_{d1}$ , we have

$$V_{\rm GS0} - V_{\rm GS1} = nV_{\rm t}\ln N.$$

(9)

From Fig. 2, we can see that

$$V_{\rm GS0} = V_{\rm GS1} + I_{\rm d0} R_0. \tag{10}$$

From Eqs. (9) and (10), we have

$$I_{\rm d0} = \frac{V_{\rm GS0} - V_{\rm GS1}}{R_0} = \frac{nV_{\rm t}\ln N}{R_0}.$$

(11)

Then the voltage across the resistors  $R_1$  and  $R_3$  is

$$V_{\rm R1} + V_{\rm R3} = I_{\rm d0}(R_1 + R_3) = \frac{R_1 + R_3}{R_0} n V_{\rm t} \ln N,$$

(12)

where  $(R_1 + R_3)/R_0$  is the temperature independent resistor ratio, so the voltage is proportional to the absolute temperature. From Eqs. (6) and (12), we can see that the expression for the reference voltage is

$$V_{\rm ref} = V_{\rm GS0} + V_{\rm R1} + V_{\rm R3} = V_{\rm GS}(T_0) + [K_{\rm T} + V_{\rm GS}(T_0) - V_{\rm TH}(T_0)] \left(\frac{T}{T_0} - 1\right) + \frac{R_1 + R_3}{R_0} n V_{\rm t} \ln N.$$

(13)

So we can choose a proper resistor ratio of  $(R_1 + R_3)/R_0$  to achieve the temperature compensation.

In the voltage reference proposed by Giustolisi<sup>[6]</sup>, the voltage reference is generated by the  $V_{GS}$  of the MOS transistors working in the subthreshold region. The voltage reference proposed by Leung<sup>[10]</sup> is based on the  $\Delta V_{GS}$  of a NMOS transistor

Fig. 3. Micrograph of the proposed bandgap reference.

Fig. 4. Measured and simulated temperature dependence of the voltage reference.

and a PMOS transistor. In our design, we generated the voltage reference with the  $\Delta V_{GS}$  of two NMOS transistors, which are working in the subthreshold region. Furthermore, an error amplifier is used to improve the performance of the voltage reference. As shown in Table 1, the PSRR and line regulation performance of the proposed voltage reference are much better than the voltage reference previously reported in the literature.

#### 4. Experimental results

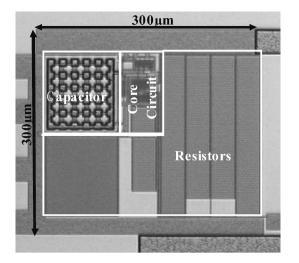

The proposed voltage reference is designed and fabricated by a 0.18  $\mu$ m CMOS process, as shown in Fig. 3. The proposed circuit occupies a 0.09 mm<sup>2</sup> chip area. At room temperature, the supply current is 1.5  $\mu$ A at a 0.8 V supply voltage. The chip area is very small and the supply current is extremely low due to the simple circuit structure.

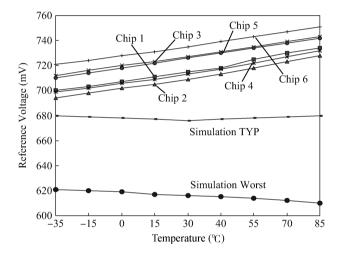

As shown in Fig. 4, the measured temperature coefficients of the proposed reference circuit for 6 chips at a 0.8 V supply are about 370 ppm/°C, approximately 6 times the circuit simulation result at typical condition of 57 ppm/°C, and even more than twice that in the worst condition of 158 ppm/°C. Therefore, it can be seen that except for resistance mismatch or the

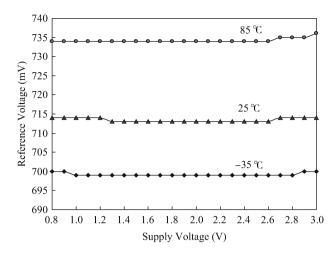

Fig. 5. Measured supply voltage dependence of the voltage reference at different temperatures of chip 1.

transistors' characteristic fluctuation possibly caused by process variations, another more important reason is that the simulation model is not so accurate as to agree rather well with experiment, especially for the transistors working in the weak inversion region. But fortunately, this inconsistency can be reduced by the adjustment of device sizes according to Eq. (3). A better temperature coefficient can be achieved by properly adjusting the resistance ratio of  $(R_1 + R_3)/R_0$  in the circuit design or by using resistance trimming technology. Figure 5 shows the reference voltage dependence of the supply voltage, and the calculated line regulation is about 0.3 mV/V at room temperature for the supply voltage from 0.8 to 3 V.

The power-supply rejection ratio (PSRR) is used to measure the ability of signal suppression of a bandgap, and it is given by PSRR =  $20 \lg |v_o(f)/v_{in}(f)|$ , where  $v_{in}(f)$  and  $v_o(f)$ are the input signal and the output signal, respectively. The spectrum analyzer with a high input impedance ( $R_{in} = 1 M\Omega$ ) is used to measure the signal level at the input and output of the bandgap, and the input sine wave at the input of the bandgap is 0.1 V. The experimental results show that the PSRR is -67 dB @ 10 kHz at a 1 V supply voltage.

Table 1 summarizes the performance of the proposed voltage reference compared to the voltage reference previously reported in the literature and the conventional bandgap voltage reference based on the parasitic bipolar junction transistors.

## 5. Conclusion

In this paper, a low-voltage low-power CMOS voltage reference based on subthreshold MOSFETs has been introduced. It does not use any diodes or BJT. With a power supply voltage of 0.8 V, the proposed voltage reference circuit presents an output voltage of 700 mV with a temperature coefficient of 370 ppm/°C over the temperature range of -35 to 85 °C. The power supply current of the whole circuit is only 1.5  $\mu$ A at room temperature. This circuit is suitable for low power, low voltage applications.

## Acknowledgments

The authors would like to thank the Osaka University

| Parameter                        | Conventional <sup>[11]</sup> | Ref. [6]    | Ref. [10]   | This work    |

|----------------------------------|------------------------------|-------------|-------------|--------------|

| Technology (µm)                  | 0.9                          | 1.2         | 0.6         | 0.18         |

| Supply voltage (V)               | 2.7-5.5                      | 1.2-4       | 1.4–3       | 0.8-3        |

| Supply current ( $\mu A$ )       | 300                          | 3.6         | 9.7         | 1.5          |

| Reference voltage (V)            | 1.236                        | 0.3         | 0.310       | 0.7          |

| Temperature coefficient (ppm/°C) | 85                           | 120         | 62          | 370*         |

| PSRR (dB)                        | -80 @10 kHz                  | −40 @ 5 kHz | −47 @ 1 kHz | −67 @ 10 kHz |

| Line regulation (%/V)            |                              |             | 0.225       | 0.036        |

| Area (mm <sup>2</sup> )          | _                            | 0.23        | 0.055       | 0.09         |

| Year                             | 1995                         | 2003        | 2003        | 2010         |

Table 1. Comparison of the voltage reference available in the literature.

\* The temperature coefficient performance can be improved by the trimming procedure or by modifying the transistors sizes of M1 and M2.

Global COE Program "Center for Electronic Devices Innovation" from the Ministry of Education, Culture, Sports, Science and Technology of Japan for sponsoring this work.

## References

- Widlar R J. New developments in IC voltage regulators. IEEE J Solid-State Circuits, 1971, 16(1): 2

- [2] Kuijk K E. A precision reference voltage source. IEEE J Solid-State Circuits, 1973, 8(3): 222

- [3] Banba H, Shiga H, Umezawa A, et al. A CMOS bandgap reference circuit with sub-1-V operation. IEEE J Solid-State Circuits, 1999, 34(5): 670

- [4] Leung K N, Mok P K T. A sub-1-V 15-ppm/°C CMOS bandgap voltage reference without requiring low threshold voltage device. IEEE J Solid-State Circuits, 2002, 37(4): 526

- [5] Jiang Y, Lee E K F. Design of low-voltage bandgap reference us-

ing transimpedance amplifier. IEEE Trans Circuits Syst II, 2000, 47(6): 552

- [6] Giustolisi G, Palumbo G, Criscione M, et al. A low-voltage lowpower voltage reference based on subthreshold MOSFETs. IEEE J Solid-State Circuits, 2003, 38(1): 151

- [7] Filanovsky I M, Allam A. Mutual compensation of mobility and threshold voltage temperature effects with applications in CMOS circuits. IEEE Trans Circuits Syst I, 2001, 48(7): 876

- [8] Cheng Y, Hu C. MOSFET modeling & BSIM3 user's guide. New York: Kluwer, 1999

- [9] Gray P R, Meyer R G. Analysis and design of analog integrated circuits. New York: John Wiley & Sons Inc, 1993

- [10] Leung K N, Mok P K T. A CMOS voltage reference based on weighted  $\Delta V_{GS}$  for CMOS low-dropout linear regulators. IEEE J Solid-State Circuits, 2003, 38(1): 146

- [11] Tham K M, Nagaraj K. A low supply voltage high PSRR voltage reference in CMOS process. IEEE J Solid-State Circuits, 1995, 30: 586