# SPICE compatible analytical electron mobility model for biaxial strained-Si-MOSFETs

Amit Chaudhry<sup>1,†</sup>, J. N. Roy<sup>2</sup>, and S. Sangwan<sup>1</sup>

<sup>1</sup>UIET, Panjab University, Chandigarh, India <sup>2</sup>Solar Semiconductro Pvt. Ltd, Hyderabad, India

**Abstract:** This paper describes an analytical model for bulk electron mobility in strained-Si layers as a function of strain. Phonon scattering, columbic scattering and surface roughness scattering are included to analyze the full mobility model. Analytical explicit calculations of all of the parameters to accurately estimate the electron mobility have been made. The results predict an increase in the electron mobility with the application of biaxial strain as also predicted from the basic theory of strain physics of metal oxide semiconductor (MOS) devices. The results have also been compared with numerically reported results and show good agreement.

Key words:mobility;SiGe; strained-Si; phonon; surface roughness; columbicDOI:10.1088/1674-4926/32/5/054001EEACC: 2520

# 1. Introduction

CMOS technology has contributed significantly to the microelectronics industry, thus playing an important role in the overall development of all of the countries. The performance and density of a CMOS chip can be improved through device scaling, which is inevitable as also propounded by Moore's law, which states that the transistor density of a CMOS chip doubles approximately after every one and a half years<sup>[1]</sup>. Continuing with Moore's law, the gate length of the MOSFET will eventually shrink to 10 nm in 2015<sup>[2]</sup>. Seeing the trend of down scaling, continuous improvements in VLSI MOSFET device models are required so that the exact behavior of deep submicron and nanometer scale MOSFETs can be described with accuracy. The reduction in carrier mobility is a major cause of drain current degradation. But as we scale down the MOSFET, carrier mobility decreases due to the high vertical electrical fields in the substrate. This reduces the speed of the device. To control these effects, strained silicon technology has evolved in the past few years as a replacement of silicon in substrate. An attempt has been made in this paper to analytically model the electron mobility. In detail, this paper deals with the physics of strained silicon MOSFET, presents the effect of strain on the silicon band structure, and gives some modeling issues in the strained silicon MOS technology.

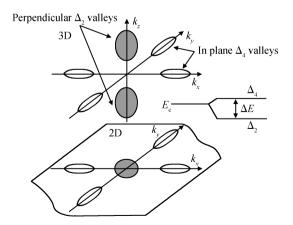

#### 2. Strain effect on mobility

When a layer of a crystal is grown over another layer, a strain is developed in the upper layer due to the mismatch of the lattice constants of two layers without decreasing the dimensions of the devices to achieve the high speeds without scaling down the devices. The strain is a very useful parameter in devices as carrier mobility significantly increases by altering the band structure at the channel. The alteration of band structure in the channel layer provides lower effective mass and also suppresses intervalley scattering, which is a prime cause of enhancement of carrier mobility and the drive current. The mobility becomes roughly twice that of conventional Si substrate<sup>[3]</sup>. The conduction band splitting has been shown in Fig. 1. Each energy level of silicon is composed of six energy states in three dimensions. These are named as two perpendicular  $\Delta_2$  states and four  $\Delta_4$  states parallel to the plane. When stress is applied, the  $\Delta_2$  states and  $\Delta_4$  states are split up into lower and higher energy states. This band alteration gives an alternative lower site for electrons to reside in, i.e.  $\Delta_4$ . The difference in the energy levels causes repopulation of the electrons. The effective mass of electrons in the lower energy states is less than the higher states. Due to this, the electron mobility increases. Besides this, the inter-valley phonon scattering between the lower and upper states is suppressed due to the strain induced larger energy difference. The mathematical equation (1) proves this theory. Mathematically, carrier mobility is

$$\mu = q\tau/m^*,\tag{1}$$

Fig. 1. Energy band splitting due to biaxial strain in conduction bands.

<sup>†</sup> Corresponding author. Email: amit\_chaudhry01@yahoo.com Received 23 November 2010, revised manuscript received 25 December 2010

where  $1/\tau$  = scattering rate and  $m^*$  = conductivity effective mass. The mobility is directly related to the carrier velocity v and applied external electric field E, as shown by

$$v = \mu E. \tag{2}$$

It can be seen that increasing the carrier mobility increases the velocity, which is directly proportional to the switching speed of the device and the drain current. This process is especially useful at nanometer scales where the carrier mobility is affected the most, as explained in Section 1.

#### 3. Modeling of electron mobility

Electron mobility is a very important parameter in the overall MOSFET modeling process. This is because parameters like drain current and hence trans-conductance strongly depend on mobility. There are three major scattering mechanisms that affect a MOSFET's inversion layer carrier mobility, as given below.

#### 3.1. Phonon scattering due to lattice vibrations

Phonon scattering is due to lattice vibrations. The scattering rate is found from the calculations carried out using the deformation potential, as reported in Ref. [5]. The main problem is calculation of the electrical field at the oxide/silicon interface. The phonon scattering is evaluated as

$$\mu_{\rm ph}^{-1} = (\mu_{\rm pho}\beta^{-1}) \left[ 1 + (E_{\rm s}/E_{\rm o})^{0.2\alpha} \right],\tag{3}$$

where  $\beta = 1 + a_1\{1 + (0.4a_1)^{b_1}\}^{-1/b_1}$ ,  $\alpha = 1 + a_2\{1 + (1.1a_2)^{b_2}\}^{-1/b_2}$ .  $\mu_{\text{pho}} = 1470 \text{ cm}^2/(\text{V}\cdot\text{s})$ ,  $E_0 = 7 \times 10^4 \text{ V/cm}$ ,  $a_1 = 11, b_1 = 15, a_2 = 3, b_2 = 25$  are the constants as obtained from Ref. [5].  $E_s =$  effective vertical electrical field from the substrate to the oxide.

# 3.2. Surface roughness scattering due to the microscopic roughness of the Si–SiO<sub>2</sub> interface

The microscopic roughness at the surface of the oxide/silicon interface causes a decrease in electron mobility due to scattering from the surface. Moreover, the electrical fields increasing due to the massive downscaling of the technology tend to pull the electrons towards the interface further. The empirical formula for the surface roughness of Ref. [5] is

$$\mu_{\rm sr} = \delta \times 10^{14} / E_{\rm s}^2,\tag{4}$$

where

$$\delta = \delta_o + a_3 \{1 + (a_3/\Delta \delta)^{b_3}\}^{-1/b_3}, \delta_o = 3.8, a_3 = 7, \Delta \delta = 2.1, b_3 = 15.$$

#### 3.3. Coulomb scattering due to impurity scattering

The coulomb mobility is calculated as

$$\mu_{\rm c}^{-1} = q C N_{\rm a} / Q_{\rm inv},\tag{5}$$

where  $C = 46 \times 10^{-9}$  V/cm,  $Q_{inv}$  is the inversion charge density and  $N_a =$  doping concentration (cm<sup>-3</sup>).

The total mobility of the electrons is calculated as follows from Mathiessen's rule,

$$\mu_{\text{Total}}^{-1} = \mu_{\text{ph}}^{-1} + \mu_{\text{sr}}^{-1} + \mu_{\text{c}}^{-1}.$$

(6)

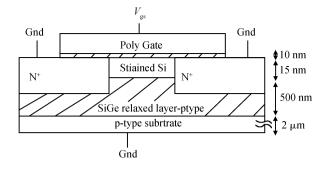

Fig. 2. Cross-sectional view of biaxially strained-Si–SiGe bulk-Si MOSFET.

#### 4. Calculation of effective electrical field

There is no proper analytical solution of Eqs. (3)–(5) in the existing literature<sup>[5, 6]</sup>. This may be due to the analytical formulations of inversion charge density, depletion charge density and threshold voltage of biaxial strained MOSFETs seldom being available in the literature. In this paper, we have solved all of these equations analytically and no approximations have been used. The first parameter in solving these equations is the surface electrical field.

The total charge density in the substrate (due to both the inversion region and the depletion region) is given by Gauss's law,

$$E_{\rm s} = (\eta Q_{\rm inv} + Q_{\rm depl}) / \varepsilon_{\rm Si} \varepsilon_0, \tag{7}$$

where  $\eta = 0.75$ , is the correction in inversion charge density in the (100) surface.  $Q_{inv}$  is the inversion charge density,  $Q_{depl}$  is the depletion charge density,  $\varepsilon_{Si}$  is the relative permittivity of silicon substrate, and  $\varepsilon_0$  is the air permittivity.

#### 4.1. Calculation of depletion charge density

The depletion charge density is given by

$$Q_{\rm depl} = q N_{\rm a} x_{\rm d},\tag{8}$$

where  $x_d$  is the depletion width in the substrate.  $x_d$  is calculated as dividing the MOS substrate region in three parts, such as (1) p-type silicon/silicon germanium interface; (2) silicon germanium interface/strained silicon layer interface; and (3) strained silicon/oxide layer interface.

#### 4.1.1. Hetero-interface I: p-type substrate and the SiGe relaxed layer p-type

Consider the MOSFET structure shown in Fig. 2. The depletion region extends in the p-type substrate and the SiGe relaxed layer. Let the thickness of SiGe relaxed layer be  $x_{SiGe}$  and the depletion region in the p-type substrate be  $x_s$ . Applying the Poisson equation at this interface, for getting the potential distribution in the substrate and keeping substrate at zero bias, we get in the limits from  $0 < x < x_d$  towards the oxide,

$$\mathrm{d}^2\phi/\mathrm{d}x^2 = qN_\mathrm{a}/\varepsilon_\mathrm{o}\varepsilon_\mathrm{Si}.\tag{9}$$

Integrating Eq. (9) by applying boundary conditions, the electrical field at the interface I is given by

$$\mathrm{d}\phi/\mathrm{d}x = -E_{\mathrm{Si}} = qN_{\mathrm{a}}x_{\mathrm{d}}/\varepsilon_{\mathrm{o}}\varepsilon_{\mathrm{Si}},\tag{10}$$

$$\phi_1(x) = q N_{\rm a} x^2 / 2\varepsilon_{\rm o} \varepsilon_{\rm Si}.$$

(11)

At  $x = x_d$ ,

$$\phi_1(x_d) = q N_a x_d^2 / 2\varepsilon_o \varepsilon_{\rm Si}, \qquad (12)$$

is the potential at the substrate and SiGe relaxed layer heterointerface. This can be called at the top of the substrate or at the bottom of the SiGe relaxed layer.

#### 4.1.2. Hetero-interface II: SiGe relaxed layer p-type and ptype strained Si

The SiGe relaxed layer is assumed to be of constant electrical field and hence no depletion region exists in this area. The electrical field in the hetero interface I is the same as at the hetero interface II. The electrical field is given in Eq. (10). Solving Poisson equation in the SiGe relaxed layer. Integrating Eq. (10) in the SiGe channel, from  $x = x_d$  to  $x = x_d + x_{SiGe}$ , and putting boundary conditions for the potential  $\phi_2$ , we get

$$\phi_2(x) - \phi_1(x_d) = q N_a x_d x / \varepsilon_o \varepsilon_{\text{Si}}, \qquad (13)$$

$$\phi_2(x_{\rm SiGe} + x_{\rm d}) = q N_{\rm a} x_{\rm d}^2 / 2\varepsilon_{\rm o} \varepsilon_{\rm Si} + q N_{\rm a} x_{\rm d} x_{\rm SiGe} / \varepsilon_{\rm o} \varepsilon_{\rm Si}.$$

# 4.1.3. Hetero-interface III: p-type strained Si and silicon oxide

The electrical field at the bottom of the strained silicon cap layer is the same as given by Eq. (10) due to the continuity of electrical fields at the hetero interface III. The electrical field at the strained silicon/oxide interface is calculated. Integrating Eq. (10) in the SiGe channel, from  $x = x_d$  to  $x = x_d + x_{SiGe} + x_{ssi}$ , and putting boundary conditions for the potential  $\phi_3$ , we get

$$\phi_{s}(x) - \phi_{1}(x_{d}) = qN_{a}x_{d}x/\varepsilon_{0}\varepsilon_{Si},$$

$$\phi_{s}(x_{d} + x_{SiGe} + x_{ssi}) = qN_{a}x_{d}x_{ssi}/\varepsilon_{0}\varepsilon_{Si} + qN_{a}x_{d}^{2}/2\varepsilon_{0}\varepsilon_{Si} + qN_{a}x_{d}x_{SiGe}/\varepsilon_{0}\varepsilon_{Si}.$$

(14)

Now,  $\phi_3(x_d + x_{SiGe} + x_{ssi})$  is the surface potential, which is constant and is equal to

$$\phi_{\rm ss} = 2\phi_{\rm f} - \Delta E_{\rm C}(x), \tag{15}$$

where  $\Delta E_{\rm C}(x)$  is the conduction band offset due to strain in the lattice and  $\phi_{\rm f}$  is the Fermi potential, a parameter which is a function of doping.  $\phi_{\rm f} = kT/q\ln(N_{\rm a}/n_{\rm i})$ , where  $n_{\rm i}$  is intrinsic carrier concentration, equals  $(N_{\rm c}N_{\rm v})^{1/2}\exp(-E_{\rm g}/2kT)$ . Using Eqs. (14) and (15) and solving the quadratic equation, we get the maximum depletion width in the substrate,

$$x_{\rm d} = -(x_{\rm SiGe} + x_{\rm ssi}) + \{(x_{\rm SiGe} + x_{\rm ssi})^2 + 2(\phi_{\rm ss}\varepsilon_{\rm Si}/qN_{\rm a})\}^{1/2}.$$

(16)

Using Eq. (16) in Eq. (8), we get the depletion charge density.

Table 1. Strained silicon MOSFET parameters used in simulation.

| 1                                             |                                    |

|-----------------------------------------------|------------------------------------|

| Parameter                                     | Value                              |

| Germanium content in SiGe relaxed layer       | 0-0.4                              |

| Relaxed SiGe film thickness t <sub>SiGe</sub> | 0–15 nm                            |

| Source/Drain and poly silicon doping          | $2 \times 10^{20} \text{ cm}^{-3}$ |

| Substrate doping                              | $5 \times 10^{17} \text{ cm}^{-3}$ |

| Gate oxide thickness                          | 8.0 nm                             |

| Work function of gate material                | 4.35 eV                            |

| Strained silicon film thickness $t_{si}$      | 0–15 nm                            |

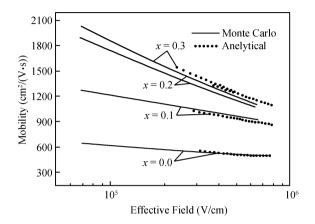

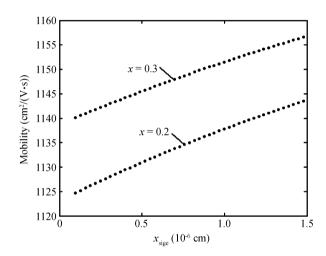

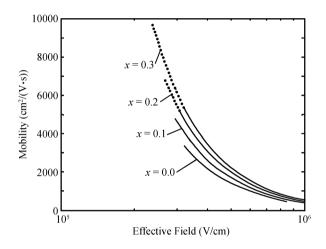

Fig. 3. Modeled results of electron phonon mobility with effective electrical field for strained-Si on  $Si_{1-x}Ge_x$  MOSFETs at room temperature. Reported results are shown by the black lines. Data calculated with the model developed in this paper are shown by the symbols.

#### 4.2. Modeling of inversion electron density

The inversion charge density including weak and strong inversion can be found by solving Poisson's Equation and applying the necessary boundary conditions. The total charge density is

$$Q_{\rm inv} = C_{\rm ox} \left( V_{\rm gs} - V_{\rm Ts} \right), \tag{17}$$

where  $C_{\text{ox}}$  is the oxide capacitance (F/m<sup>2</sup>),  $kT/q = V_{\text{t}} = 0.026$  V at room temperature,  $\phi_{\text{f}}$  is the Fermi potential in the substrate, equals  $(kT/q)\ln(N_{\text{a}}/n_{\text{i}})$ , and

$$V_{\rm Ts} = V_{\rm fbs} + \phi_{\rm ss} + \phi_{\rm ox}.$$

(18)

The flat band voltage for a metal gate strained silicon MOSFET is hence given by<sup>[7]</sup>

$$V_{\rm fbs} = \phi_{\rm m} - \{\chi_{\rm s} + E_{\rm g}^{\rm sige} - V_{\rm t} \ln(N_{\rm v}^{\rm sige}/N_{\rm a})\},$$

(19)

where  $\chi_s = 4.35 + 0.58x$ ,  $N_v^{\text{sige}} = 1.04 + x (0.6 - 1.04) \times 10^{19} \text{ cm}^{-3}$ ,  $\phi_{\text{ss}} = 2 \phi_{\text{f}} - \Delta E_{\text{g}}$ ,  $E_{\text{g}} - \Delta E_{\text{g}} = E_{\text{g}}^{\text{sige}}$ ,  $E_{\text{g}} = 1.12 \text{ eV}$ ,  $\Delta E_{\text{g}} = 0.4x$ ,  $\phi_{\text{oxs}} = qN_{\text{a}}x_{\text{d}}/C_{\text{ox}}$  obtained from Eq. (8). So, using Eqs. (8) and (17) in Eq. (7), we get the effective surface electrical field. So using Eq. (7), Equations (3)–(6) can be solved explicitly. The following are the results obtained after calculating these above equations.

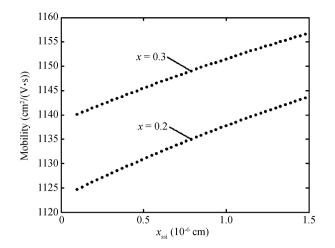

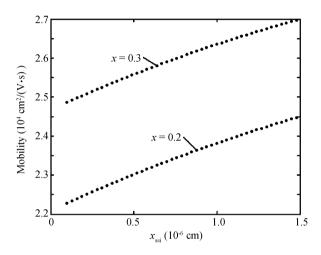

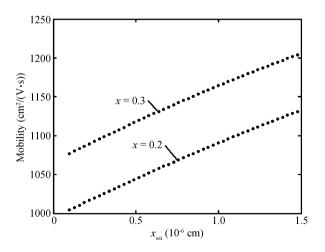

Fig. 4. Modeled results of electron phonon mobility with strained silicon thickness for strained-Si on  $Si_{1-x}Ge_x$  MOSFETs at room temperature with a gate to source voltage of 3 V.

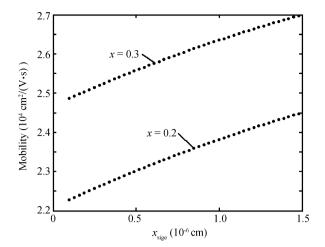

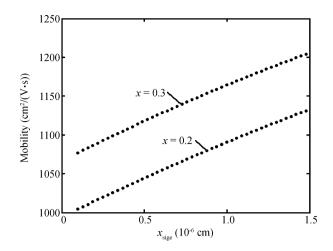

Fig. 5. Modeled results of electron phonon mobility with silicon germanium thickness for strained-Si on  $Si_{1-x}Ge_x$  MOSFETs at room temperature with a gate to source voltage of 3 V.

#### 5. Results and discussion

We have modeled electron mobility for the biaxial strained silicon/SiGe MOSFET for various device parameters. The parameters used in our simulation are given in Table 1. Figure 3 shows the phonon mobility variation with the effective surface electrical field. The influence of strain due to increased germanium content is clearly seen as the mobility increases with the increased germanium content, even at high electrical fields. The results match closely with reported results<sup>[5]</sup>. Figure 4 shows the phonon mobility variation with the strained silicon thickness. The influence of strain due to increased germanium content is clearly seen as the mobility increases with the increased germanium content at high strained silicon thickness. Figure 5 shows the phonon mobility variation with the relaxed silicon germanium layer thickness. The influence of strain due to increased germanium content is clearly seen as the mobility increases with the increased germanium content. The results match closely with reported results<sup>[5]</sup>.

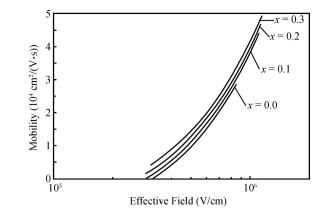

Figure 6 shows the columbic mobility variation with the

Fig. 6. Modeled results of electron coulomb mobility with effective electrical field for strained-Si on  $Si_{1-x}Ge_x$  MOSFETs at room temperature.

Fig. 7. Modeled results of electron coulomb mobility with strained silicon thickness for strained-Si on  $Si_{1-x}Ge_x$  MOSFETs at room temperature with a gate to source voltage of 3 V.

effective surface electrical field. The influence of strain due to increased germanium content is clearly seen as the columbic mobility increases with the increased germanium content, even at high electrical fields. The increase is not so sharp as compared to the phonon mobility increase, showing little impact of the strain on the columbic mobility. Figures 7 and 8 show an increasing trend of columbic mobility with the strained silicon thickness and relaxed silicon germanium thickness, respectively.

Figure 9 shows the surface roughness mobility variation with the effective surface electrical field. The influence of strain due to increased germanium content is clearly seen as the surface roughness mobility increases with the increased germanium content, even at high electrical fields. The increase is not so sharp as compared to the phonon mobility increase, showing little impact of the strain on the surface roughness mobility. Figures 10 and 11 show an increasing trend of columbic mobility with the strained silicon thickness and relaxed silicon germanium thickness, respectively.

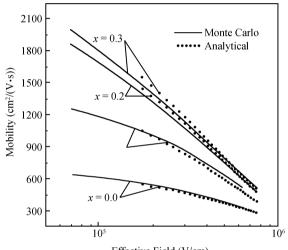

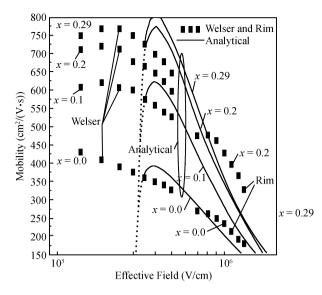

Figure 12 shows the phonon and surface roughness mobility variation with the effective surface electrical field. The influence of strain due to increased germanium content is clearly

Fig. 8. Modeled results of electron coulomb mobility with relaxed silicon germanium thickness for strained-Si on  $Si_{1-x}Ge_x$  MOSFETs at room temperature with a gate to source voltage of 3 V.

Fig. 9. Modeled results of surface roughness electron mobility with effective electrical field for strained-Si on  $Si_{1-x}Ge_x$  MOSFETs at room temperature.

Fig. 10. Modeled results of surface roughness electron mobility with thickness of strained silicon region for strained-Si on  $Si_{1-x}Ge_x$  MOSFETs at room temperature with a gate voltage of 3 V.

seen as the surface roughness mobility increases with the increased germanium content, even at high electrical fields. The

Fig. 11. Modeled results of surface roughness electron mobility with thickness of relaxed silicon germanium region for strained-Si on  $Si_{1-x}Ge_x$  MOSFETs at room temperature with a gate voltage of 3 V.

Effective Field (V/cm)

Fig. 12. Modeled results of electron mobility (accounting for phonon and surface roughness scattering mechanisms) with effective electrical field for strained-Si on  $Si_{1-x}Ge_x$  MOSFETs at room temperature. Reported results are shown by black lines. Data calculated with the model developed in this paper are shown by blue symbols.

results match closely with reported results<sup>[5]</sup>. Figure 13 shows all three mobility variation with the effective surface electrical field. The influence of strain due to increased germanium content is clearly seen as the surface roughness mobility increases with the increased germanium content, even at high electrical fields. The results match closely with reported results<sup>[5]</sup>.

## 6. Conclusion

The semi analytical model developed in this paper shows an increase in electron mobility with the germanium concentration at a given electrical field. The results match closely with the numerical results produced using Monte Carlo simulations reported in literature.

Fig. 13. Modeled results of electron mobility with effective electrical field for strained-Si on  $Si_{1-x}Ge_x$  MOSFETs at room temperature. Data reported by Welser *et al.* and Rim *et al.* in Ref. [5] are shown by squares. Data calculated with the model developed in this paper are shown by lines. The mobility curves vary with the germanium content in the relaxed SiGe buffer layer.

## Acknowledgments

The authors thank the Director, UIET, Panjab University,

Chandigarh, India, for allowing them to carry out this work. The authors would like to thank Panjab University, Chandigarh, India, for providing an excellent research environment to complete this work. The authors would like to thank the Department of information technology, New Delhi, India, for financial assistance for the project on nanoscale and low temperature electronics.

### References

- Schaller R R. Moore's law: past, present and future. IEEE Spectrum, June, 1997: 53

- [2] Moore G E. Cramming more components onto integrated circuits. Proc IEEE, 1998, 86(1): 82

- [3] Rim K, Hoyt J L, Gibbons J F. Fabrication and analysis of deep submicron strained-Si N-MOSFETs. IEEE Trans Electron Devices, 2000, 47(7): 1406

- [4] Maiti C K, Chakrabarti N B, Ray S K. Strained silicon heterostructure field effect transistors. New York: Taylor and Francis, 2007

- [5] Roldán J B, Gámiz F, Cartujo-Cassinello P, et al. Strained-Si on SiGe MOSFET mobility model. IEEE Trans Electron Devices, 2003, 50(5): 1408

- [6] Walczak J, Majkusia B. Electron mobility and drain current in strained-Si MOSFET. Journal of Telecommunications and Information Technology, March, 2007: 84

- [7] Nahfeh H, Hoyt J L, Antoniadis D A. A physically based analytical model for the threshold voltage of strained-Si n-MOSFETs. IEEE Trans Electron Devices, 2004, 51(12): 2069