# Pb(Zr<sub>0.52</sub>Ti<sub>0.48</sub>)O<sub>3</sub> memory capacitor on Si with a polycrystalline silicon/SiO<sub>2</sub> stacked buffer layer\*

Cai Daolin(蔡道林)<sup>1,†</sup>, Li Ping(李平)<sup>2</sup>, Zhai Yahong(翟亚红)<sup>2</sup>, Song Zhitang(宋志棠)<sup>1</sup>, and Chen Houpeng(陈后鹏)<sup>1</sup>

<sup>1</sup>State Key Laboratory of Functional Materials for Informatics, Laboratory of Nanotechnology, Shanghai Institute of Microsystems and Information Technology, Chinese Academy of Sciences, Shanghai 200050, China

<sup>2</sup>State Key Laboratory of Electronic Thin Films and Integrated Devices, University of Electronic Science and Technology of

"State Key Laboratory of Electronic Thin Films and Integrated Devices, University of Electronic Science and Technology of China, Chengdu 610054, China

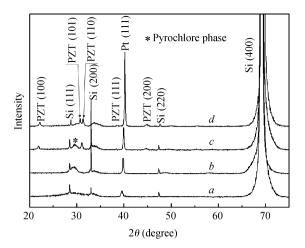

**Abstract:**  $Pb(Zr_{0.52}Ti_{0.48})O_3$  (PZT) thin films have been deposited on a p-type Si substrate separated by a polycrystalline silicon/SiO<sub>2</sub> stacked buffer layer. The X-ray diffraction peaks of the PZT thin films prepared on the polycrystalline silicon annealed at different temperatures were measured. In addition, the polarization of the Pt/PZT/polycrystalline silicon capacitor has been investigated. The memory capacitor of the metal/ferroelectric/polycrystalline silicon/SiO<sub>2</sub>/semiconductor structure annealed at 650 °C exhibits a clockwise capacitance–voltage hysteresis loop due to the ferroelectric polarization of the PZT thin film. The memory window increases with increasing the area coupling ratio between the SiO<sub>2</sub> capacitor and the PZT capacitor.

**Key words:** capacitor; thin film; memory **DOI:** 10.1088/1674-4926/32/9/094007

**PACC:** 7780F

# 1. Introduction

Ferroelectric thin film is a promising material for nonvolatile memory applications<sup>[1,2]</sup>. In particular, the ferroelectric field effect transistor (FFET), as a nonvolatile memory, is promising for the future because FFETs have a single device structure, low power consumption, nonvolatile data storage and nondestructive readout operation characteristics<sup>[3-6]</sup>. FFETs can pave the way for the high-density integration of nonvolatile ferroelectric random access memory (FRAM). However, it is difficult to prepare ferroelectric thin films with good characteristics directly on silicon substrate because of the interface reactions between the ferroelectric thin film and the silicon substrate<sup>[7]</sup>. A ferroelectric FET with a metal/ferroelectric/insulator/silicon (MFIS) structure is proposed in order to avoid interface reactions<sup>[8-10]</sup>. When a metal is additionally inserted between the ferroelectric layer and the insulator layer, a metal/ferroelectric/metal/insulator/silicon (MFMIS) structure can be obtained<sup>[11-13]</sup>.

In our previous work, an FFET structure using a polycrystalline silicon (poly-Si)/SiO<sub>2</sub> stacked layer as a buffer layer has been proposed and the current–voltage characteristics of the FFET with this metal/PZT/poly-Si/SiO<sub>2</sub>/Si (MFPIS) structure have been reported<sup>[14]</sup>. Electrical properties of MFPIS capacitors such as the memory window need to be better understood. So MFPIS structure memory capacitors have been fabricated. In this paper, the crystalline phases of the Pb(Zr<sub>0.52</sub>Ti<sub>0.48</sub>)O<sub>3</sub> (PZT) thin films on polycrystalline silicon annealed at different temperatures are identified. The memory window of the MFPIS capacitors is investigated by the capacitance–voltage (*C*–*V*) method. The memory window as a function of the area coupling ratio between the  $\mathrm{SiO}_2$  capacitor and the PZT capacitor is discussed.

# 2. Experiment

To fabricate the MFPIS capacitors, a p-type Si wafer with (100) orientation was used as the starting substrate. A  $SiO_2$ layer was thermally grown on Si substrate. A poly-Si layer was fabricated by the liquid phase chemical vapor deposition method. Then the phosphorus ions were implanted to dope the poly-Si. PZT thin films were deposited by radio frequency magnetron sputtering at room temperature. The PZT target was  $Pb_{1,1}(Zr_{0.52}Ti_{0.48})O_3$ . The excess of Pb was to compensate for volatile PbO. The PZT thin films were etched by a wet process. The Pt electrode was sputtered and patterned by a liftoff process. Then the PZT thin films were rapidly thermal annealed at 500-650 °C for 40 s in an argon and oxygen mixed gas atmosphere in order to obtain a good crystal orientation. The volume ratio of argon and oxygen in the mixed gas atmosphere was 10 : 3. The thicknesses of Pt, PZT, poly-Si, and SiO<sub>2</sub> were 100, 200, 200 and 20 nm, respectively. The aluminum electrode was sputtered. Post metallization annealing was performed at 250 °C in an N<sub>2</sub> ambient for 30 min.

The crystalline phase of the PZT thin films was identified by X-ray diffraction (XRD). The C-V characteristics were measured with an Agilent 4284A precision LCR meter.

### 3. Results and discussion

Figure 1 shows the XRD patterns of the PZT thin films formed by the process described above. The crystallization behavior of the PZT films was sensitively influenced by the an-

<sup>\*</sup> Project supported by the National Key Foundation of China (No. 51310Z).

<sup>†</sup> Corresponding author. Email: caidl@mail.sim.ac.cn

Received 10 March 2011, revised manuscript received 5 May 2011

Fig. 1. XRD patterns of the PZT thin films on poly-Si/SiO<sub>2</sub>/Si annealed at various temperatures. (*a*) As deposited. (*b*) 500 °C. (*c*) 600 °C. (*d*) 650 °C.

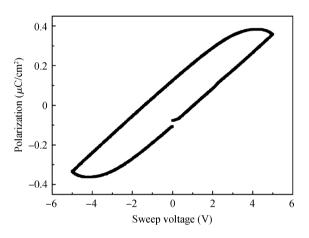

Fig. 2. P-V hysteresis loop of the Pt/PZT/poly-Si capacitor. PZT thin film was annealed at 650 °C.

Figure 2 shows the polarization–voltage (P-V) hysteresis loop of the Pt/PZT/poly-Si capacitor, indicating a non-saturating P-V behavior with a small remnant polarization (~ 0.15  $\mu$ C/cm<sup>2</sup>). This is because that the insufficient crystalline occurs when the PZT thin films are deposited on the poly-Si layer. The small polarization is consistent with the weak peak intensity shown in Fig. 1.

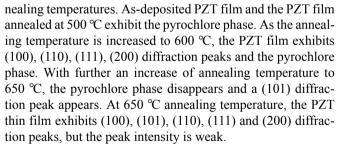

Figure 3 shows the C-V characteristics of the MFPIS memory capacitor. The sweep voltage changed from negative to positive and then back, and the frequency and the voltage of the measuring signal were 1 MHz and 50 mV, respectively. As traced by arrows, the clockwise hysteresis loop is clearly observed, indicating that the memory effect is due to the ferro-

Fig. 3. C-V characteristics of the MFPIS memory capacitor. PZT thin film was annealed at 650 °C.

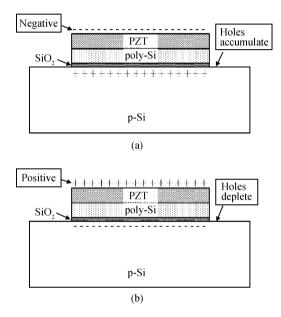

Fig. 4. Schematic diagram of a simplified model for the MFPIS memory capacitor under different bias conditions. Si surface is (a) in accumulation and (b) in inversion.

electric polarization of the PZT thin film.

When a negative voltage is applied to the top electrode of the MFPIS capacitor, the PZT layer becomes polarized and the holes will accumulate at the silicon surface due to the polarization of the PZT layer, as shown in Fig. 4(a). When the sweep voltage sweeps from negative to positive voltage, an additional positive voltage is needed to convert the silicon surface from accumulation to inversion. Thus, the C-V curve is shifted toward the right.

When a positive voltage is applied to the top electrode of the capacitor, the PZT layer becomes polarized. As shown in Fig. 4(b), the holes will be depleted and an extra number electron will be induced to inversion at the silicon surface. When the sweep voltage sweeps from positive to negative voltage, an additional negative voltage is needed to convert the silicon surface from inversion to accumulation. Thus, the C-Vcurve is shifted toward the left. Hence, there will be a clockwise C-V hysteresis window. This is due to the polarization effect

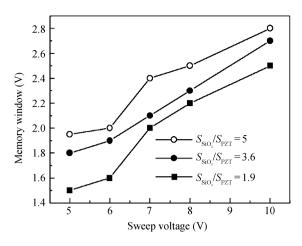

Fig. 5. Memory windows of the MFPIS memory capacitors with different coupling ratios. PZT thin film was annealed at 650 °C.

of the PZT thin film. The shifted direction is consistent with the counterclockwise current–voltage loops of the MFPIS FFET in our previous work<sup>[14]</sup>.

The memory window is an important memory parameter. The memory window is defined as the voltage shift when the sweep voltage is swept from accumulation to inversion and back<sup>[15]</sup>. The memory window as a function of the sweep voltage derived from the C-V curves has been measured. Figure 5 shows the memory windows measured from the C-V characteristics of the MFPIS memory capacitors with the sweep voltage range of 5-10 V. The MFPIS memory capacitors exhibit the progressively increasing C-V memory window with increasing the sweep voltage because the ferroelectric polarization increases as the sweep voltage increases. The memory windows with different area coupling ratios between the SiO<sub>2</sub> capacitor and the PZT capacitor are shown in Fig. 5. The memory window increases with increasing the coupling ratio. In order to further explain this, the electrical field on PZT ( $E_{PZT}$ ) has been calculated by the following equations [2, 14, 16]:

$$E_{\rm PZT} = V_{\rm g} / \left( d_{\rm PZT} + \frac{\varepsilon_{\rm PZT} S_{\rm PZT}}{\varepsilon_{\rm SiO_2} S_{\rm SiO_2}} d_{\rm SiO_2} \right), \tag{1}$$

where  $d_{PZT}$  and  $d_{SiO_2}$  are the thicknesses of PZT and SiO<sub>2</sub> respectively.  $S_{PZT}$  and  $S_{SiO_2}$  are the areas of PZT and SiO<sub>2</sub> corresponding to the areas of the ferroelectric capacitor and the metal–oxide–semiconductor capacitor, respectively. It is noted that  $E_{PZT}$  increases with increasing the coupling ratio. So the memory window increases with increasing the coupling ratio. In our case,  $d_{PZT} = 200$  nm, and  $d_{SiO_2} = 20$  nm, even  $S_{SiO_2}/S_{PZT} = 1.9$ . Considering the dielectric constants of PZT ( $\varepsilon_{PZT} = 500$ )<sup>[2]</sup> and SiO<sub>2</sub> ( $\varepsilon_{SiO_2} = 3.9$ )<sup>[17]</sup>, we get  $E_{PZT}$  as 32.3 kV/cm at 5 V sweep voltage, which is sufficient for ferroelectric domain switching to occur in PZT<sup>[16]</sup>.

In fact, the polarization of 0.15  $\mu$ C/cm<sup>2</sup> shown in Fig. 2 is large enough to swing the silicon surface potential from depletion to inversion. This is also consistent with the theoretical prediction<sup>[18]</sup> which suggests that the remnant polarization, once it exceeds certain minimal value (e.g., of order 0.1  $\mu$ C/cm<sup>2</sup>), has a minor impact on the memory window. The device performance could be improved by further optimizing the thicknesses and areas of PZT and SiO<sub>2</sub>.

#### 4. Conclusion

In conclusion, a metal/PZT/poly-Si/SiO<sub>2</sub>/Si structure memory capacitor has been fabricated by depositing a PZT ferroelectric layer on a poly-Si/SiO<sub>2</sub> stacked buffer layer by radio frequency magnetron sputtering. A remnant polarization that is enough to swing the silicon surface is obtained from the Pt/PZT/poly-Si capacitor. The clockwise hysteresis loop in the C-V characteristics demonstrates that this MFPIS structure capacitor can realize a memory function due to the ferroelectric polarization of the PZT thin film. This is consistent with the counterclockwise current–voltage loops of the MFPIS FFET. The memory window increases with increasing the area coupling ratios between the capacitor of SiO<sub>2</sub> and PZT.

# References

- Kim Y T, Shin D S. Memory window of Pt/ SrBi<sub>2</sub>-Ta<sub>2</sub>O<sub>9</sub>/CeO<sub>2</sub>/SiO<sub>2</sub>/Si structure for metal ferroelectric insulator semiconductor field effect transistor. Appl Phys Lett, 1997, 71(24): 3507

- [2] Chang C Y, Juan T P, Lee J Y. Fabrication and characterization of metal-ferroelectric (PbZr<sub>0.53</sub>Ti<sub>0.47</sub>O<sub>3</sub>)-insulator(Dy<sub>2</sub>O<sub>3</sub>)semiconductor capacitors for nonvolatile memory applications. Appl Phys Lett, 2006, 88: 072917

- [3] Sun C L, Chen S Y, Liao C C, et al. Low voltage lead titanate/Si one-transistor ferroelectric memory with good device characteristics. Appl Phys Lett, 2004, 85: 4726

- [4] Li T K, Hsu S T, Ulrich B D, et al. The thermal stability of onetransistor ferroelectric memory with Pt–Pb<sub>5</sub>Ge<sub>3</sub>O<sub>11</sub>–Ir–poly-SiO<sub>2</sub>–Si gate stack. IEEE Trans Electron Devices, 2003, 50(11): 2280

- [5] Aizawa K, Park B E, Kawashima Y, et al. Impact of HfO<sub>2</sub> buffer layers on data retention characteristics of ferroelectric-gate fieldeffect transistors. Appl Phys Lett, 2004, 85: 3199

- [6] Scott J F. Applications of modern ferroelectrics. Science, 2007, 315: 954

- [7] Liu C H, Wu J M, Wu L J. Characteristics of metalferroelectric-insulator-silicon structures with ferroelectric (Pb<sub>0.8</sub>Ba<sub>0.2</sub>)ZrO<sub>3</sub> thin films and (Ba<sub>0.5</sub>Sr<sub>0.5</sub>)TiO<sub>3</sub> buffer layer. Appl Phys Lett, 2006, 88: 122901

- [8] Tokumitsu E, Nakamura R I, Ishiwara H. Nonvolatile memory operations of metal-ferroelectric-insulator-semiconductor (MFIS) FETs using PLZT/STO/Si(100) structures. IEEE Electron Device Lett, 1997, 18(4): 160

- [9] Hirai T, Fujisaki Y, Nagashima K, et al. Preparation of SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub> film at low temperatures and fabrication of a metal/ferroelectric/insulator/semiconductor field effect transistor using Al/SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>/CeO<sub>2</sub>/Si(100) structures. Jpn J Appl Phys, Part 1, 1997, 36(9B): 5908

- [10] Lee S K, Kim Y T, Kim S L, et al. Effects of coercive voltage and charge injection on memory windows of metal-ferroelectric-semiconductor and metalferroelectric-insulator-semiconductor gate structures. J Appl Phys, 2002, 91(11): 9303

- [11] Nakao Y, Nakamura T, Kamisawa A, et al. Study on ferroelectric thin films for application to NDRO nonvolatile memories. Integr Ferroelectr, 1995, 6(34): 5202

- [12] Kawasaki T, Akiyama Y, Fujita S, et al. MFMIS structure for nonvolatile ferroelectric memory using PZT thin film. IEICE Trans Electron, 1998, E81-C(4): 584

- [13] Tokumitsu E, Fujii G, Ishiwara H. Nonvolatile ferroelectric-gate field-effect transistors using SrBi<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>/Pt/SrTa<sub>2</sub>O<sub>6</sub>/SiON/Si

structures. Appl Phys Lett, 1999, 75(4): 575

- [14] Cai D L, Li P, Zhang S R, et al. Fabrication and characteristics of a metal/ferroelectric/polycrystalline silicon/insulator/silicon field effect transistor. Appl Phys Lett, 2007, 90: 153513

- [15] Jun T P, Chang C Y, Lee Y M. A new metalferroelectric(PbZr<sub>0.53</sub>Ti<sub>0.47</sub>O<sub>3</sub>) – insulator(Dy<sub>2</sub>O<sub>3</sub>) – semiconductor (MFIS) FET for nonvolatile memory applications. IEEE Electron Device Lett, 2006, 27(4): 217

- [16] Kang Y S, Xiao Q, Alivov Y I, et al. Fabrication and current-voltage characterization of a ferroelectric lead zirconate ti-

tanate/AlGaN/GaN field effect transistor. Appl Phys Lett, 2006, 88: 123508

- [17] Lim S H, Rastogi A C, Desu S B. Electrical properties of metal– ferroelectric–insulator–semiconductor structures based on ferroelectric polyvinylidene fluoride copolymer film gate for nonvolatile random access memory application. J Appl Phys, 2004, 96(10): 5673

- [18] Miller S L, McWhorter P J. Physics of the ferroelectric nonvolatile memory field effect transistor. J Appl Phys, 1992, 72(12): 5999