# Continuous analytic I-V model for GS DG MOSFETs including hot-carrier degradation effects

Toufik Bentrcia<sup>1</sup>, Faycal Djeffal<sup>2,†</sup>, and Abdel Hamid Benhaya<sup>2</sup>

<sup>1</sup>Department of Physics, University of Batna, Batna 05000, Algeria <sup>2</sup>LEA, Department of Electronics, University of Batna, Batna 05000, Algeria

Abstract: We have studied the influence of hot-carrier degradation effects on the drain current of a gate-stack double-gate (GS DG) MOSFET device. Our analysis is carried out by using an accurate continuous current–voltage (I-V) model, derived based on both Poisson's and continuity equations without the need of charge-sheet approximation. The developed model offers the possibility to describe the entire range of different regions (subthreshold, linear and saturation) through a unique continuous expression. Therefore, the proposed approach can bring considerable enhancement at the level of multi-gate compact modeling including hot-carrier degradation effects.

Key words: GS DG MOSFET; hot-carriers degradation effects; compact modeling; piece-wise models **DOI:** 10.1088/1674-4926/33/1/014001 **EEACC:** 2570

## 1. Introduction

Double-gate MOSFET architectures have been recognized as a leading candidate to extend the scaling limit of conventional bulk MOSFETs to 25 nm gate length and beyond due to their significant reduction of the short channel effects, which prevail in bulk MOSFETs<sup>[1]</sup>. The use of undoped Si films for DG MOSFETs avoids the problems resulting from dopantimpurity location randomness and improves carrier transport by the resulting mobility enhancement, so the idea of an undoped body is expected to become widespread in the coming years as miniaturization advances<sup>[2]</sup>. Several analytic potential and drain current models for undoped symmetric double gate MOSFETs have been derived by solving Poisson's and current continuity equations with the gradual channel approximation. The obtained expressions are able to take account of the volume inversion effects, which is not the case for charge-sheet approximation based models<sup>[3]</sup>.

However, as device feature size shrinks down to deep submicron region, in order to get better device performance and higher package density, the characteristics degrade because of the hot-carrier effect<sup>[4]</sup>. For a deep submicron device, hotcarrier induced degradation becomes a major reliability concern and affects the optimal function. The main cause of the hot-carrier degradation effect in multi-gate devices is already discussed in many literature reviews<sup>[5,6]</sup>. Recent works discussing the elaboration of new closed analytical models have been proposed to study DG MOSFET structures including the interfacial hot-carrier effects. This is achieved in order to investigate the scaling limits of these devices when defects generated by the injected carriers near the drain side are present. However, explored studies have shown two basic drawbacks: firstly, the majorities of these works are limited to the subthreshold regime and cannot be used to study device behavior in the linear or saturation regimes<sup>[7]</sup> and, secondly, the models employed are based on the charge-sheet approximation and some physics phenomena are missed<sup>[8]</sup>. Therefore, a profound

analysis of the interfacial hot-carrier effects on the drain current is a mandatory requirement in order to facilitate the design of future CMOS integrated circuits.

In this paper, we propose a new continuous analytical model to study the performances of the GS DG MOSFET including hot-carrier degradation effects, based on closed-form solutions of Poisson's and current continuity equations. The possibility of developing an extended formulation for the GS DG MOSFET with an interfacial trap density is carried out in the rest of this paper and the model has three distinctive features.

(1) The device channel is assumed to be undoped (lightly doped) instead of the usual high channel doping density. Such absence of dopant atoms in the channel further reduces the mobility degradation by eliminating impurity scattering and avoiding random microscopic dopant fluctuations.

(2) The analytic drain current model covers all three regions of MOSFET operations, subthreshold, linear and saturation, thus maintaining strong continuity between different regions without the need for adjustable parameters, which are in general meaningless physically.

(3) The compact model for a GS DG MOSFET including the hot-carrier degradation effect is derived based on the Pao-Sah integral without the charge-sheet approximation, so that the volume inversion phenomenon in the subthreshold region can be properly predicted.

Our proposed long-channel model is ideally suitable for being the kernel of a GS DG MOSFET including a hot-carrier effects compact formulation. In addition, it can be used as a passage between analytical compact modeling and circuit simulators such as SPICE, Cadence and Anacad's Eldo in order to analyze the electrical circuit performance degradation due to age-related phenomena. For a complete compact model, this long-channel core would need to be enhanced with additional physical effects, such as short-channel and quantum mechanical effects.

<sup>†</sup> Corresponding author. Email: faycaldzdz@hotmail.com

Received 11 July 2011, revised manuscript received 5 September 2011

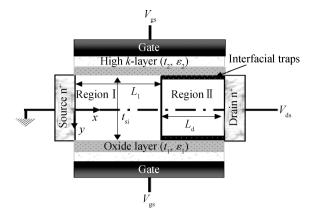

Fig. 1. Schematic diagram of a GS DG MOSFET with an interfacial trap density near the drain side.

#### 2. Modeling approach

We consider a symmetric GS DG undoped n-channel MOSFET, as illustrated in Fig. 1.

We also consider a channel long enough so that the device electrostatics are described by 1-D Poisson's equation in the direction vertical to the channel. Neglecting the hole density, Poisson's equation in the silicon film is given by,

$$\frac{\mathrm{d}^2\psi(x)}{\mathrm{d}x^2} = \frac{\mathrm{d}^2\left(\psi(x) - V\right)}{\mathrm{d}x^2} = \frac{q n_\mathrm{i}}{\varepsilon_\mathrm{si}} \mathrm{e}^{q\left(\frac{\psi(x) - V}{kT}\right)}, \quad (1)$$

where q is the electronic charge,  $n_i$  the intrinsic carrier concentration,  $\varepsilon_{si}$  the permittivity of silicon,  $\psi(x)$  the silicon band bending, and V the electron quasi-Fermi potential.

Despite that the drift–diffusion mechanism has been widely considered as the cornerstone modeling tool for various long channel devices, it is worthwhile employing more elaborated schema such as ballistic transport equations especially when dealing with the nanoscale case, where the mean free path of the carriers is bigger than that of the silicon film width<sup>[9]</sup>.

Since the current mainly flows along the y-direction, we assume that V is constant along the x-direction; i.e., V = V(y). This is the so called gradual channel approximation. Equation (1) can then be integrated twice to yield the solution<sup>[10]</sup>,

$$\psi(x) = V - \frac{2kT}{q} \ln\left(\frac{t_{\rm si}}{2\beta} \sqrt{\frac{q^2 n_{\rm i}}{2\varepsilon_{\rm si}kT}} \cos\frac{2\beta x}{t_{\rm si}}\right).$$

(2)

The constant  $\beta$  is related to  $\psi$  through the boundary condition deduced from Gauss's law,

$$\varepsilon_{\rm ox} \frac{V_{\rm gs} - \Delta \phi - \psi \left( x = \pm \frac{t_{\rm si}}{2} \right)}{t_{\rm oxeff}} = \pm \varepsilon_{\rm si} \left. \frac{\mathrm{d}\psi(x)}{\mathrm{d}x} \right|_{x = \pm \frac{t_{\rm si}}{2}}.$$

(3)

Here  $\varepsilon_{ox}$  is the permittivity of oxide,  $V_{gs}$  is the voltage applied to both gates,  $t_{si}$  and  $t_{oxeff}$  are the silicon and the effective oxide thicknesses, and  $\Delta \phi$  is the work function of both the top and bottom gate electrodes with respect to the intrinsic silicon.

The effective oxide layer thickness of insulator layer  $t_{\text{oxeff}}$  is given by the superposition of the thickness of the SiO<sub>2</sub> layer and the thickness of the high-*k* layer as follows<sup>[11]</sup>,

$$t_{\text{oxeff}} = t_1 + \frac{\varepsilon_1}{\varepsilon_2} t_2. \tag{4}$$

By substituting Eq. (2) into Eq. (3), we get a nonlinear equation relating  $\beta$  explicitly to different basic parameters,

$$\frac{2\varepsilon_{\rm si}t_{\rm oxeff}}{\varepsilon_{\rm ox}t_{\rm si}}\beta\tan\beta - \ln\left(\cos\beta\right) + \ln\beta = \frac{q\left(V_{\rm gs} - \Delta\phi - V\right)}{2kT} - \ln\left(\frac{2}{t_{\rm si}}\sqrt{\frac{2\varepsilon_{\rm si}kT}{q^2n_{\rm i}}}\right).$$

(5)

The hot-carrier-induced oxide-interface charge has a significant influence on two device properties: (1) it affects the local electric potential in the adjacent drain region; and (2) it changes the local channel electron mobility. The potential effect can be accounted for as an additional term in the total mobile charge per unit gate area  $Q_{inv}$  in the damaged region. By using Eq. (2) combined with  $\frac{Q_{inv}}{\varepsilon_{si}} = 2 \left. \frac{d\psi(x)}{dx} \right|_{x=\frac{t_{si}}{2}}$ , required quantity  $Q_{inv}$  expressed in terms of  $\beta$  yields for each region,

$$Q_{\rm inv}(\beta) = \begin{cases} \frac{8\varepsilon_{\rm si}}{t_{\rm si}} \frac{kT}{q} \beta \tan \beta, & 0 \le y \le L_1, \\ \frac{8\varepsilon_{\rm si}}{t_{\rm si}} \frac{kT}{q} \beta \tan \beta - 2qN_{\rm f}, & L_1 \le y \le L. \end{cases}$$

(6)

The reduction of channel electron mobility can be represented by Mathiessen's rule, as proposed by Nishida and Sah<sup>[12]</sup>. This approach assumes that the total reciprocal mobility is composed of bulk mobility  $\mu_0$  and oxide interface charge scattering mobility  $\mu_{ox}$  as follows,

$$\mu_{i=1,2} = \begin{cases} \mu_0, & 0 \le y \le L_1, \\ \frac{\mu_0 \mu_{\text{ox}}}{\mu_0 + \mu_{\text{ox}}}, & L_1 \le y \le L, \end{cases}$$

(7)

where the electron mobility caused by the charge scattering is given by,

$$\mu_{\rm ox} = 1000 \times \frac{3 \times 10^{11} T}{80 N_{\rm f}}.$$

(8)

For a given  $V_{gs}$ ,  $\beta$  can be solved from Eq. (5) as a function of V. Note that V varies from the source to the drain, the functional dependence of V(y) and  $\beta(y)$  is determined by the current continuity equation, which requires the current  $I_{ds}$  given by  $I_{ds} = \mu W Q_{inv} dV/dy$  to be constant, independent of V or y. The parameter  $\mu$  is the effective mobility, and W is the device width. Note that  $dV/d\beta$  can also be expressed as a function of  $\beta$  by differentiating Eq. (5) to get,

$$\frac{\mathrm{d}V}{\mathrm{d}\beta} = -\frac{2kT}{q} \left[ \frac{1}{\beta} + \tan\beta + 2\frac{\varepsilon_{\mathrm{si}}t_{\mathrm{oxeff}}}{\varepsilon_{\mathrm{ox}}t_{\mathrm{s}}i} \frac{\mathrm{d}}{\mathrm{d}\beta} \left(\beta \tan\beta\right) \right].$$

(9)

The solution of Pao–Sah's integral can be found in two adjacent channel regions by integrating both sides of the continuity equation from the source to the boundary of the damaged

| Table 1. Asymptotic values and dominance rules for different regions of operation. |                            |                                   |              |              |                                        |                                        |

|------------------------------------------------------------------------------------|----------------------------|-----------------------------------|--------------|--------------|----------------------------------------|----------------------------------------|

| Regime                                                                             | $f_{\rm r}(\beta_{\rm s})$ | $f_{\rm r}(\beta_{\rm p})$        | $\beta_{s}$  | $eta_{ m p}$ | $g_{\rm r}(\beta_{\rm s})$             | $g_{\rm r}(\beta_{\rm p})$             |

| Subthreshold                                                                       | $\ll -1$                   | $\ll -1$                          | $\ll 1$      | ≪ 1          | —                                      | —                                      |

|                                                                                    | $\ln \beta_s$              | $\ln \beta_{\rm p}$               | —            |              | ${\beta_s}^2/2$                        | $\beta_{\rm p}^2/2$                    |

| Linear                                                                             | $\gg 1$                    | $\gg 1$                           | $\sim \pi/2$ | $\sim \pi/2$ | —                                      | —                                      |

|                                                                                    | $\beta_{s} tan \beta_{s}$  | $\beta_{\rm p} tan \beta_{\rm p}$ | —            | —            | $(\beta_{\rm s} \tan \beta_{\rm s})^2$ | $(\beta_{\rm p} \tan \beta_{\rm p})^2$ |

| Saturation                                                                         | $\gg 1$                    | $\ll -1$                          | $\sim \pi/2$ | $\ll 1$      |                                        |                                        |

|                                                                                    | $\beta_{s} tan \beta_{s}$  | $\ln eta_{ m p}$                  |              |              | $(\beta_{\rm s} \tan \beta_{\rm s})^2$ | $\beta_{\rm p}^2/2$                    |

Table 1. Asymptotic values and dominance rules for different regions of operation.

region  $L_1$  then from the boundary to the drain<sup>[13]</sup> and valid expressions of the drain current in these regions are carried out as follows: for the fresh region we have,

$$I_{\rm ds} = \mu_1 \frac{W}{L_1} \int_0^{V_{\rm p}} \mathcal{Q}_{\rm inv}(V) \mathrm{d}V = \mu_1 \frac{W}{L_1} \int_{\beta_{\rm s}}^{\beta_{\rm p}} \mathcal{Q}_{\rm inv}(\beta) \frac{\mathrm{d}V}{\mathrm{d}\beta} \mathrm{d}\beta.$$

(10)

Substituting different factors in Eq. (10) and carrying out the integration analytically,

$$I_{\rm ds} = \mu_1 \frac{4W\varepsilon_{\rm si}}{t_{\rm si}L_1} \left(\frac{2kT}{q}\right)^2 \times \left[\beta \tan\beta - \frac{\beta^2}{2} + \frac{\varepsilon_{\rm si}t_{\rm oxeff}}{\varepsilon_{\rm ox}t_{\rm s}i} \left(\beta \tan\beta\right)^2\right]_{\beta_{\rm p}}^{\beta_{\rm s}},$$

(11)

and for the damaged region,

$$I_{\rm ds} = \mu_2 \frac{W}{L_{\rm d}} \int_{V_{\rm p}}^{V_{\rm ds}} Q_{\rm inv}(V) \mathrm{d}V = \mu_2 \frac{W}{L_{\rm d}} \int_{\beta_{\rm p}}^{\beta_{\rm d}} Q_{\rm inv}(\beta) \frac{\mathrm{d}V}{\mathrm{d}\beta} \mathrm{d}\beta.$$

(12)

Substituting appropriate parameters as previously then carrying out the integration analytically yields,

$$I_{\rm ds} = \mu_2 \frac{4W\varepsilon_{\rm si}}{t_{\rm si}L_{\rm d}} \left(\frac{2kT}{q}\right)^2 \\ \times \left[\beta \tan\beta - \frac{\beta^2}{2} + \frac{\varepsilon_{\rm si}t_{\rm oxeff}}{\varepsilon_{\rm ox}t_{\rm si}} \left(\beta \tan\beta\right)^2\right]_{\beta_{\rm d}}^{\beta_{\rm p}} \\ - \mu_2 \frac{4WN_{\rm f}kT}{L_{\rm d}} \left[\ln\frac{\beta}{\cos\beta} + \frac{2\varepsilon_{\rm si}t_{\rm oxeff}}{\varepsilon_{\rm ox}t_{\rm s}i} \left(\beta \tan\beta\right)\right]_{\beta_{\rm d}}^{\beta_{\rm p}}.$$

(13)

As is clear from the obtained expressions of drain current in both considered regions, the channel length modulation effect is ignored, which can be explained by the fact that our framework is based on a long channel model. In order to take into account such phenomenon for scaled devices, we have to introduce a new effective length and some fitting parameters<sup>[14]</sup>.

To compute the drain current we define the following two functions representing the right-hand side of Eqs. (5) and (11),

$$f_{\rm r}(\beta) = 2r\beta \tan\beta - \ln(\cos\beta) + \ln\beta, \qquad (14)$$

$$g_{\rm r}(\beta) = \beta \tan \beta - \frac{\beta^2}{2} + r \left(\beta \tan \beta\right)^2.$$

(15)

Note that the range of  $\beta$  is  $0 < \beta < \pi/2$  and r is a structural parameter defined as  $r = \varepsilon_{si} t_{ox} / \varepsilon_{ox} t_{si}$  For given  $V_{gs}$  and  $V_{ds}$ ,  $\beta_s$  and  $\beta_d$  are calculated from the conditions,

$$f_{\rm r}(\beta_{\rm s}) = (q/2kT) \left( V_{\rm gs} - V_0 \right),$$

(16)

$$f_{\rm r}(\beta_{\rm d}) = (q/2kT) \left( V_{\rm gs} - V_0 - V_{\rm ds} \right), \tag{17}$$

where

$$V_0 = \Delta \phi + \frac{2kT}{q} \ln \left( \frac{2}{t_{\rm si}} \sqrt{\frac{2\varepsilon_{\rm si}kT}{q^2 n_{\rm i}}} \right).$$

At this level,  $\beta_p$  can be also obtained numerically by equating drain current expressions of both damaged and fresh regions.

In the limit case of a fresh device, all parameters correspond to those of the fresh region, hence  $\beta_p \rightarrow \beta_d$ , and as a result, our compact model reduces to the drain current model established in Ref. [15],

$$I_{\rm ds} = \mu_1 \frac{4W\varepsilon_{\rm si}}{t_{\rm si}L} \left(\frac{2kT}{q}\right)^2 \\ \times \left[\beta \tan\beta - \frac{\beta^2}{2} + \frac{\varepsilon_{\rm si}t_{\rm oxeff}}{\varepsilon_{\rm ox}t_{\rm si}} (\beta \tan\beta)^2\right]_{\beta_{\rm d}}^{\beta_{\rm s}}.$$

(18)

Here we have in hand all the ingredients required for the elaboration of the drain current model taking account of the hot-carrier degradation effects. Then we can write,

$$I_{\rm ds} \propto \left[ g_{\rm r}(\beta_{\rm s}) - g_{\rm r}(\beta_{\rm p}) \right]. \tag{19}$$

The asymptotic values and dominance rules characterizing different operation modes in the case of a fresh double gate device have been presented in Ref. [16] and extended later to the surrounding gate device<sup>[17]</sup>. Based on the same formalism, some useful expressions, needed for the piece-wise models deduction, are elaborated for the case of GS DG MOSFET including the hot-carrier degradation effect, as summarized in Table 1. It should be noted that without loss of generality, only the fresh region of the device is considered and the interfacial traps density effect is introduced through the intermediate parameter  $\beta_p$  and the reduced mobility in the damaged region  $\mu_2$ .

## 3. Piece-wise model deduction

In the following, the GS DG MOSFET including hotcarrier effect regions of operation are derived from this continuous analytical model based on approximations given in Table 1.

(1) Subthreshold region<sup>[18]</sup>:

$I_{ds1}$

I

$$_{\rm ds} = I_{\rm ds1} + I_{\rm ds2},\tag{20}$$

with

$$= \mu_1 \frac{W t_{\rm si} n_{\rm i} kT}{L_1} e^{\frac{q(V_{\rm gs} - \Delta\phi)}{kT}} \left(1 - e^{-\frac{qV_{\rm p}}{kT}}\right)$$

and

$$I_{\rm ds2} = \mu_2 \frac{W t_{\rm si} n_{\rm i} k T}{L_{\rm d}} e^{\frac{q(V_{\rm gs} - \Delta\phi)}{kT}} \left(1 - e^{-\frac{q(V_{\rm ds} - V_{\rm p})}{kT}}\right),$$

are the subthreshold currents associated with the fresh and damaged regions in a similar way to the methodology proposed for 4-T and 3-T DG MOSFET based on the basic diffusion current<sup>[19]</sup>,

$$J_{\rm n}(y) = q D_{\rm n} \frac{n_{\rm min}(y)}{L} \left(1 - {\rm e}^{\frac{V_{\rm ds}}{V_{\rm t}}}\right), \qquad (21)$$

where  $D_n$  denotes the diffusion constant, and  $n_{\min}(y)$  is the minimum carriers concentration at a fixed location along the channel. The subthreshold current is proportional to the cross sectional area of the device, but independent of  $t_{\text{oeffx}}$ , which is a manifestation of "volume inversion" that cannot be reproduced by standard charge-sheet-based I-V models.

(2) Linear region above threshold<sup>[20]</sup>:

$$I_{\rm ds} = 2\mu_1 C_{\rm ox} \frac{W}{L_1} \left( V_{\rm gs} - V_{\rm th} - \frac{V_{\rm p}}{2} \right) V_{\rm p}, \qquad (22)$$

where  $V_{\text{th}}$  is the threshold voltage, and  $C_{\text{ox}}$  is the oxide capacitance.

(3) Saturation region:

$$I_{\rm ds} = \mu_1 C_{\rm ox} \frac{W}{L_1} \\ \times \left[ \left( V_{\rm gs} - V_{\rm th} \right)^2 - 2r \left( \frac{2kT}{q} \right)^2 e^{\frac{q(V_{\rm gs} - V_0 - V_{\rm p})}{kT}} \right],$$

(23)

where the saturation current depends on  $(V_{\rm gs} - V_{\rm th})^2$ , as expected for a MOSFET. The saturation current approaches the saturation value with a difference term exponentially decreasing with  $V_{\rm p}$ , in contrast to common piecewise models in which the current is made to be constant in saturation<sup>[21]</sup>.

Since all precedent expressions of the drain current depend on the voltage at the boundary of both regions  $V_p$  rather than the parameters  $\beta_p$ , an implicit formula for  $V_p$  can be obtained from the boundary condition (5),

$$V_{\rm p} = V_{\rm gs} - \Delta \phi - \frac{2kT}{q} \times \left[ \ln\left(\frac{2}{t_{\rm si}}\sqrt{\frac{2\varepsilon_{\rm si}kT}{q^2n_{\rm i}}}\right) + 2r\beta_{\rm p}\tan\beta_{\rm p} - \ln\frac{\cos\beta_{\rm p}}{\beta_{\rm p}} \right].$$

(24)

## 4. Results and discussion

Values of the parameters used for the validation of our proposed model are summarized in Table 2. The range of some geometrical parameters is fixed according to our initial long channel device assumption, so that many alterations of the model regarding the scaling effects can be neglected. Table 2. Values of parameters used in the simulation.

| Parameter       | Value                                      |  |  |

|-----------------|--------------------------------------------|--|--|

| Т               | 300 K                                      |  |  |

| L               | $2 \times 10^{-5}$ cm                      |  |  |

| $L_1$           | 2L/3 cm                                    |  |  |

| $N_{\rm f}$     | $1 \times 10^{12} \text{ cm}^{-2}$         |  |  |

| W               | $3 \times 10^{-6}$ cm                      |  |  |

| t <sub>si</sub> | $2 \times 10^{-6}$ cm                      |  |  |

| $t_1$           | $1 \times 10^{-7} \text{ cm}$              |  |  |

| $\varepsilon_1$ | 3.9                                        |  |  |

| $t_2$           | $1.5 \times 10^{-7} \text{ cm}$            |  |  |

| £2              | 10                                         |  |  |

| ni              | $1.45 \times 10^{10} \text{ cm}^{-3}$      |  |  |

| $\mu_{0}$       | $800 \text{ cm}^2/(\text{V}\cdot\text{s})$ |  |  |

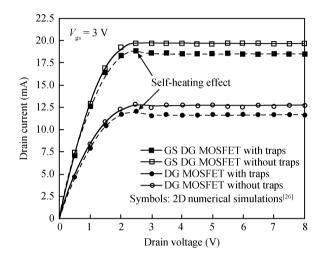

Fig. 2.  $I_{ds}$ - $V_{ds}$  characteristics for DG and GS DG MOSFETs with and without traps.

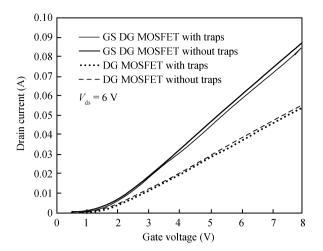

Figures 2 and 3 show the I-V characteristics of DG and GS DG MOSFETs with and without hot-carrier stress. It can be seen that the GS DG device has higher current as compared with the DG device.

As shown in Fig. 2, a decrease of drain current above the linear regime in the case of damaged devices has been observed and this phenomenon can be explained by the channel selfheating effect caused by the presence of an interfacial charge density at the boundary contributing to the increase of coulomb scattering of electrons, which in turn leads to a decrease in the amount of heat flux passing through the interface. Such a process affects the whole thermal behavior of the device over long term work periods. In fact, other constraints can aggressively make the situation worse, such as the introduction of materials with instable thermal conductivity or the significant increase in the phonon boundary scattering generated by thin semiconductor films<sup>[22]</sup>. Since the thermal resistance  $R_{\rm th}$  constitutes a mandatory factor in the self-heating effect, it is possible to extract from the static output characteristics such parameters and the device temperature rise as a function of temperature with the help of some additional data<sup>[23]</sup>. It should be noted that our model including the law of mobility degradation is equivalent in a simplified manner to the introduction of some thermal effects in the whole approach.

It is also clear that a reduction in the drain current can be

Fig. 3.  $I_{ds}-V_{gs}$  characteristics for DG and GS DG MOSFETs with and without traps.

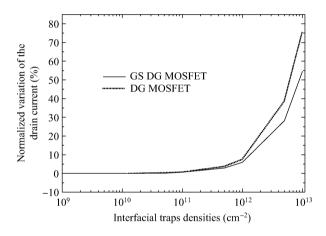

Fig. 4. Variation of the normalized drain current of the DG MOSFET as function of interfacial traps densities for both cases: with and without high-k layer ( $V_{gs} = 3 \text{ V}$ ,  $V_{ds} = 4 \text{ V}$ ).

observed in the case of damaged devices (Figs. 2 and 3) and this reduction can be explained by the effect of the trapped electrons in the damaged region on the drain current density. Moreover, the drain current degradation becomes more apparent when the gate voltage is increased to higher values. The GS DG MOS-FET brings prominent advantages in terms of derived drain current and immunity against the hot-carrier degradation effect compared with conventional DG MOSFETs, which clearly implies that the GS DG design leads to a reduction in hot-carrier effects and impact ionization and, therefore, the hot-carrier reliability is considerably improved.

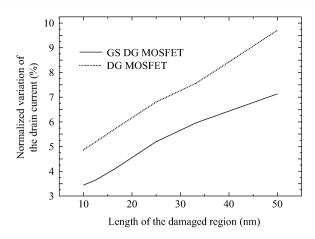

The comparison of both structures' performance in terms of immunity against the hot-carrier degradation can be illustrated by determining the normalized variation of the drain current, which constitutes a pertinent parameter for the characterization of such ageing phenomenon<sup>[24]</sup>.

The degradation of conventional and GS DG MOSFETs as function of charge density and length of the damaged region is illustrated in Figs. 4 and 5.

As shown in Fig. 4 for several different levels of interfacial trap densities, it can be seen that the increase of charge density leads to an increase of the normalized variation of the

Fig. 5. Variation of the normalized drain current of the DG MOSFET as a function of the damaged region length for both cases: with and without high-*k* layer ( $V_{gs} = 3 \text{ V}$ ,  $V_{ds} = 4 \text{ V}$ ).

drain current in both cases. However, the drain current degradation is slower for the GS DG MOSFET structure compared with the conventional one, which confirms well our assumption regarding the immunity of the device. Based on the same parameter, the variation with the length of the damaged region follows also an increasing behavior where the GS DG MOS-FET structure presents the lower vulnerability toward the hotcarrier degradation effect, as indicated in Fig. 5. The immunity of gate-stack-based devices was also demonstrated for other types of architectures<sup>[25]</sup>.

#### 5. Conclusion

In this work, original analytical models that include hotcarrier effects for symmetrical lightly doped gate-stack doublegate (GS DG) MOSFETs are presented. The models were used to study the impact of interfacial hot-carrier on the device electrical parameters such as drain current and inversion charge for GS DG MOSFETs. In addition, the proposed models inherit all the favorable features from the accurate models associated with each regime. Therefore, all the regions of operation and the transitions are correctly described without charge-sheet approximation or fitting parameters. A good match is shown between model predicted values and 2D device simulations done with similar physical effects turned on. Finally, the closedform expressions to model various device parameters can be easily implemented into circuit simulators such as PSPICE for more accurate predictions of DG FET-based circuits.

### References

- Djeffal F, Dibi Z, Hafiane M L, et al. Design and simulation of a nanoelectronic DG MOSFET current source using artificial neural networks. Mater Sci Eng C, 2007, 27: 1111

- [2] Ortiz-Conde A, Garcia-Sanchez F J, Muci J, et al. A review of core compact models for undoped double-gate SOI MOSFETs. IEEE Trans Electron Devices, 2007, 54(1): 131

- [3] Song J, Yu B, Yuan Y, et al. A review on compact modeling of multiple-gate MOSFETs. IEEE Trans Circuits Syst, 2009, 56(8): 1858

- [4] Djeffal F, Ghoggali Z, Dibi Z, et al. Analytical analysis of

nanoscale multiple gate MOSFETs including effects of hotcarrier induced interface charges. Microelectron Reliab, 2009, 49: 377

- [5] Bentrcia T, Djeffal F. Compact modeling of multi-gate MOS-FET including hot-carrier effects. In: Kwon M J, ed. Chapter 4, CMOS technology, Series: electrical engineering developments. New York: Nova Science Publishers, 2011: 135

- [6] Pagey M P. Hot-carrier reliability simulation in aggressively scaled MOS transistors. PhD Dissertation, Electrical Engineering Department, Vanderbilt University, Nashville, Tennessee, USA, 2003

- [7] Ghoggali Z, Djeffal F, Lakhdar N. Analytical analysis of nanoscale double-gate MOSFETs including the hot-carrier degradation effects. International Journal of Electronics, 2010, 97(2): 119

- [8] Arora N. MOSFET modeling for VLSI simulation theory and practice. In: International Series on Advances in Solid State Electronics and Technology. Singapore: World Scientific Publishing, 2007

- [9] Munteanu D, Autran J L, Loussier X, et al. Quantum shortchannel compact modeling of drain-current in double-gate MOS-FET. Solid-State Electron, 2006, 50: 680

- [10] Taur Y. An analytical solution to a double-gate MOSFET with undoped body. IEEE Electron Device Lett, 2000, 21: 245

- [11] Djeffal F, Meguellati M, Benhaya A. A two-dimensional analytical analysis of subthreshold behaviour to study the scaling capability of nanoscale graded channel gate stack DG MOSFETs. Physica E: Low-Dimensional Systems and Nanostructures, 2009, 41: 1872

- [12] Nishida T, Sah C T. A physically based mobility model for MOS-FET numerical simulation. IEEE Trans Electron Devices, 1987, 34: 310

- [13] Leblebici Y, Kang S M. Modelling of nMOS transistors for simulation of hot-carrier induced device and circuit degradation. IEEE Trans Computer-Aided-Design, 1992, 11(2): 235

- [14] Hariharan V, Vasi J, Rao V R. Drain current model including velocity saturation for symmetric double-gate MOSFETs. IEEE Trans Electron Devices, 2008, 55(8): 2173

- [15] Yu B, Song J, Yuan Y, et al. A unified analytic drain current

model for multiple-gate MOSFETs. IEEE Trans Electron Devices, 2008, 55(8): 2157

- [16] Taur Y, Liang X, Wang W, et al. A continuous analytic draincurrent model for DG MOSFETs. IEEE Electron Device Lett, 2004, 25(2): 107

- [17] Jiménez D, Iñíguez B, Suñé J, et al. Continuous analytic I-V model for surrounding-gate MOSFETs. IEEE Electron Device Lett, 2004, 25(8): 571

- [18] Bentrcia T, Djeffal F, Arar D. An analytical two dimensional subthreshold current model for nanoscale GC GS DG MOSFET including interfacial traps effects. 2nd International Conference on Electronic Systems, Batna, Algeria, 2009: 173

- [19] Dey A A, Chakravorty A, DasGupta N, et al. Analytical model of subthreshold current and slope for asymetric 4-T and 3-T double gate MOSFETs. IEEE Trans Electron Devices, 2008, 55: 3442

- [20] Bentrcia T, Djeffal F, Abdi M A, et al. A compact analytical current model including traps effects for GS DG MOSFETs. 14th International Workshop on Symbolic and Numerical Methods, Modeling and Applications to Circuit Design, Gammarth, Tunisia, 2010

- [21] Djeffal F, Bentrcia T, Bendib T. An analytical drain current model for undoped GSDG MOSFETs including interfacial hot-carrier effects. Phys Status Solidi C, 2011, 8(3): 907

- [22] Pop E. Self-heating and scaling of thin body transistors. PhD Dissertation, Electrical Engineering Department, Stanford University, 2004

- [23] Jomaah J, Ghibaudo G, Balestra F. Modeling of self-heating effects in thin-film SOI MOSFET's as a function of temperature. Journal de Physique IV. Colloque C6, supplément au Journal de Physique III, 1994, 4: 57

- [24] Naseh S, Jamal Deen M, Chen C. Hot-carrier reliability of submicron nMOSFETs and integrated nMOS low noise amplifiers. Microelectron Reliab, 2006, 46: 201

- [25] Abdi M A, Djeffal F, Bentrcia T, et al. An analytical drain current model for GS GAA MOSFET including interfacial traps effects.

14th International Workshop on Symbolic and Numerical Methods, Modeling and Applications to Circuit Design, Gammarth, Tunisia, 2010

- [26] ATLAS: 2D device simulator. SILVACO International, 2008