# A simplified compact model of miniaturized cross-shaped CMOS integrated Hall devices

Huang Haiyun(黄海云)<sup>1,2</sup>, Wang Dejun(王德君)<sup>1,†</sup>, Li Wenbo(李文波)<sup>1</sup>, Xu Yue(徐跃)<sup>3</sup>, Qin Huibin(秦会斌)<sup>2</sup>, and Hu Yongcai(胡永才)<sup>2</sup>

<sup>1</sup>School of Electronic Science and Technology, Faculty of Electronic Information and Electronic Engineering, Dalian University of Technology, Dalian 116024, China

<sup>2</sup>Institute of New Electron Devices, Hangzhou Dianzhi University, Hangzhou 310018, China

<sup>3</sup>College of Electronic Science & Engineering, Nanjing University of Posts and Telecommunications, Nanjing 210003, China

**Abstract:** A simplified compact model for a miniaturized cross-shaped CMOS integrated Hall device is presented. The model has a simple circuit structure, only consisting of a passive network with eight non-linear resistors and four current-controlled voltage sources. It completely considers the following effects: non-linear conductivity, geometry dependence of sensitivity, temperature drift, lateral diffusion, and junction field effect. The model has been implemented in Verilog-A hardware description language and was successfully performed in a Cadence Spectre simulator. The simulation results are in good accordance with the classic experimental results reported in the literature.

Key words: miniaturized Hall device; compact model; lateral diffusion; junction field effect DOI: 10.1088/1674-4926/33/8/084005 EEACC: 2570

# 1. Introduction

CMOS integrated Hall magnetic sensors have been widely applied in industrial control systems, intelligent instruments, consumer electronic products, and so on. They have demonstrated great advantages of high reliability, compact size, high accuracy and low cost since they are easily embedded on one chip with the electrical circuits in a standard CMOS process. Unfortunately, CMOS integrated Hall sensors have low sensitivity compared with BiCMOS Hall sensors. In addition, they are very vulnerable to the variations of fabrication process, temperature drift, and package-induced mechanical stress<sup>[1]</sup>. These negative factors cause a serious offset and low frequency noise even in the absence of a magnetic field, which may be large enough to obscure the Hall signal. As a consequence, the special processing circuits with the spinning current method are widely used to eliminate offset and low frequency noise<sup>[1]</sup>. In order to facilitate the analysis of an electrical circuit with the integrated sensors, it is necessary to extract a precise simulation model which has to take into account important physical effects and the influence of materials and technological parameters on electrical characteristics. Moreover, the extracted model should be compatible with current circuit analysis software packages, such as SPICE-like simulators. In addition, the model should be accurate and simple.

With the continuous scaling down of CMOS processes, miniaturized integrated Hall device with low power, high sensitivity, and small size are urgently required. Demierre *et al.* proposed a miniaturized Hall device with an N-well implantation widow of 2.4  $\mu$ m, and Janossy *et al.* developed an even smaller Hall device with an active area of about 0.1 × 0.1  $\mu$ m<sup>2</sup> in silicon technology<sup>[2, 3]</sup>. Owing to an obvious reduction of doping level resulting from the N-well lateral diffusion,

the current-related sensitivity of miniaturized Hall devices is greatly improved compared with that of conventional Hall devices. Unfortunately, miniaturized Hall devices suffer from the junction field effect more easily, which can result in a higher offset. Therefore, the simulation model for miniaturized Hall devices should be improved, which should appropriately analyze the lateral diffusion effect during the process and the junction field effect. Several previous models fail in simultaneously simulating the non-linear conductivity, the shaped-dependent sensitivity, temperature drift, lateral diffusion, etc.<sup>[4-6]</sup> Recently, a completely scalable accurate lumped-circuit model was proposed by Dimitropoulos et al.<sup>[7]</sup>. This model performed well in analyzing geometrical, temperature, field-dependent mobility and junction field effects for several Hall sensors. It consists of the basic components, including JFETs and currentcontrolled current sources. The amount of these components can be freely increased to achieve a required accuracy at the expense of computation efficiency. However, this macro model increases circuit simulation complexity. In addition, it needs an accurate JEFT device model, which cannot usually be provided by using standard CMOS technology.

In this paper, a simplified compact model for miniaturized cross-shaped CMOS integrated Hall devices is developed. The model only consists of a passive network, including eight nonlinear resistances and four current-controlled voltage sources. It completely covers the following phenomena: the lateral diffusion of the N-well, the junction field effect, the non-linear conductivity effect, the geometrical effect, and temperature drift. In this work, we mainly deal with the sensors working in a weak magnetic field; accordingly, two strong magnetic-fieldrelated effects of magneto-resistance and carriers scattering are not taken into account. The model has been implemented in Verilog-A hardware description language with only ten key

<sup>†</sup> Corresponding author. Email: dwang121@dlut.edu.cn Received 21 July 2011, revised manuscript received 19 March 2012

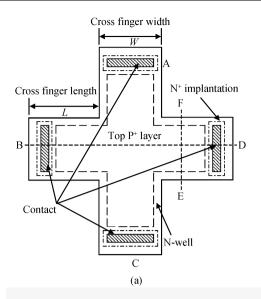

Fig. 1. Cross-shaped Hall sensor fabricated in standard CMOS technology. (a) Top view. (b) View with the cross-section along BD line. (c) View with the cross-section along EF line.

technological and physical parameters and can be conveniently used in standard SPICE-like EDA tools. It is noted that besides the cross-shaped Hall devices, the model is also suitable for other horizontal Hall devices with symmetrical shapes, such as square or diamond.

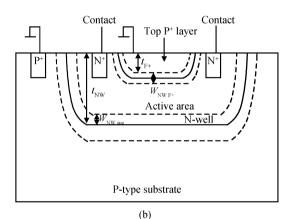

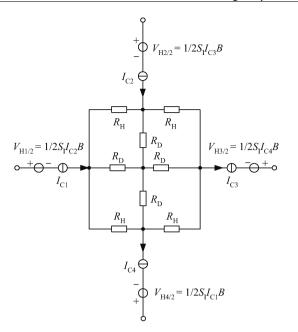

Fig. 2. A simplified model for the cross-shaped CMOS integrated Hall devices.

# 2. The simplified compact model

Nowadays, the cross-shaped Hall device with a 90° symmetry structure (seen in Fig. 1) has been broadly used due to its relative high sensitivity and immunity to alignment tolerances from the fabrication  $\operatorname{process}^{[5, 6]}$ . Here, the active area of a Hall device is usually implemented by a lowly doped N-well diffusion region which is isolated from the P-type substrate by the reverse-biased well/substrate p–n junction. In order to reduce flicker noise and surface carrier losses, a shallow highly doped P<sup>+</sup> conductive top layer often covers the surface of the active area. The P-type substrate and P<sup>+</sup> top layer are generally grounded together. In addition, there are four contact regions in the N-well, which are highly N<sup>+</sup> doped concentration with the source and drain formation processing step in CMOS technology.

#### 2.1. Structure of the model

The conventional compact model is based on a 4-resistance Wheatstone bridge to model the behaviors of Hall sensors. For the 4-resistance model, the value of equivalent resistance between two adjacent contacts is not accurate since the current flowing through the two adjacent contacts does not effectively cross the central region of the device. In addition, it cannot accurately model the offset induced by the piezo-resistance effect of silicon. In contrast to the complicated Dimitropoulos model mentioned above, a simplified 8-resistance symmetric model is developed, as illustrated in Fig. 2. Here, besides the four resistances  $R_{\rm H}$  on the H-bridge, the other four resistances  $R_{\rm D}$  sit between the contacts of each diagonal, respectively. In addition, there are four voltage sources  $V_{\text{H}i/2}$  (i = 1 to 4) used to model the Hall generator. Each Hall voltage source  $V_{\text{H}i/2}$  is controlled by a current source  $I_{ci}$  (i = 1 to 4) flowing through the closer contact and is proportional to the perpendicular magnetic field and bias current. Here,  $I_{ci}$  as a circuit branch current measurement is a zero-voltage current source.

In order to determine the values of the two resistances  $R_{\rm H}$  and  $R_{\rm D}$ , we skillfully combine the Van der Pauw method and the model's circuit structure<sup>[8–10]</sup>. In the Van der Pauw method, the N-well sheet resistance  $R_{\rm s}$  of the Hall plate is related to one measured resistance value of  $R_{\rm AB, CD}$  by

$$R_{\rm AB,\,CD} = \frac{\ln 2}{\pi} R_{\rm s},\tag{1}$$

where  $R_{AB, CD} = V_{CD}/I_{AB}$  denotes the potential difference between contacts C and D per current flowing  $I_{AB}$  from contact A to contact B. The contacts of A, B, C and D are illustrated in Fig. 1(a).

Meanwhile, in terms of the model structure of the Hall plate,  $R_{AB,CD}$  can be calculated by

$$R_{\rm AB, CD} = \frac{R_{\rm H}}{4} \frac{2R_{\rm D} - R_{\rm H}}{2R_{\rm D} + R_{\rm H}}.$$

(2)

On the other hand, the internal equivalent resistance between two diagonal contacts, A and C, can be obtained according to the circuit structure of the model and the geometrical structure of the Hall device:

$$R_{\rm AC} = \frac{2R_{\rm D}R_{\rm H}}{2R_{\rm D} + R_{\rm H}} = \left(2\frac{L}{W} + \frac{2}{3}\right)R_{\rm s}.$$

(3)

Here, 2L/W + 2/3 is the effective number of squares of the Nwell diffusion resistance. *L* and *W* are the finger length and finger width of the cross-shaped Hall devices, respectively. The center square number of the cross-shaped Hall devices is approximately reduced to 2/3 because the two fingers for sensing Hall signal are placed in parallel. Using Eqs. (1), (2) and (3), we finally obtain

$$R_{\rm H} = \frac{2R_{\rm s}}{\pi} \left[ \left( 2\frac{L}{W} + \frac{2}{3} \right) \pi - 2\ln 2 \right], \tag{4}$$

and

$$\frac{R_{\rm H}}{R_{\rm D}} = 2 - \frac{8}{\pi} \frac{\ln 2}{2L/W + 2/3}.$$

(5)

#### 2.2. Geometry dependent sensitivity effect

When a magnetic field is orthogonally applied on the device plane and two diagonal contacts are biased with a current I or a voltage V, the Hall voltage  $V_{\rm H}$  appears on other two diagonal contacts. The equation linking Hall voltage  $V_{\rm H}$  with bias current and magnetic field is equal to

CID

and

$$V_{\rm H} = S_{\rm I} I B, \qquad (6)$$

$$S_I = \frac{Gr_{\rm H}}{qN_{\rm D,\,NW}t_{\rm eff}},\tag{7}$$

where  $S_{\rm I}$  is defined as the current related sensitivity of the Hall device, which is determined by a geometrical correction factor G, effective thickness  $t_{\rm eff}$  of the Hall device, Hall factor  $r_{\rm H}$  of the majority carriers and the N-well doping concentration  $N_{\rm D, NW}$ .

For a cross-shaped Hall device, if the geometrical condition of  $W/2L \le 0.39$  is met, G can be calculated by following equation with accuracy better than  $0.5\%^{[11]}$ :

$$G = 1 - 5.0267 \frac{\theta_{\rm H}}{\tan \theta_{\rm H}} \exp\left(-\frac{\pi}{2} \frac{W + 2L}{W}\right), \qquad (8)$$

where  $\theta_n = \tan^{-1}(\mu_H B)$  is the Hall angle.  $\mu_H = r_H \mu_n$  is the Hall mobility.  $\mu_n$  is the electron mobility.

If the applied magnetic field is low, Eq. (8) can be further simplified to

$$G = 1 - \exp\left(-\frac{\pi L}{W}\right). \tag{9}$$

After considering the geometrical effect, each Hall voltage  $V_{\text{H}i/2}$  in Fig. 2 is modeled using the current-controlled voltage sources with the following equation:

$$V_{\text{H}i/2} = \frac{1}{2} S_{\text{I}} I_{\text{C}i} B, \quad i = 1, 2, 3, 4.$$

(10)

#### 2.3. Non-linear conductivity effect

The sheet resistance of the N-well dominates the important behaviors of the model, which is defined as:

$$R_{\rm s} = \frac{1}{q\mu_{\rm n}N_{\rm D,\,NW}t_{\rm eff}}.$$

(11)

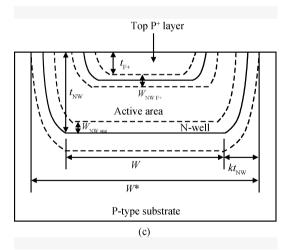

As shown in Fig. 1(b), the effective depth of an N-well is equal to

$$t_{\rm eff} = t_{\rm NW} - t_{\rm P+} - w_{\rm NW,\,SUB} - w_{\rm NW,\,P+},$$

(12)

$w_{\rm NW, SUB}(U_{\rm pn}) =$

$$\sqrt{\frac{2\varepsilon_{\rm s}}{q}}\frac{N_{\rm A,\,SUB}}{(N_{\rm A,\,SUB}+N_{\rm D,\,NW})N_{\rm D,\,NW}}(V_{\rm bi,\,SUB}+U_{\rm pn}),\quad(13)$$

$$w_{\rm NW, P+}(U_{\rm pn}) = \sqrt{\frac{2\varepsilon_{\rm s}}{q} \frac{N_{\rm A, P+} + N_{\rm D, NW}}{N_{\rm A, P+} N_{\rm D, NW}} (V_{\rm bi, P+} + U_{\rm pn})}.$$

(14)

Here,  $t_{\text{NW}}$  is the depth of N-well implantation, and  $t_{\text{P+}}$  is the effective thickness of the top conductive layer.  $V_{\text{bi, P+}}$  and  $V_{\text{bi, SUB}}$  are the built in potential of PN junction,  $V_{\text{bi, P+}} = \frac{KT}{q} \ln \frac{N_{\text{A, P+}}N_{\text{D, NW}}}{n_i^2}$  and  $V_{\text{bi, SUB}} = \frac{KT}{q} \ln \frac{N_{\text{A, SUB}}N_{\text{D, NW}}}{n_i^2}$ .  $N_{\text{D, NW}}$ ,  $N_{\text{A, P+}}$ ,  $N_{\text{A, SUB}}$  are defined as the doping concentration of the N-well, the top P<sup>+</sup> layer and the substrate, respectively.  $w_{\text{NW, SUB}}$  is the bottom depletion region at the N-well side between the N-well and the P-type substrate.  $w_{\text{NW, P+}}$  is the upper depletion region situated between the N-well and the top P<sup>+</sup> conductive layer.

It is well known that the thickness of a depletion region is obviously changed by the reverse biased PN junction voltage  $U_{pn}$ . Therefore, the sheet resistance  $R_s$  suffers from strong voltage dependence of non-linearity. Compared with the bottom depletion region, the thickness of the upper depletion region is smaller due to the high doping of the top P<sup>+</sup> layer. As a result, the thickness variation of the upper depletion region induced by a negative bias voltage can be ignored. According

$( \cap$

to Eq. (11), a Taylor expansion up to second order with Lagrange's remainder term of the third order. Since the value of the remainder term is small, it can be neglected and a simplified equation for calculating the voltage dependence of sheet resistance  $R_s$  is obtained<sup>[6, 10]</sup>:

$$R_{\rm s}(U_{\rm pn}) = \frac{1}{q\mu_{\rm n}N_{\rm D,\,NW}(t_{\rm eff}^* - \sqrt{k_1V_{\rm bi}})} \\ + \frac{1}{2}\frac{\sqrt{k_1V_{\rm bi}}}{q\mu_{\rm n}N_{\rm D,\,NW}(t_{\rm eff}^* - \sqrt{k_1V_{\rm bi}})^2V_{\rm bi}}U_{\rm pn} \\ + \left[-\frac{1}{8}\frac{\sqrt{k_1V_{\rm bi}}}{(t_{\rm eff}^* - \sqrt{k_1V_{\rm bi}})V_{\rm bi}^2} + \frac{1}{4}\frac{k_1}{(t_{\rm eff}^* - \sqrt{k_1V_{\rm bi}})^2V_{\rm bi}}\right] \\ \times \left[q\mu_{\rm n}N_{\rm D,\,NW}\left(t_{\rm eff}^* - \sqrt{k_1V_{\rm bi}}\right)\right]^{-1}U_{\rm pn}^2 + O(U_{\rm pn}^3) \\ \approx R_{\rm s}(0\,\rm V) + BBR_1R_{\rm s}(0\,\rm V)U_{\rm pn} + BBR_2R_{\rm s}(0\,\rm V)U_{\rm pn}^2,$$

(15)

where  $R_s(0 \text{ V})$  is the zero-biased N-well sheet resistance of a Hall device and its two reverse biased voltage coefficients are described by BBR<sub>1</sub> and BBR<sub>2</sub>.  $t_{\text{eff}}^* = t_{\text{NW}} - t_{\text{P+}} - w_{\text{NW},\text{P+}}$ (0 V), and  $k_1 = \frac{2\varepsilon_{\text{si}}}{q} \frac{N_{\text{A,SUB}}}{(N_{\text{A,SUB}} + N_{\text{D,NW}})N_{\text{D,NW}}}$ . Besides the Hall device resistances, the sensitivity is also

Besides the Hall device resistances, the sensitivity is also subject to a reverse biased PN junction effect and can be calculated by using the same method. The current-related magnetic sensitivity is given by

$$S_{\rm I}(U_{\rm pn}) = S_{\rm I} \left( 1 + {\rm BBS}_1 \cdot U_{\rm pn} + {\rm BBS}_2 \cdot U_{\rm pn}^2 \right). \tag{16}$$

Here, the coefficients of BBS<sub>1</sub> and BBS<sub>2</sub> are the first and second voltage dependence of sensitivity, respectively.

#### 2.4. Lateral diffusion effect

Special attention should be given to the lateral diffusion effect of miniaturized Hall devices with a narrow N-Well implantation strip. Based on the N-well implantation depth and its average doping concentration  $N_{D,NW}$ , the N-well implantation dose using the depth of implantation  $t_{NW}$  can be estimated by<sup>[12]</sup>:

$$D_{\rm NW} = (N_{\rm A, SUB} + N_{\rm D, NW})t_{\rm NW}.$$

(17)

Being a miniaturized Hall device, the lateral diffusion effect of an N-well cannot be ignored. Since the lateral diffusion length is proportional to the depth of implantation, the equivalent implantation length is defined with a factor of k (see Fig. 1(c)):

$$W^* = W + 2kt_{\rm NW}.$$

(18)

Here, W is the implantation width of N-well (i.e. cross finger width in Fig. 1(c)),  $k \approx 0.8$  for a low doped substrate.

Considering the lateral diffusion of N-well implantation, an approximate half ellipse cross-section with area  $S^*$  in Fig. 1(c) is obtained:

$$S^* = \frac{\pi}{4} W^* t_{\rm NW}.$$

(19)

From Eqs. (17), (18) and (19), the effective N-well doping level after implantation through a narrow strip can be calculated by<sup>[12]</sup>:

$$N_{\rm D, NW}^{*} = \frac{D_{\rm NW}}{S^{*}} W - N_{\rm A, SUB}$$

=  $\frac{4}{\pi} \frac{W}{W^{*}} (N_{\rm A, SUB} + N_{\rm D, NW}) - N_{\rm A, SUB}.$  (20)

#### 2.5. Junction field effect

We have known that the N-well of cross-shaped Hall devices is surrounded by P-type substrate and a top P<sup>+</sup> layer. The active cross-section of a Hall device is obviously decreased because of the reverse biased PN junction field effect (JFE). The narrower the implantation width of a Hall device is, the more serious the junction field effect becomes. For miniaturized Hall sensors, we should first take into account the lateral diffusion effect. Therefore, the thickness of the two depletion regions in Eqs. (13) and (14) should be recalculated with the effective N-well doping concentration  $N_{D, NW}^*$ .

According to the Hall sensor cross-section shown in Fig. 1(c) and considering the junction field effect, the cross-section  $S_{JFE}^*$  of the N-well active area is obtained<sup>[12]</sup>:

$$S_{\rm JFE}^* = \frac{\pi}{4} (t_{\rm NW} - t_{\rm p+} - w_{\rm NW,\,SUB} - w_{\rm NW,\,P+}) \\ \times (W + 2k t_{\rm NW} - 2w_{\rm NW,\,SUB}).$$

(21)

Hence, the sheet resistance per square  $R_s$  in Eq. (11) is rewritten as:

$$R_{\rm s} = \frac{1}{q\mu_{\rm n} N_{\rm D, NW}^*} \frac{W}{S_{\rm JFE}^*}.$$

(22)

Accordingly, the current related sensitivity  $S_1$  in Eq. (7) is rewritten as:

$$S_{\rm I} = \frac{G r_{\rm H}}{q N_{\rm D, NW}^*} \frac{w}{S_{\rm JFE}^*}.$$

(23)

## 2.6. Temperature effect

It is well known that Hall device characteristics, such as sensitivity, resistance of N-well and offset, are sensitive to temperature drift. The temperature behavior of N-well sheet resistance can be well approximated by the second order polynomial:

$$R_{\rm s}(T, U_{\rm pn}) = R_{\rm s}(U_{\rm pn}) \cdot \left(1 + R_{\rm TC1}\Delta T + R_{\rm TC2}\Delta T^2\right).$$

(24)

Here,  $\Delta T = T - 300$  K,  $R_{TC1}$  and  $R_{TC2}$  are temperature coefficients which can be directly obtained from the foundry technology files.

Assuming the *G* and  $t_{\text{eff}}$  are independent on temperature, the thermal drift of current related sensitivity  $\alpha_{\text{SI}}$  can be formulated by<sup>[11–13]</sup>

$$\alpha_{\rm SI} = \frac{1}{S_{\rm I}} \frac{\mathrm{d}S_{\rm I}}{\mathrm{d}T} = \alpha_{\rm rH} - \alpha_{\rm N}, \qquad (25)$$

where  $\alpha_{rH}$  and  $\alpha_N$  are the temperature coefficient of the Hall factor and the N-well carrier concentration, respectively.

Due to the combination of the temperature dependent  $\alpha_{rH}$ and  $\alpha_N$ ,  $\alpha_{SI}$  is about in the range of  $\pm$  500 ppm/°C throughout

| Table 1. Key model parameters (AWS CAQ 0.8 µm CWOS technology). |                                      |                                    |

|-----------------------------------------------------------------|--------------------------------------|------------------------------------|

| Parameters                                                      | Definition                           | Default value                      |

| N <sub>D, NW</sub>                                              | Doping concentration in N-well       | $4 \times 10^{16} \text{ cm}^{-3}$ |

| $N_{\rm A, P+}$                                                 | Doping concentration in top P+ layer | $1 \times 10^{20} \text{ cm}^{-3}$ |

| $N_{\rm A,SUB}$                                                 | Doping concentration in substrate    | $1 \times 10^{16} \text{ cm}^{-3}$ |

| t <sub>NW</sub>                                                 | Depth of N-well                      | $4 \mu \mathrm{m}$                 |

| $t_{\rm P+}$                                                    | Depth of top P+ layer                | 0.3 μm                             |

| $\mu_{ m n}$                                                    | Electrons mobility                   | 950 cm <sup>2</sup> /(V·s)         |

| $r_{ m H}$                                                      | Hall factor                          | 1.2                                |

| $R_{\rm TC1}$                                                   | Temperature coefficient of N-well    | 0.5 %/°C                           |

| $R_{\rm TC2}$                                                   | Temperature coefficient of N-well    | 20 ppm/°C                          |

| $\alpha_{\rm SI}$                                               | Temperature coefficient of $S_{I}$   | $\pm 500 \text{ ppm/°C}$           |

Table 1. Key model parameters (AMS CXQ 0.8  $\mu m$  CMOS technology)

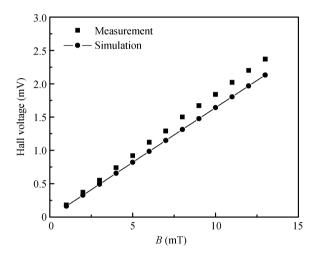

Fig. 3. The simulated and measured output Hall voltage versus magnetic field.

the industrial temperature range for a typical N-well doping concentration of  $4 \times 10^{16}$  cm<sup>-3[13]</sup>. A zero temperature coefficient of sensitivity could be obtained near room temperature.

Considering the thermal drift effect, Eq. (16) can be rewritten as

$$S_{\rm I}(\Delta T, U_{\rm pn}) = S_I(U_{\rm pn}) \left(1 + \alpha_{\rm SI} \Delta T\right).$$

<sup>(26)</sup>

#### **3. Simulation results**

The new simulation model code has been implemented in behavioral Verilog-A language, including ten key technological and physical parameters. The model simulation was performed using AMS CXQ 0.8 µm CMOS technological parameters by using a Cadence Spectre simulator. Table 1 shows the used key parameters<sup>[10-12]</sup></sup>. For the CMOS N-well, with a doping concentration of  $4 \times 10^{16}$  cm<sup>-3</sup>, the electrons mobility  $\mu_n$  and Hall factor  $r_H$  are about 950 cm<sup>2</sup>/(V·s) and 1.2, respectively. It is noted that the parameter of N<sup>+</sup> contacts with 0.3  $\mu$ m thickness and 6 × 10<sup>19</sup> cm<sup>-3</sup> doping level is not included in this model. Since the N<sup>+</sup> contact resistance is relatively very small compared to the N-Well resistance, it can be neglected. To verify the accuracy of the model, the corresponding experimental results of cross-shaped Hall devices fabricated in the same technology are compared to the model's simulation results<sup>[11, 12]</sup>.

Figure 3 shows the simulated Hall voltage versus the variations of magnetic field at room temperature. When the Hall

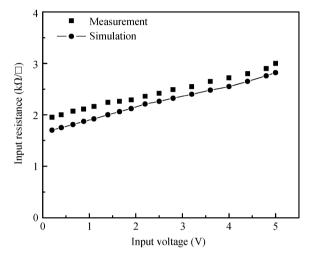

Fig. 4. Comparisons between the simulations and measurements of N-well resistance per square versus input voltage.

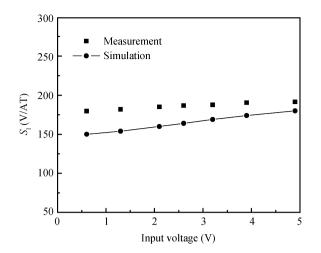

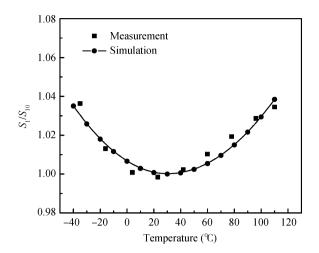

device implantation width is 2.4  $\mu$ m and the Hall device is biased with 1 mA, the simulated Hall voltage is about 0.164, 0.82 and 1.64 mV at 1, 5 and 10 mT magnetic fields, respectively. A current-related sensitivity of about 164 V/AT is obtained. In contrast to the plot of measurements, as shown in Fig. 3, this value is close to the tested value of about 185 V/AT<sup>[11, 12]</sup>. Figure 4 illustrates the simulated N-well resistance per square versus variations of input voltage for 2.4  $\mu$ m implantation width. The simulated input resistance per square is increased from 1.7 to 2.8 k $\Omega/\Box$  when the input voltage sweeps from 0 to 5 V. By comparison, the simulation results are approximated to the measured results shown in Fig. 4<sup>[12]</sup>. Further, a comparison of the current related sensitivity versus different input voltages between the simulated and tested results is shown in Fig. 5. We observe that the simulated current-related sensitivity increases from 150 to 180 V/AT with the input voltage increasing from 0 to 5 V. The simulation results are in good accordance with the measured results<sup>[12]</sup>. Due to the voltage dependent junction field effect, the N-well thickness is decreased with the input voltage increasing. Accordingly, the current-related sensitivity is also increased. In addition, we simulated the thermal drift of the current related sensitivity without considering packaging stress. We suppose  $\alpha_{SI}$  linearly changes from -500 to 500 ppm/°C in the temperature range from -40 to 110 °C. Figure 6 shows the simulated and measured relative variation of  $\alpha_{\rm SI}$  (related to the value at 30 °C) as a function of temperature.

Fig. 5. Comparisons between the simulations and measurements of the current related sensitivity versus input voltage.

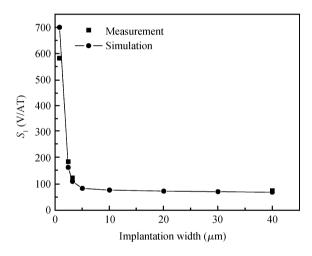

It can be observed that the measured zero temperature coefficient of  $S_1$  is present at about 20 °C, while it appears at 30 °C in the simulation. This is due to the zero temperature coefficient of  $S_{\rm I}$  usually fluctuating within the room temperature range for the actual Hall devices. So, we use a typical value of 30 °C in the simulation. On the whole, the simulation and experimental results achieves consistency when Hall sensor is liberated from packaging stress<sup>[11]</sup>. Finally, the model simulations of the current related sensitivity for different implantation widths are compared, as shown in Fig. 7. It can be obviously observed that the current related sensitivity is greatly improved with a reduction in implantation width. This is because the lateral diffusion effect results in an obvious decrease in the N-well doping concentration. For a large Hall device with 40  $\mu$ m implantation width, the model's simulation is in very good agreement with the measured results. However, when the N-well implantation width is reduced to 0.8  $\mu$ m, the error becomes a bit larger<sup>[12]</sup>. This is because the N-well lateral diffusion effect is over estimated. The N-well doping level is higher than the actual value so that the simulated  $S_{\rm I}$  is obviously higher than the tested result. Over all, a good match between the simulation and experiments is obtained for the small Hall devices when the N-well implantation width is higher than 2.4  $\mu$ m.

## 4. Conclusions

A simplified compact simulation model for miniaturized CMOS-integrated Hall devices has been developed. The model only consists of a passive network, including eight non-linear resistors and four current-controlled voltage sources. Except for two physical stress-related effects (piezo-resistance and piezo-Hall effects) induced packaging, the model not only takes into account the non-linear conductivity, geometrical effect, and temperature drift, but also considers the lateral diffusion and junction field effect for the miniaturized Hall devices. The model has been written in Verilog-A hardware description language and only needs ten key technological and physical parameters. The used parameters can be easily obtained from device measurements or foundry technology files. The model does not need to use JFET model and can be directly performed in standard SPICE-like EDA tools such as Cadence Spectre.

Fig. 6. Comparisons between the simulated and measured relative variation of the current related sensitivity (related to the value  $S_{10}$  at 30 °C) versus temperature.

Fig. 7. Comparisons between the simulations and measurements of the current related sensitivity for different N-well implantation widths.

To prove the correctness and accuracy of the simplified model, the model simulation was performed using AMS CXQ 0.8  $\mu$ m CMOS technology parameters. The simulation results are in good agreement with the classic experimental results<sup>[11, 12]</sup>. Therefore, the simplified model is very suitable for the circuit design of Hall magnetic micro-system chips.

## References

- Bilotti A, Monreal G, Vig R. Monolithic magnetic Hall sensor using dynamic quadrature offset cancellation. IEEE J Solid-State Circuits, 1997, 32: 829

- [2] Boero G, Demierre M, Besse P A, et al. Micro-Hall devices: performance, technologies and applications. Sensors and Actuator A, 2003, 106: 314

- [3] Sandhu A, Masuda H, Kurosawa K, et al. Bismuth nano-Hall probes fabricated by focused ion beam milling for direct magnetic imaging by room temperature scanning Hall probe microscopy. Electron Lett, 2001, 37: 1335

- [4] Salim A, Manku T, Nathan A, et al. Modeling of magnetic-field sensitive devices using circuit simulation tools. 5th IEEE Solid-

State Sensor and Actuator Workshop, 1992: 94

- [5] Jovanovi E, Pesi T, Panti D. 3D simulation of cross-shaped Hall sensor and its equivalent circuit model. IEEE Trans Proc 24th International Conference on Microelectronics, 2004: 235

- [6] Schweda J, Riedling K. A nonlinear simulation model for integrated Hall devices in CMOS silicon technology. Proceedings of the International Workshop on Behavioral Modeling and Simulation, 2002: 14

- [7] Dimitropoulos P D, Drljaca P M, Popovic R S, et al. Horizontal Hall devices: a lumped-circuit model for EDA simulators. Sensors and Actuators A, 2007, 3: 161

- [8] Cornils M, Doelle M, Oliver. Sheet resistance determination using symmetric structures with contacts of finite size. IEEE Trans

Electron Devices, 2007, 54: 2756

- [9] Udo A. Limits of offset cancellation by the principle of spinning current Hall probe. Proceedings of IEEE Sensors, 2004: 1117

- [10] Xu Y, Pan H B. An improved equivalent simulation model for CMOS integrated Hall plates. Sensors, 2011, 11: 6284

- [11] Randielovic Z. Low-power high sensitivity integrated Hall magnetic sensor microsystem. EPFL: Lausanne, Switzerland, 2000

- [12] Demierre M. Improvements of CMOS Hall microsystems and application for absolute angular position measurements. PhD Thesis, EPFL: Lausanne, Switzerland, 2003

- [13] Manic D, Petr J, Popovic R S. Temperature cross-sensitivity of Hall device in submicron CMOS technology. Sensors and Actuators A, 2000, 85: 244