报

# CMOS 工艺中 GG-NMOS 结构 ESD 保护电路设计\*

#### 杜鸣 郝跃 朱志炜

(西安电子科技大学微电子学院, 宽禁带半导体材料与器件教育部重点实验室, 西安 710071)

摘要:采用 GG·NMOS 结构的 ESD 保护电路的工作原理和对其进行的 ESD 实验,提出了一种保护电路的栅耦合技术方案,并达到了预期效果.通过实验可以看出其性能达到了人体放电模式的 2 级标准.在模拟的基础上可确定损伤的机理和位置,从而给出了由 ESD 导致的栅氧化层损伤的微观机制.

关键词: ESD; GGNMOS; 人体放电模式; 栅耦合

**PACC:** 7360F; 6120J; 8240Q

中图分类号: TN386 文献标识码: A 文章编号: 0253-4177(2005)08-1619-04

#### 1 引言

ESD (electrostatic discharge) 是当今 MOS 集成电路中最重要的可靠性问题之一[1]. ESD 现象主要能对电子器件造成以下的损坏:在半导体器件中由于介质击穿而导致氧化物薄膜破裂;由于 EOS(electrical overstress) 引起过热导致金属导线熔化;由于寄生的 PNPN 结构而导致 CMOS 器件闭锁;使元器件结构中产生潜藏的缺陷,它们并不立即失效但会引起断续的故障以及长期可靠性问题,这种损伤非常微弱,不易发现,即潜在损伤[2]. 集成电路工业由 ESD 导致的损失是一个非常严重的问题. 为此,国际上对 ESD 作了很多的研究,并提出了相关的机理和模型[3~5].

对 ESD 损伤的防护手段可以分为两个方面:一方面是外部因素,即改善器件和电路的生产、工作、存储环境和规范<sup>[6]</sup>;另一方面是内部因素,即提高片内 ESD 保护电路的性能,这方面也是目前提高集成电路抗 ESD 性能的主要手段.

本文设计了一个 ESD 保护电路,说明了它的工作原理,以及这个保护电路抗 ESD 性能的实验结果,最后提出了一些改进方案.

## 2 ESD 保护电路及其工作原理

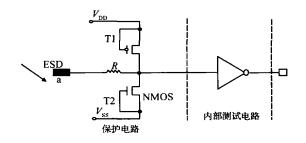

一个好的片内保护电路应该能够可以抵抗多次 ESD 应力;还应该具有足够快的开启速度以及低的 开启电阻,以保证在 ESD 事件发生时,能够快速的 将电压钳位,使得相应的被保护电路不受损伤 [7.8]。此外,保护电路还应该具有独立性,在被保护电路工作时,保护电路应该是高阻状态,不影响被保护内部 电路的正常工作.本文的 ESD 保护电路,是采用  $0.8\mu_{\rm m}$  标准 CMOS 工艺(加 ESD 注入工艺)得到的,其等效电路结构以及保护电路截面图如图 1 所示.图中 T2 为 NMOS,  $W/L=648/1.8\mu_{\rm m}$ , T1 为 PMOS,  $W/L=1178/1.8\mu_{\rm m}$ , R 是扩散电阻.

当在 PAD 上施加正的 ESD 脉冲时,下拉 NMOS 被触发,内部的寄生双极结构开启,对 ESD 电流进行旁路.在 PAD 上施加负的 ESD 脉冲时, PMOS 内部的寄生双极结构开启,旁路 ESD 电流.电阻 R 主要起到了限流的作用.

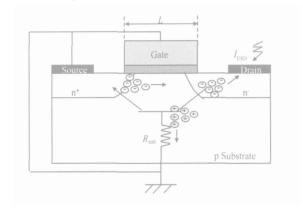

该保护电路采用的是 GGNMOS 结构的保护单元,它是利用瞬间崩溃(Snapback)效应来钳位瞬态高压和进行分流的,如图 2 所示. 这种方法有钳位电压低和低开启电阻的特点. 文中以 NMOS 为例

<sup>\*</sup>国家高技术研究发展计划资助项目(批准号:2003AA1Z1630)

杜 鸣 男,1979年出生,博士研究生,主要从事大规模集成电路可靠性研究.

郝 跃 男,1958年出生,教授,博士生导师,主要从事微电子学与半导体器件的研究.

朱志炜 男,1975年出生,博士研究生,主要从事集成电路可靠性研究.

图 1 保护结构电路图

Fig. 1 Circuit figure of protection structure

(栅接电源的 PMOS 工作原理与栅接地 NMOS 保护结构相同)来说明它的工作原理.

图 2 横向寄生晶体管 Snapback 机理示意图

Fig. 2 Schematic figure of lateral parasitic transistor

由图 2 可知,当正脉冲(ESD)加在漏结上(n<sup>+</sup>/p),该结反偏,器件进入高阻抗状态,直到达到雪崩击穿(一次击穿)电压为止.由于处于高场状态,在耗尽区会产生电子-空穴对,电子被漏接触电极收集,而空穴被衬底接触电极收集.这样,相对于接地的源结,衬底的局部电势不断增加.当局部电势增加到足以使源极-衬底结正偏时,电子就从源区注入漏.此时,NMOS 管内部的寄生双极结构开启.一旦双极结构开启,电压就从最大值 V<sub>TI</sub>下降到最小值,达到维持电压后,所加电流就由寄生双极结构维持,即瞬间崩溃(Snapback)传导模式.在该区,由于衬底的电导调制作用,电阻为正值.

# 3 栅耦合技术和测试结果

由于防护元件尺寸较大,在布局上我们采取多分支形状(finger-type),但是研究发现,不同的分支导通电压不同.当发生 ESD 放电时,这些分支不一

定会一起导通,可能只有其中2,3 支先导通.这就会使得 ESD 电流集中流向这2,3 支,而其他分支仍然关闭. 所以它的 ESD 防护能力仅相当于这2,3 支的防护能力. 这就大大削弱了其 ESD 防护能力.

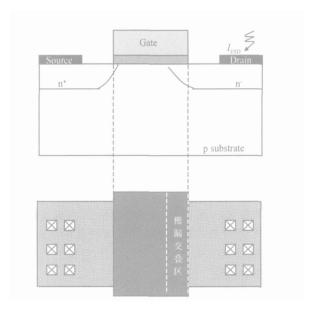

为了克服这种不均匀导通的情况,我们在版图设计中采取了一种利用电容耦合作用来使大尺寸元件能够均匀导通的设计.这种设计方案利用栅漏交叠区的结扩散电容做耦合元件,如图 3 所示.当有ESD 电压出现时,由于电容耦合作用,瞬间的电压变化会使 MOS 管的栅极电压跟着上升.因为 MOS管的栅极上施加耦合电压,所以大尺寸元件的分支会被一起导通而进入瞬间崩溃(Snapback)区域,对电压进行钳位.由于每一个分支都被导通,ESD能量被均匀地分散到每一个分支,从而有效地提高了其 ESD 防护能力.

图 3 栅耦合技术示意图

Fig. 3 Schematic figure of gate-couple technology

为了验证这个保护电路的抗静电能力,利用人体模型机从800~3000V,以200V为步幅的静电电压对此保护电路进行了 HBM (人体放电模式)的ESD测试.静电电压波形符合美883C标准,脉冲上升时间小于10ns,延迟时间为150±20ns,脉冲时间间隔为1ns.测试时,Vss公共端接地,Vdd公共端与输出端悬空,对输入端a进行ESD应力测试.

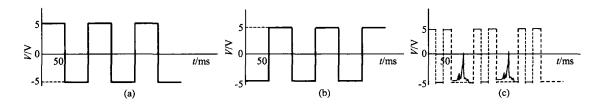

实际测试结果发现: ESD 应力在 2400V 以下 (包括 2400V)时,所有测试电路在经过应力后都符合原有规格,电路功能未失效. 输出信号与图 4(b)

一致. 当 ESD 应力在 2600V 时,有一个测试电路功能失效;ESD 应力在 2600V 以上时,所有测试电路的功能均失效. 电路输出信号如图 4(c) 所示,信号

完全失真,电路功能失效.由此得出,这个保护电路的抗静电能力可以达到 2600V,达到了人体放电模式 2 级标准(2000~3999V).

图 4 ESD 保护电路的测试结果 (a) 输入脉冲信号 ; (b) 未经过 ESD 应力的电路输出信号 ; (c) 经过 ESD 应力后失效的电路输 出信号

Fig. 4 Test results of ESD protection circuit (a) Input pulse signal; (b) Output circuit signal before ESD; (c) Output signal of failure circuit after ESD

### 4 ESD 导致的氧化层损伤微观机理

利用 Medici 进行了 Snapback 相关场的分布特性研究. 图 5 所示为空穴流的注入位置 ,图中表明了热量集中在该位置下方的漏结处 ,显示了工作中的热量扩散所造成不可恢复 ESD 损伤的初始位置 ,由此看出器件的损伤位置主要在栅漏交叠区 ,最终形成击穿 ,使得器件功能失效.

图 5 (a) 空穴流注入情况;(b) 漏端热量分布; I<sub>max</sub> = 50mA/ µm

Fig. 5 (a) Status of hole flux injection; (b) Thermal distribution of drain;  $I_{max} = 50 \text{mA}/\mu\text{m}$

加正栅压时,电子通过 Fowler-Nordheim 隧穿 效应从衬底注入,如果电场足够强,一些电子可以获 得足够高的能量,打在 Si —O 键上,发生碰撞电离, 产生新的电子-空穴对,一部分空穴在电场的作用下 漂向氧化物阴极,在 Si/SiO<sub>2</sub> 界面附近被俘获;电子 的迁移率很大,大多数被电场扫出 SiO2 层,只有极 少量的电子被陷阱俘获. 空穴在 Si/SiO2 过渡层的 俘获导致了氧化层空间正电荷的出现,使阈电压出 现负漂移,产生了潜在损伤.如果继续加高电场应 力,空穴继续被俘获,局部区域的陷阱密度大,俘获 的电荷多,导致局部电场和电流密度增大,这又加速 空穴的俘获,最终当局部电流密度达到某一特定值 时,就发生了击穿,在高电场应力下,不断产生陷阱, 一般认为击穿分为两步:第一步是注入热电子产生 空穴陷阱,它打断 Si —H 及应变 Si —O 弱键[9],导 致硅的悬挂键作为空穴陷阱,成为介质击穿的触发 位置:第二步是空穴被陷阱所俘获,使硅悬挂键 (O Si) 变三价硅键(O Si<sup>+</sup>),它不能保持三维四 面体结构,要倒塌至略为平坦结构,而这将增加其传 导性. 当在整个 SiO2 中产生局部倒塌的 O Si + 结 构构成传导通路时,就发生了介质击穿.

# 5 结论

本文设计了一个 ESD 保护电路结构,并对其工作原理以及测试结果进行了论述.这个保护电路的抗静电能力达到了人体放电模式 2 级标准.对如何提高这个保护电路的抗静电能力提出了一个改进方案,即栅耦合技术.通过模拟确定 ESD 所造成的器

件损伤的部位在栅漏交叠区域,并对氧化层损伤的机理进行了论述.这对于以后工作中提高器件 ESD 保护能力具有指导性意义.

#### 参考文献

- [1] Ma Wei, Hao Yue. ESD and its related mechanisms on LDD-CMOS. Chinese Journal of Semiconductors, 2003, 24(8):892 (in Chinese) [ 马巍,郝跃. LDD-CMOS 中 ESD 及其相关机理. 半导体学报, 2003, 24(8):892]

- [2] Ma Zhongfa, Zhuang Yiqi, Du Lei, et al. A sensitive testing technique to ESD latent damages in MOSFET. Chinese Journal of Semiconductors, 2002, 23(11):1211 (in Chinese) [马仲发,庄奕琪,杜磊,等.一种敏感的 MOSFET ESD 潜在损伤检测方法.半导体学报,2002,23(11):1211]

- [3] Sun Zmin ,Liu Litian ,Li Zhijian. Study on characteristics and optimization of MOSFET's with polysilicon-elevated source/drain. Chinese Journal of Semiconductors ,1998 ,19 (11):851 (in Chinese) [孙自敏 ,刘理天 ,李志坚. 深亚微米 PESD MOSFET 特性研究及优化设计. 半导体学报 ,1998 ,19 (11):851]

- [4] Yu Zongguang. New structures used for protection of sub-micron CMOS IC 's. Microelectronic Technology,2001,29(3):6 (in Chinese)[于宗光. 亚微米 CMOS 集成电路 ESD 保护新结构. 微电子技术,2001,29(3):6]

- [5] Unger B A. Electrostatic discharge failures of semiconductor devices. IEEE/ PROC IRPS, 1981:193

- [6] Shi Baohua Jia Xinzhang ,Zhang Desheng. Microelectronic device reliability. Xi 'an: Xidian University Publishing House, 1999:172 (in Chinese) [史保华,贾新章,张德胜. 微电子器件可靠性. 西安:西安电子科技大学出版社,1999:172]

- [7] Wu J Juliano P, Rosenbaum E. Breakdown and latent damage of ultrathin gate oxides under ESD stress conditions. Proceedings of the 22nd EOS/ ESD Symposium, 2000:287

- [8] Juliano P A, Rosenbaum E. Accurate wafer-level measurement of ESD protection device turn-on using a modified very fast transmission line pulse system. IEEE Trans Device Mater Reliab, 2001, 1:95

- [ 9 ] Thierauf S C, Anderson W R. I/O and ESD circuit design. In: Design of high-performance microprocessor circuits. Chandrakasan A, Bowhill W J, Fox F, ed. IEEE Press, 2001:377

# Design on an ESD Protection Circuit with GG NMOS Structure in CMOS Technology \*

Du Ming, Hao Yue, and Zhu Zhiwei

(Key Laboratory of Ministry of Education for Wide Band-Gap Semiconductor Materials and Devices, Microelectronics Institure, Xidian University, Xi'an 710071, China)

**Abstract:** An ESD protection circuit which uses a GG NMOS structure is presented. The operating principle and test results are depicted. An improved project ,gate-couple technology ,on the circuit is presented ,and the anticipated effect is achieved. The ability of the circuit achieves class 2 of the human-body model. It is also indicated that ESD induces damage of the gate oxide with microcosmic mechanisms ,where ESD occurs based on simulation.

Key words: ESD; GGNMOS; human-body model; gate-couple

PACC: 7360F; 6120J; 8240Q

**Article ID**: 0253-4177 (2005) 08-1619-04

<sup>\*</sup> Project supported by the National High Technology Research and the Development Program of China (No. 2003AA1Z1630)

Du Ming male, was born in 1979, PhD candidate. He is engaged in research on VLSI reliability.

Hao Yue male, was born in 1958, professor and adviser of PhD candidates. He is engaged in research on microelectronics and semiconductor devices.