Vol. 26 No. 9 Sep., 2005

# 一种抗辐照 SOI 反相器

## 赵洪辰 海潮和 韩郑生 钱 鹤 司 红2

(1 中国科学院微电子研究所,北京 100029) (2 钢铁研究总院,北京 100081)

摘要:制备了一种抗辐照 SOI 反相器,增加了一个上拉 pMOS1 和一个额外的 nMOS1.当受到辐照后,pMOS1 和 nMOS1 输出的高电平使下级输出管的源漏电压减小,降低了漏电流,有效地提高了输出端"高"电平.实验证明,该 反相器在经受 6  $\times$ 10<sup>5</sup> rad(Si) 的辐照后,输出"高"电平仍然未下降.

关键词:辐照效应;反相器;输出高电平

**EEACC:** 2570D; 2570F

中图分类号: TN432 文献标识码: A 文章编号: 0253-4177 (2005) 09-1829-04

## 1 引言

绝缘体上硅(SOI)技术实现了全介质隔离,比 体硅器件有更快的速度和更高的集成度[1],同时 SOI 中电荷收集体积很小,具有天然的抗单粒子翻 转和瞬时辐照能力[2]. 但是由于埋氧化层(BOX)和 LOCOS隔离的"鸟嘴"存在,未经加固的 SOI 器件 的抗总剂量辐照能力较弱,甚至不及体硅.目前已出 现了多种抗辐照加固工艺,如低温工艺[3]、氮氧化硅 栅介质[4]、降低 BOX 氧注入剂量并同时进行氮注 入[5]、采用环形栅结构[6] 等. 而采用适当的电路设 计,同样能够在常规工艺和器件结构下,有效地提高 电路整体的抗辐照能力. 例如,在 SRAM 存储单元 中两个相反的反相器的栅和漏之间加上反馈电阻, 能够提高 SRAM 的抗单粒子事件和剂量率辐照能 力. 电路设计同样能够应用于电路的抗总剂量辐照. 如图 1 所示的电路[7],放射量测定器测量器件阈值 电压漂移量与总剂量之间的关系,并产生一个反馈 电压. 通过比较器将这个反馈电压与参考电压进行 比较,随后输出一个数字信号.输出信号控制环振驱 动电荷泵,产生一个低于电路低电平的衬底参考电 压,从而使 nMOSFET 的阈值电压升高,与辐照引 起的阈值电压漂移相互抵消,保持器件阈值电压的 恒定.

本研究在 SIMOX 衬底上制备了一种抗辐照的 反相器 .能够有效减小总剂量辐照对电路工作状态

的影响,为 SOI 电路的进一步的抗辐照加固提供了一种选择.

## 2 器件制备

本研究应用部分耗尽工艺路线,采用 LOCOS 隔离,双多晶硅栅,即 pMOS 采用 p<sup>+</sup> 多晶硅栅, nMOS 采用 n<sup>+</sup> 多晶硅栅.选用 SIMOX 衬底,硅膜厚度和埋氧层厚度分别为 197nm 和 370nm. SOI CMOS 工艺过程主要为:光刻、刻蚀确定有源区;场区充分氧化至埋氧层;沟道注入调整阈值电压;20nm 氮化氧化合成栅介质;形成 350nm 多晶硅栅;LDD/LDS 注入;形成氧化物侧墙;源漏注入;RTA;淀积 Ti 形成自对准硅化物;最后淀积 BPSG、刻蚀接触孔、淀积和刻蚀 Al 合金等.

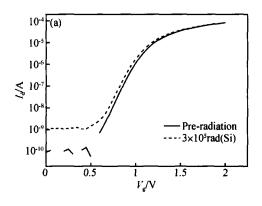

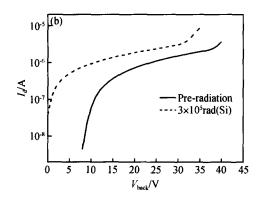

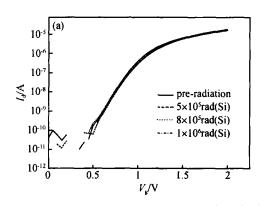

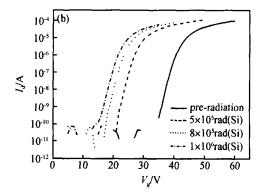

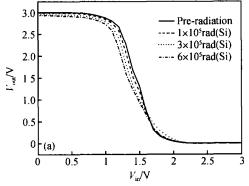

图 1 和图 2 分别给出了 20µm/1. 2µm 的条形栅和 H 型栅 SOI nMOSFET 在经过辐照后的正栅和背栅亚阈值特性,它们的工艺完全相同,结构上唯一不同的是: H 型栅器件是无边缘器件. 在经受 3 × 10<sup>5</sup> rad(Si) 的辐照后,条形栅器件的阈值电压变化不大,但出现了约 1nA 的漏电流;而 H 型栅器件在1 ×10<sup>6</sup> rad(Si) 的辐照后仍然保持较好的性能. 与条形栅器件相比, H 型栅器件唯一的不同之处在于消除了边缘寄生通道. 可见,制备器件所采用的氮化氧化合成栅技术的抗辐照性能在1 ×10<sup>6</sup> rad(Si) 以上,边缘漏电成为限制器件抗辐照性能的主要因素.

图 1 条形栅器件正栅(a)和背栅(b)辐照后的亚阈值特性

Fig. 1 Front (a) and back (b) gate subthreshold characteristics of traditional devices

图 2 H 型栅器件正栅(a)和背栅(b)辐照后的亚阈值特性

Fig. 2 Front (a) and back (b) gate subthreshold characteristics of H-type devices

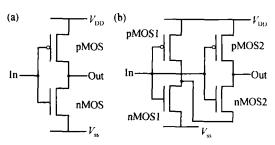

# 3 电路分析

在传统的 CMOS 反相器中,辐照将使 MOS-FET 的阈值电压向负方向漂移,并使 nMOSFET 漏电,这会导致两种结果:(1)由于阈值电压的变化,导致转变特性向负方向漂移;(2) nMOS 漏电过大会导致输出端"高"电平下降.对于阈值电压的变化,能够利用氮化氧化合成栅技术加以解决,本论文重点解决的是高电平下降的问题.

减小 nMOS 器件漏电流的一个方法就是提高 其源极电压,使源漏电压下降.在图 3(b) 所示的反 相器电路中,增加了一个上拉 pMOS(pMOS1),并 在 nMOS2 下面引入一个额外的 nMOS(nMOS1). 当输入电平为"高"时,pMOS1 将关闭,nMOS1 开 启,则原始的反相器工作不受影响. nMOS1 和 nMOS2 处于串连状态.新的反相器电路比传统电路 要慢一些,但可以通过增大 nMOS 的尺寸解决速度 问题. 当输入电平为"低"时,pMOS1 起到上拉作用,使pMOS1 和 nMOS1 的漏端连接点处于"高"电平.因此,nMOS2 能够更有效地关闭,其源漏电压很小,降低了漏电流,从而有效地提高输出端"高"电平,使其在 nMOS 经辐照漏电后,仍能保持在  $V_{tot}$ 附近.

图 3 传统反相器(a)和抗辐照反相器(b)电路图

Fig. 3 Traditional (a) and radiation hardened (b) inverters

# 结果与讨论

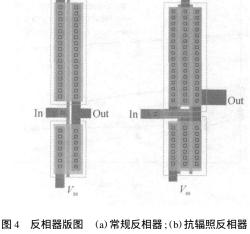

为了验证这种设计的有效性,制备了传统的反 相器和图 3(b) 所示的反相器. pMOS 和 nMOS 采用 条形栅器件,pMOS的宽长比为 40µm/1.2µm, nMOS 的宽长比为 20µm/1. 2µm, 版图如图 4 所示. 辐照过程中,样品的背栅和 Vss 端接地, VDD 端接 3V 电压,输入端接 3V 或 0V,输出端浮空,样品的全部 测试在停止辐照后 1h 内完成.

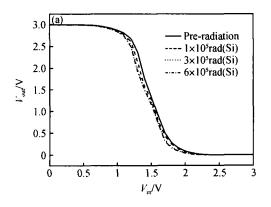

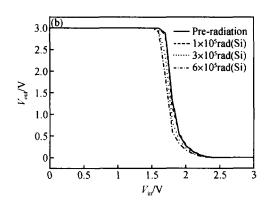

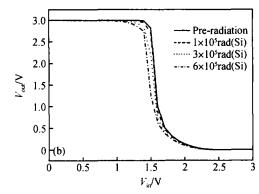

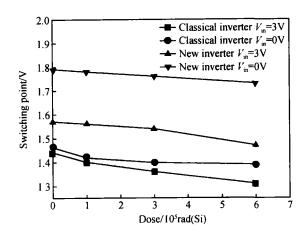

在辐照过程中输入端加 0V 电压时,不同剂量 辐照后的转变特性曲线如图 5 所示. 传统反相器和 新的反相器的输出"高"电平并未下降,只是整个曲 线向左漂移,转变电压分别下降了 0.07V 和 0.06V,如图 7 所示.在辐照过程中输入端加 3V 电 压时,转变特性曲线如图 6 所示. 经过剂量为 3 × 10<sup>5</sup> rad(Si)的辐照后,传统反相器的输出"高"电平 已经开始下降,当剂量增大到 6 ×10<sup>5</sup> rad(Si)时,降

Fig. 4 Layouts of traditional (a) and radiation hardened (b) inverters

幅达到 0.063V,转变电压下降 0.13V;而新的反相 器在 6 ×10<sup>5</sup> rad(Si)的辐照后,输出"高"电平未发生 任何下降,转变电压下降0.1V.

转变特性曲线(Vin=0V) (a)常规反相器;(b)抗辐照反相器

Transfer characteristics of traditional (a) and radiation hardened (b) inverters ( $V_{in} = 0V$ )

图 6 转变特性曲线(Vin = 3V) (a)常规反相器;(b)抗辐照反相器

Fig. 6 Transfer characteristics of traditional (a) and radiation hardened (b) inverters ( $V_{in} = 3V$ )

图 7 反相器的转变电压与总剂量的关系

Fig. 7 Transfer voltage as a function of dose

由以上结果可见,新的反相器电路在"高"电平的保持方面比传统反相器更加优秀,有更好的抗辐照性能.辐照过程中输入端加 3V 电压,对反相器的损伤明显更大.这主要是因为栅极加高电压时,nMOS开启,pMOS关闭,都处于最劣辐照条件;而栅极加 0V 时,nMOS关闭,pMOS开启,辐照对晶体管的影响较小.两种结构反相器的转变电压的变化基本一致,如图 7 所示,这主要是因为反相器的转变电压是与 nMOS 和 pMOS 的阈值电压相关的.而本研究中晶体管使用的是氮化氧化合成栅介质,能够承受较高的辐照剂量,因此晶体管的阈值电压变化不大并保持一致.

# 5 结论

制备了一种新型的抗辐照反相器,与常规反相

器相比,增加了一个上拉 pMOS,并引入了一个额外的 nMOS. 该反相器电路在输出"高"电平的保持方面比传统反相器更加优秀,在 6 ×10<sup>5</sup> rad(Si)的辐照后输出"高"电平未发生任何下降.

#### 参考文献

- [1] Liu Xinyu, Liu Yunlong, Sun Haifeng, et al. Characteristics on total-dose radiation hardeness for CMOS/SOI 4Kb SRAM. Chinese Journal of Semiconductors, 2002, 23(2):213(in Chinese)[刘新宇,刘运龙,孙海峰,等. CMOS/SOI 4Kb SRAM 总剂量辐照实验.半导体学报, 2002, 23(2):213]

- [2] Zhao Hongchen, Hai Chaohe, Han Zhengsheng, et al. Radiation of SOI MOSFET with shallow source. Chinese Journal of Semiconductors, 2004, 25(6):735 (in Chinese) [赵洪辰,海潮和,韩郑生,等. 源区浅结 SOI MOSFET 的辐照效应模拟. 半导体学报, 2004, 25(6):735]

- [ 3 ] Leray J L ,Dupont-Nivet E ,Pere J L . CMOS/ SOI hardening at 100 Mrad(SiO<sub>2</sub>) . IEEE Trans Nucl Sci ,1990 ,37 :2013

- [4] Lo GQ Joshi AB, Kwong DL. Radiation hardeness of MOS-FET's with N<sub>2</sub>O-nitrided gate oxides. IEEE Trans Electron Devices, 1993, 40:1565

- [5] Ohno T, Takahasi M, Ohtaka A. Suppression of the parasitic bipolar effect in ultra-thin-film nMOSFET 's/SIMOX by Ar implantation into source/drain regions. IEDM Tech Dig, 1995:627

- [6] Yoshimi M, Terauchi M, Murakoshi A. Technology trends of silicomor-insulator—its advantages and problems to be solved. IEDM Tech Dig, 1994:429

- [7] Shreedhara J K, Barnaby H L, Bhuva B L. Circuit technique for threshold voltage stabilization using substrate bias in total dose environments. IEEE Trans Nucl Sci, 2000, 47:2557

#### A Radiation Hardened SOI Inverter

Zhao Hongchen<sup>1</sup>, Hai Chaohe<sup>1</sup>, Han Zhengsheng<sup>1</sup>, Qian He<sup>1</sup>, and Si Hong<sup>2</sup>

(1 Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China)

(2 Central Iron and Steel Research Institute, Beijing 100081, China)

**Abstract:** A radiation hardened SOI inverter with an additional pMOS1 and a nMOS1 is fabricated. When the inverter is irradiated, the source-drain voltage of nMOS in the inverter will be reduced by the high output voltage of pMOS1 and nMOS1. As a result, the leakage current decreases and the "high "output voltage will be maintained. After a radiation of 6 ×10<sup>5</sup> rad(Si), the output voltage does not decrease.

Key words: radiation; inverter; output voltage

**EEACC:** 2570D; 2570F

**Article ID**: 0253-4177 (2005) 09-1829-04