# A Linear CMOS OTA and Its Application to a 3. 3 V 20M Hz High- Q $g_m$ - C Bandpass Filter $^*$

## Wang Bin and Yang Huazhong

(Department of Electronic Engineering, Tsinghua University, Beijing 100084, China)

Abstract: A design of a linear and fully-balanced operational transconductance amplifier (OTA) with improved high DC gain and wide bandwidth is presented. Derivative from a single common source field effect transistor (FET) cascade and its DC FV characteristics, the third-order coefficient  $g_3$  has been well compensated with a parallel FET operated in the triode region, which has ever-odd symmetries between the boundary of the saturation and triode region. Therefore, for high linearity, a simple solution is obtained to increase input signal amplitude in saturation for the application of OTA continuous-time filters. A negative resistance load (NRL) technique is used for the compensation of parasitic output resistance and an achievement of a high DC-gain of the OTA circuits without extra internal nodes. Additionally, derivations from the ideal - 90 °phase of the  $g_m$ -C integrator mainly due to a finite DC gain and parasitic poles will be avoided in the frequency range of interest. HSPICE simulation shows that the total harmonic distortion at  $1V_{\rm pp}$  is less than 1% from a single 3. 3V supply. As an application of the VHF CMOS OTA, a second-order OTA-C bandpass filter is fabricated using a 0. 18µm CMOS process with two kinds of gate-oxide layers, which has achieved a center frequency of 20MHz, a 3dB-bandwidth of 180kHz, and a quality factor of 110.

**Key words:** linear OTA; high DC-gain; high Q; bandpass filter

**EEACC:** 1270E: 2570D

#### 1 Introduction

In recent years, development of sophisticated analog and digital circuits fabricated on a single chip has resulted in the implementation of a single-chip mixed analog/digital system. Active filters have been implemented with various degrees of integration. Many design techniques have been proposed for realizing monolithic continuous-time filters. For high-frequency application, the transconductance-capacitor ( $g_m$ -C) approach is well-known where the basic block is a continuous-time integra-

tor. Excess phase shifts in the integrator will have great influence on the frequency response of high-frequency filters. A linearized operational transconductance amplifier (OTA) cell is designed and optimized for integrator phase error cancellation<sup>[1-5]</sup>.

In order to achieve high output resistance and to increase the voltage gain of the OTA, a negative conductance is used to cancel its positive output conductance, which can also compensate for the loss introduced by the finite output impedance of the OTA implemented in the continuous-time filter, thus the quality factor (Q) is increased. Negative resistance load (NRL) realized high-gain OTA

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (Nos. 90207001, 90307016) and the National High Technology Research and Development Program of China (No. 2003AA1Z1390)

Wang Bin female, graduate student. Her research interest is mainly on continuous-time filter design.

Yang Huazhong male ,professor. His research interest is mainly on low power system structure and circuit design ,digital information processing chip design ,and CMOS integrated circuits design and verification.

with large gain bandwidth-products (GBW) and avoided excess phase shifts from ideal - 90° phase of the integrator<sup>16~81</sup>. Compared with other commonly used gain enhancement techniques, NRL has fewer poles and consumes less power. In this paper, a simple OTA has been proposed with enhanced DC gain and improved linearity.

## 2 High-gain OTA with NRL

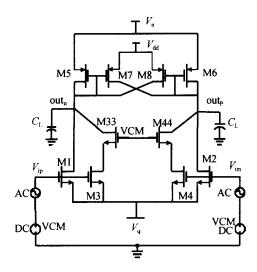

The design of analog signal processing systems is increasingly based on OTAs because of their fast speed in comparison with conventional low output impedance operational amplifiers (Op Amp), and their bias dependence transconductance tenability. However, the range of linear operation of OTAs has been restricted seriously, and has been investigated in the literature for several decades [9,10]. In this paper we combine a novel technique proposed in Refs. [11,12] to linearize the input differential pair with NRL to reduce non-zero integrator phase shift due to the internal low impedance and parasitic capacitance of the OTA. Figure 1 shows the proposed OTA which consists of a negative resistance load (M5, M6, M7, M8) and a differential transconductance cell (M1, M2, M3, M4, M33, M44) that is firstly proposed by Youn et al. [12] to improve the linearity of low noise amplifiers. The nonlinearity of a circuit mainly comes from the nonlinearity of MOSFETs which can be characterized by Taylor expansion in the range of interest:

$y(t) = g_1 x(t) + g_2 x^2(t) + g_3 x^3(t) + \dots$  (1) where x(t) and y(t) are the input voltage  $V_{\rm gs}$  and channel current  $I_{\rm ds}$  of MOSFETs, respectively. For small  $x, y(t) = g_1 x$ , indicating that  $g_1$  can be the small signal gain.  $g_2$ ,  $g_3$  are the successive derivatives of DC FV characteristics. The third-order coefficient  $g_3$  is the major source of the harmonic distortion of differential OTAs because the differential structure cancels out all the even order harmonics. M33 and M44 play the roles of eliminating  $g_3$ .

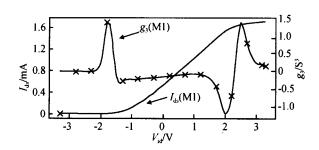

Figure 2 shows the output drain-source cur-

Fig. 1 Proposed OTA with NRL

rent and its 3rd-order coefficient  $g_3$  of the simple cascade circuit. The MOSFET FV curve (Fig. 2) shows asymmetry in the saturation and triode region of the 3rd-order derivative. According to this characteristic of the cascade circuit, we can add a MOSFET working in the triode region to cancel out the nonlinearity of the original MOSFET. For realization, a branch circuit (M3 and M33) parallel with MOSFET M1 is used to compensate the nonlinearity of the original cascade circuit, where M33 is operated in the saturation region and M3 is operated in the triode region when the amplitude of the input signal is small. M2, M44, and M4 are matched to M1, M33, and M3, respectively.

Fig. 2 M1 FV DC curve and its 3rd-order derivative

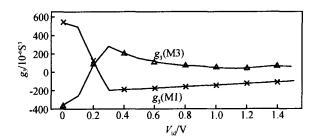

Figure 3 shows the three-order derivative of M1 and M3 respectively, where M1 firstly comes into the saturation region and then M3 follows M1 into the saturation region. However, when the input signal is large, M3 enters the triode region and

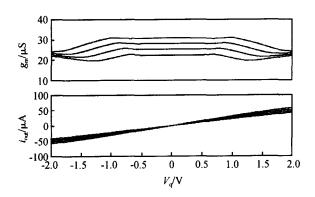

M1 is still in the saturation region. At the vicinity of the common mode input voltage (CMIV), the 3rd-order derivatives of M1 and M3 can cancel out each other ,therefore the linearity of the OTA has been improved with a decreased 3rd-order derivative. Figure 4 shows the transconductance ( $g_m$ ) simulation result of the linearized OTA with NRL. As  $V_q$  varies from 0 to 0.3V,  $g_m$  adjustment in range from 30.8 to 22.2 $\mu$ s is obtained for single power supply of 3.3V.

Fig. 3 3rd-order derivatives of M1 and M3

Fig. 4 OTA output currents and  $g_m$  at different  $V_q$

An ideal transconductance amplifier is an infinite bandwidth voltage controlled current source with an infinite input and output impedance. However, the output impedance of a real  $g_m$  cell is always finite and the real  $g_m$  cell is then a two-pole system and the dominant pole is no longer at zero. Meanwhile, a non-zero integrator phase shift caused by internal low impedance and parasitic capacitance will make the actual frequency response deviate from the ideal case, especially for high-Q system which will become unstable in the extreme case if the excess phase shift is not reduced. Re-

cently, a number of researchers have investigated techniques based on the negative resistance  $load^{[13,14]}$ . We can represent the building block circuit of Fig. 1 with its small-signal macro-model including parasitic output resistance  $R_p$  in parallel with a negative resistance  $R_n$ , which is shown in Fig. 5. From the macro-model, we can obtain the transfer function of the OTA,

$$A(s) = \frac{V_{\text{out}}}{V_{\text{in}}} = -\frac{g_{\text{m}}}{\frac{1}{R_{\text{p}}} + \frac{1}{R_{\text{n}}} + s(C_{\text{l}} + C_{\text{p}})}$$

(2)

where  $C_1$ ,  $C_p$  are the load capacitor and parasitic capacitor, respectively,  $R_n$ ,  $R_p$  will be described in the following description.

$$V_{\rm in} = \left( \begin{array}{c} V_{\rm in} \\ V_{\rm in} \end{array} \right) \left( \begin{array}{c} V_{\rm in} \\ V_{\rm in} \end{array} \right) \left( \begin{array}{c} V_{\rm in} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \right) \left( \begin{array}{c} V_{\rm out} \\ V_{\rm out} \end{array} \right) \left( \begin{array}{c} V_$$

Fig. 5 Small signal equivalent circuit of Fig. 1

Using the standard square-law model of MOS devices in the NRL subcircuit of Fig. 1, the differential output current can be described as

$$i_{\text{out}} = I_{\text{outn}} - I_{\text{outp}} = -2 k_{\text{p}} (V_{\text{dd}} - V_{\text{a}}) (V_{\text{outp}} - V_{\text{outn}})$$

where  $k_p = 0.5 \mu_p C_{ox} W/L$  is the OTA parameter.

Then the output equivalent transconductance is

$$g_{\rm mn} = \frac{\partial i_{\rm out}}{\partial V_{\rm out}} = -2 k_{\rm p} (V_{\rm dd} - V_{\rm a}) \tag{4}$$

Thus, the negative resistance  $R_N$  can be written as

$$R_{\rm N} = 1/g_{\rm mn} = -1/2 k_{\rm p} (V_{\rm dd} - V_{\rm a}) = -\frac{1}{g_{\rm m8} - g_{\rm m5}}$$

(5)

where  $g_{m8}$ ,  $g_{m5}$  are the tranconductances of M8 and M5, respectively. If at the output terminal the sum of output resistances is close to the negative resistance, theoretically infinite output resistance and voltage gain will be obtained. From the circuit of Fig. 1, output transconductance approaches the sum of M1, M33, M5, and M8, when all of the four MOSFETs work in the saturation region where M3 works in the triode region. Thus the output conductance of the OTA can be approximated as,

$$R_{\rm p} = 1/g_{\rm ds} = \frac{1}{g_{\rm ds1} + g_{\rm ds33} + g_{\rm ds5} + g_{\rm ds8}}$$

(6)

From Eq. (2) ,we can obtain infinite DC gain of the OTA under the condition  $R_p = -R_n$ . However, if  $R_p < R_n$ , the system will be unstable due to a right-half-plane pole, known as "overcompensated". From Eqs. (4) and (5), the unstable state can be avoided if and only if the following inequation holds.

$$V_{\rm a} = V_{\rm dd} - \frac{1}{2k_{\rm B}R_{\rm B}} \tag{7}$$

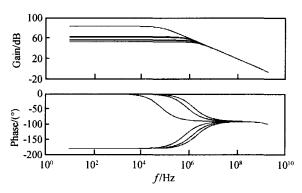

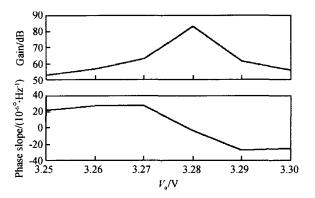

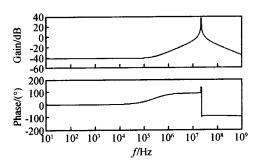

Figure 6 shows the AC response of the proposed OTA circuit with sweeping  $V_a$  voltage from 3. 25 to 3. 3V. For simplicity, gain and phase slope curves versus different  $V_a$  voltages are shown in Fig. 7. According to Eqs. (4) and (7), the negative transconductance has a direct proportion nexus with the difference between supply voltage  $V_{\rm dd}$  and  $V_a$ ; the result plot shown in Fig. 7 is a bilateral symmetry curve at  $V_a = 3$ . 28V. When  $V_a > 3$ . 28V, the system will remain stable due to the negative phase slope<sup>[15]</sup>. HSPICE simulation shows the output resistance is 171M and gain is 83dB at CMIV = 1. 65V and  $V_a = 3$ . 28V.

Fig. 6 OTA output gain and phase with NRL

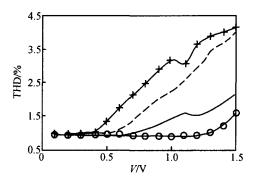

The simulated total harmonic distortion (THD) for the proposed circuit of Fig. 1 is depicted in Fig. 8. HSPICE simulation shows that the THD is less than 1 % when the input voltage ranges within  $1V_{\rm FP}$  and CMIV ranges from 1. 65V to 2. 65V. The marker diamond real line dashed line, and marker plus sign represent THD curves at

CMIV of 1. 65, 2, 2. 35, and 2. 65, respectively.

Fig. 7 OTA output gain and phase slope versus different  $V_a$

Fig. 8 OTA total harmonic distortion for different VCM

## 3 High Q bandpass filter design

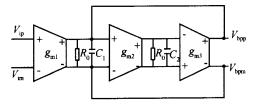

Figure 9 shows the structure of a single biquad bandpass filter while OTA  $g_{\rm m2}$  and  $g_{\rm m3}$  implement an active gyrator and  $g_{\rm m1}$ ,  $C_{\rm l}$  and  $C_{\rm 2}$  form an integrator<sup>[16]</sup>. The equivalent inductance  $L_{\rm eq}$  of gyrator is given by

$$L_{\rm eq} = \frac{C_2}{g_{\rm m2} g_{\rm m3}} \tag{8}$$

and the center frequency o is given by

$$_{0} = \frac{1}{\sqrt{LC}} = \sqrt{\frac{g_{m2} g_{m3}}{C_{1} C_{2}}}$$

(9)

An approach to compensate the finite output impedance of OTA is to parallel a negative  $g_m$  cell with the  $g_m$  cell. The resulted output impedance is

$$R_0 = \frac{1}{g_{0i} - g_{m-}} \tag{10}$$

where  $g_{0i}$  is the output impedance of the  $\dot{r}$ th OTA,  $g_{\rm m}$  is the output impedance of the negative  $g_{\rm m}$  cell itself. For high Q application, the transfer function can be approximated as

$$H(s) = \frac{V_{\text{bp}}}{V_{\text{in}}} = \frac{sg_{\text{ml}} C_{\text{l}}}{s^2 + s/C_{\text{l}} R_0 + g_{\text{m2}} g_{\text{m3}}/C_{\text{l}} C_2}$$

(11)

Q value is

$$Q = \frac{0}{BW} = 0 C_1 R_0 = g_{m2,3} R_0$$

(12)

Figure 10 shows the HSPICE simulated amplitude-frequency and phase-frequency response of the bandpass filter implemented by the proposed linear OTA with NRL. The simulation was performed at 20MHz center frequency and quality factor was 110 where  $C_1$ ,  $C_2$  are equal to 0. 29pF.

Fig. 9 Biquad bandpass filter

Fig. 10 Biquad bandpass implementing negative resistance load OTA

### 4 Conclusion

This paper has presented the design and implementation of the high-gain linear OTA which can operate at a very high frequency and low power supply voltage. The resulting bandpass filter exhibits a high-Q, large voltage gain, and good linearity at the several tens MHz region.

#### References

- [1] Jaime E. Introduction to the design of transconductor-capacitor filters. Boston: Kluwer Academic Publishers, 1992

- [ 2 ] Schaumann R ,Van Valkenberg M E. Design of analog filters.

Oxford:Oxford University Press ,2001

- [ 3 ] Nauta B. A CMOS transconductance C filter technique for very high frequencies. IEEE J Solid State Circuits, 1992, 27

(2):142

- [4] Steyaert M S J ,Sansen W. A 10. 7-MHz 68dB SNR CMOS continuous-time filter with on-chip automatic tuning. IEEE J Solid-State Circuits ,1992 ,27(12):1843

- [5] Khorrambadi H, Gray P R. High-frequency continuous-time filters. IEEE J Solid-State Circuits, 1984, 19(6):939

- [6] Karsilayan A I, Achaumann R. Mixed-mode automatic tuning scheme for high-Q continuous time filters. IEEE Circuits, Devices and Systems Proceedings, 2000, 147(1):57

- [7] Hori S, Maeda T, Yano H, et al. A widely tunable CMOS Gm-C filter with a negative source degeneration resistor transoc-ndurctor. Proceedings of 29th European Solid-State Circuits, 2003:449

- [8] Manetakis K, Toumazou C. A 50MHz high Q bandpass CM-OS filter. IEEE Circuits and Systems International Symposium, 1997:309

- [ 9 ] Krummenacher F, Joehl N. A 4MHz CMOS continuous time filter with on chip automatic tuning. IEEE J Solid-State Circuits 1988, 23(3):750

- [10] Chen Mingdeng, Silva-Martinez J, Rokhsaz S, et al. A 2-Vpp 80-200MHz fourth-order continuous-time linear phase filter with automatic frequency tuning. IEEE J Solid-State Circuits, 2003, 38(10):1745

- [11] Cao Ke, Yang H Z, Wang H, et al. Design of low-voltage low noise amplifiers with high linearity. Chinese Journal of Semi-conductors, 2004, 25(11):1364(in Chinese)[曹克,杨华中,汪蕙,等.高线性低电压低噪声放大器设计.半导体学报,2004,25(11):1364]

- [12] Youn Y S, Chang J Hg, Koh KJn, et al. A 2 GHz 16dBm IIP3 low noise amplifier in 0. 25µm CMOS technology. IEEE J Solid-State Circuits, 2003, 38(1):452

- [13] Jie Yan, Geiger R L. A negative conductance voltage gain enhancement technique for low voltage high speed CMOS Op-Amp design. Proceedings of 43rd IEEE Midwest Symposium, 2000, 1:502

- [14] Szczepanski S. VHF fully-differential linearized CMOS transconductance element and its applications. IEEE International Symposium on Circuits and Systems, 1994, 5:97

- [15] Nauta B. Analog CMOS filters for very high frequencies. Boston: Kluwer Academic Publishers, 1993

- [16] Liu Hengsheng, Aydin I. A high frequency bandpass continuous-time filter with automatic frequency and Q-factor tuning. IEEE International Symposium on Circuits and Systems, 2001,1:328

## 应用于高 Q 跨导-电容带通滤波器的线性跨导运放设计

### 王 斌 杨华中

(清华大学电子工程系,北京 100084)

关键词:线性跨导运放;高直流增益;高品质因数;带通滤波器

**EEACC:** 1270E; 2570D

中图分类号: TN432 文献标识码: A 文章编号: 0253-4177 (2005) 10-1892-06

<sup>\*</sup>国家自然科学基金(批准号:90207001,90307016),国家高技术研究发展计划(批准号:2003AA1Z1390)资助项目

王 斌 女,硕士研究生,主要从事模拟滤波器电路设计. Email:w-b02 @mails.tsinghua.edu.cn