# 11 GHz CMOS 环形压控振荡器设计\*

### 王雪艳 朱 恩 熊明珍 王志功

(东南大学射频与光电集成电路研究所,南京 210096)

摘要:设计了一种全差分高速环形压控振荡器(VCO).该 VCO 有三级,每一级的增益是快慢通路增益的矢量叠加和,快慢通路的增益由底部电流源决定,差分控制电压通过镜像电流源控制快慢通路的各自电流,最终实现对振荡频率的调节.分析了 VCO 的工作原理及其相位噪声.电路采用 TSMC 公司 0.18µm 标准 CMOS 工艺制作.测试结果显示:芯片工作频率为 10.88~11.72 GHz,相位噪声为 - 101 dBc/ Hz @10 MHz,输出信号抖动为 3.8ps ms,在 1.8V 电源电压下的直流功耗约为 75mW.该 VCO 可以应用于锁相环和频率合成器中.

关键词:压控振荡器;相位噪声;射频电路

**EEACC:** 1230B

中图分类号: TN752 文献标识码: A 文章编号: 0253-4177(2005)01-0187-05

### 1 引言

压控振荡器被广泛应用于通信系统电路中,例 如锁相环、频率综合器以及时钟产生和时钟恢复电 路. 常见 VCO 的实现形式有 LC 振荡器和环形振荡 器.在 GHz 频段上 LC 振荡器的噪声性能优于环形 振荡器[1]. 在标准 CMOS 工艺中为了防止栓锁效应, 硅衬底多为高掺杂,而当频率达到 10GHz 以上时, 由于衬底的高掺杂,电感高频损失增加.主要表现为 导电率较低的电感在高频下产生的"趋肤效应"[2]和 "涡流效应" $^{[2]}$ 严重,使其自谐振频率和 o 值急剧下 降. 目前国内外已报道的研究成果中能达到 10 GHz 以上的多采用一些先进工艺,如 0.13µm CMOS, GaAs, GeSi<sup>[3]</sup>, Bipolar<sup>[4]</sup>,以及非标准的低掺杂衬底来 实现,但无法与现有 CMOS 工艺兼容,而现有 CMOS 工艺实现的电路速度又比较低[5~7]. 因此,采用低成 本、低功耗、易集成且易寻求代工服务的标准 CMOS 工艺设计高速通信集成电路,既是市场的需要,也是 研究的重点.

# 2 电路结构

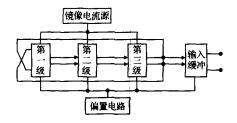

设计的 VCO 系统框图如图 1 所示,整个系统包括三级延迟、可控镜像电流源、两级输出缓冲和偏置电路.全部采用全差分、全对称的电路结构,级与级之间直接耦合.前一级输出缓冲用于增加 VCO 驱动负载电容的能力,后一级输出缓冲用于消除信号反射而造成的功率损耗,增加传输效率,实现 50 传输线匹配.两级输出缓冲均采用源级耦合差分对构成.偏置电路包括高值电阻分压结构和有源器件分压结构,分别用于控制输入端的内偏置和电路中的电流源偏置.

图1 VCO系统框图

Fig. 1 Voltage-control oscillator architecture

<sup>\*</sup>国家高技术研究发展计划资助项目(批准号:2001AA312060)

王雪艳 女,硕士研究生,主要从事万兆以太网和 SDH-64 专用高速集成电路设计.

朱 恩 男,教授,从事以太网和光纤倍讯系统专用集成电路的研究.

#### 3 电路原理

负反馈振荡器起振的必要条件是环路增益满足 下面两个条件:

$$/ H(\mathfrak{j}_{0}) / 1 \tag{1}$$

$$H(\mathfrak{j}_{0}) = 180^{\circ} \tag{2}$$

这些条件是必要非充分的. 为了使 VCO 在温度和工艺存在偏差情况下仍能起振,我们选择环路的增益至少是两到三倍. 考虑到级数较多不但增加面积且增加功耗,所以本设计选择三级. 根据公式(1)和(2)计算得出,三级环形 VCO 的每一级低频增益至少是  $2\sqrt{3}$  。频率信号的相移为 60  $\sqrt{3}$  。是振荡频率,。是每级差分放大对的 3dB 带宽).

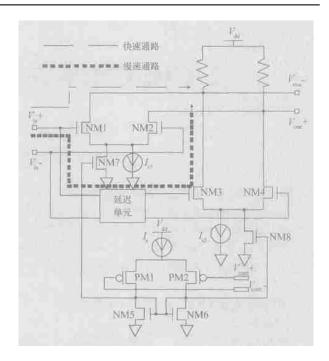

VCO 每级的框图如图 2 所示,它由快速通路和慢速通路组成,差分对 NM1,NM2 组成信号的快速通路,差分对 NM3,NM4 和延迟单元组成信号的慢速通路.输出信号是两通路的矢量叠加,Vcont调节两通路的增益.当快速通路开启,慢速通路关断时,振荡频率最高;而快速通路关断,慢速通路开启时,振荡频率最低;Vcont使快速通路和慢速通路同时开启时,振荡频率由两通路延迟的矢量和决定.慢速通路中插入的延迟单元为源级耦合的基本差分放大器,负载为 PMOS 管.延迟单元只是要求提供一定的延迟,因此可以牺牲一定的增益来减小输入电容,从而拓展 VCO 单级带宽.

VCO 每级增益的变化通过调节差分对 NM1, NM2 和差分对 NM3, NM4 底部电流源实现. 由于当 NM3, NM4 差分对增益为零时,慢速通路就完全关断,所以延迟单元不需要调节. 输出信号幅度恒定是我们所希望的. 假设差分对 NM1, NM2 和差分对 NM3, NM4 电流反向变化,电流和为定值,那么快慢通路的矢量叠加得到的输出信号的摆幅恒定. 为了实现电流和为定值,电路中使用了差分镜像电流源,与源级耦合差分对相比,它既避免了低电压时管子叠放对管子工作状态的影响,同时又增强了控制端与输出端的隔离,有利于抑制噪声,提高相位噪声. 镜像电流源中,我们选用 PMOS 差分对是考虑到 PMOS 管比 NMOS 管有较小的 1/f 噪声(闪烁噪声)和较小的噪声跨导. 对同样的噪声电压,跨导小的 PMOS 管输出的噪声电流小,引起的相位噪声小.

图 2 VCO 单级电路示意图 Fig. 2 One stage of VCO

### 4 相位噪声分析

VCO 的主要性能指标主要包括振荡频率、电压-频率转换的线性度、调谐范围、相位噪声、抖动和制 造成本,其中相位噪声和抖动最为关键,主要表现在 输出频率的波动,它直接影响定时的精度,降低了一 定信噪比情况下的信号传输的误码率,不能实现最 佳传输.相位和频率的波动因此成为国内外理论界 研究热点[8~10].建立了适用于各种振荡器的模型, 其中最主要的是线性时不变(LTI)模型和线性时变 (LTV)模型. 它们都详细解释了各种噪声源转化为 相位和幅度变化的机理,在相位噪声谱线的邻近载 频的  $1/f^3$  区主要受 1/f 噪声影响. 低频的 1/f 噪声 正是由于有源器件在关断过程中的非线性调制而影 响输出频谱的. 在  $1/f^2$  区主要受白噪声的影响. 在 不同的区域内我们重点优化关键噪声. 影响相位噪 声的主要因素除了噪声功率谱密度和功耗外,还有 脉冲敏感函数(ISF) . 通过优化输出波形的对称 性来减小.

噪声主要来源可以分为两组<sup>[11]</sup>,分别为器件噪声和外加干扰. 热噪声(thermal noise)、散弹噪声(shot noise)、闪烁噪声(flicker noise)属于器件噪声;电源噪声和衬底噪声(supply and substrate noise)属于外加干扰噪声.

1/f² 区的关键噪声白噪声 (white noise) 主要是热噪声. 热噪声包括电阻热噪声、有源管沟道热噪声和栅电阻热噪声. 公式(3)和(4)给出了沟道热噪声和栅热噪声的表达式:

$$I_{\rm nd}^2 = 4 \, k \, T \, g_{\rm d0} \, f \tag{3}$$

$$I_{\rm ng}^2 = 4 k T g_{\rm g} f \tag{4}$$

式中 ,是依赖管子偏置的系数,在饱和状态下与沟道长度成反比,短沟道中 一般为  $2 \sim 3$ , 约是 的 2 倍;  $g_{a0}$ 是漏端零偏置下的漏输出跨导;  $g_{g}$ 是栅到源导纳的实部. 由 (3) 式可知,减小跨导可以降低噪声. 作为恒流源的管子则可采用栅长较长的管子. 对于栅宽较大的管子可通过叉指型版图设计来减小栅电阻热噪声.

$1/f^3$  区的关键噪声 1/f 噪声,又称闪烁噪声,它的谱密度随频率的降低而增加. 公式(5)给出了有源器件的电流源模型:

$$\overline{I_n^2} = \frac{Kg_m^2}{C_{ox}WL} \times \frac{1}{f}$$

(5)

K是由工艺决定的参数. 工艺一定情况下,增大管子面积可以减小 1/f 噪声. 电流源适当选择大一点的管子. 一般认为 PMOS 比 NMOS 有更小的 1/f 噪声, 因为前者沟道中载流子为空穴 $^{(11)}$ . 前面提到选择 PMOS 为控制电路的电流源.

电源噪声和衬底噪声对相位噪声的影响不能忽略,与级数有关而与功耗无关.由于振荡器每一级都受到相同的干扰,呈现完全相关的噪声.在频率一定时,级数越多则电源噪声对相位噪声越多,一般选择三级.版图设计中注意完全对称原则,将有效抑制电源引入的共模噪声.尽量增大电源和地线之间的电容,可滤除电源耦合串扰.有源放大管衬底噪声可以看作是电源噪声的负变化,即衬底电压变化 · V 等效为电源电压变化 · V.

# 5 仿真和测试结果

本设计采用 TSMC 公司的 0.18µm CMOS 模型进行仿真,前仿真使用 Agilent ADS 高频设计工具,后仿真使用 Cadence 的 Spectre. 版图设计在 Cadence 环境中完成. 流片版图如图 3 所示,核心面积只有 0.2mm x0.2mm.

芯片测试在作者所在研究所完成,主要测试设备包括美国 Cascade Microtech 公司的微波速芯片测试台, CSCSG高频探针高析仪,美国 HP 公司的 22

图 3 VCO 芯片照片 Fig. 3 Chip die photograph

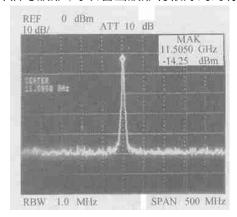

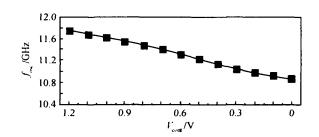

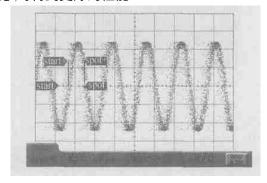

GHz 频谱分析仪和美国 Agilent 公司 86100A 系列数字通信分析仪.测试结果表明:芯片工作频率范围为  $10.88 \sim 11.72$  GHz,图 4为 VCO 在 11.5 GHz 时振荡频谱,在 10 MHz 频偏处(小于 1.66)测得单边带相位噪声约 - 101 dBc/Hz,控制电压在  $0 \sim 1.2$  V 变化,电压-频率转换系数  $K_{VCO}$ 为 700 MHz/V;图 5.5 显示振荡器的电压-频率转换具有很好的线性度;图 6.6 给出输出时钟信号波形,可以看出波形有很好的对称性,实

图 4 VCO 振荡频谱图 Fig. 4 VCO output spectrum

图 5 压控特性曲线 Fig. 5 Voltage control-frequency curve

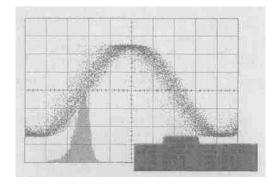

测占空比为 48 %,输出信号峰-峰值为 120mV;图 7中显示信号抖动为 3.8ps rms.整个芯片以 1.8V 电源电压供电,功耗为 75mW.由于输出缓冲带宽的限制,输出信号幅度峰-峰值较小,信号经过输出缓冲后信噪比下降,若采用电感补偿技术拓展输出缓冲带宽,可得到更好的性能.

图 6 输出时钟信号波形 Fig. 6 Measured VCO output in time domain

图 7 抖动的柱状图 Fig. 7 Jitter of output

# 6 结论

基于 0.18µm 标准 CMOS 工艺,设计完成了工作速度达到 11 GHz 的环形 VCO,比现有设计的工作速度提高了 4~6 倍.通过对各种噪声的分析以及电路本身对噪声敏感度分析,综合优化电路参数.测试结果显示该 VCO 的压控特性线性度好,输出波形基本对称,调频范围适中,相位噪声低于文献[6]中的

- 80dBc/ Hz @5MHz,满足通信系统的一般要求. 可根据需要调整部分参数集成到锁相环中,用于万兆以太网、STM-64 和 OC-192 的时钟产生和时钟恢复电路中.

#### 参考文献

- [1] Chi Baoyong ,Shi Bingxue. A 2.4 GHz CMOS quadrature voltage-controlled oscilla based on symmetrical spiral inductors and differential diodes. Chinese Journal of Semiconductors ,2002 ,23(2):131 (in Chinese) [池保勇 ,石秉学. 基于对称螺旋型电感和差分二极管的2.4 GHz CMOS 正交输出压控振荡器. 半导体学报 ,2002 ,23(2):

- [ 2 ] Lee T.H. The Design of CMOS radio-frequency integrated circuits.

Cambirdge: Press of the University of Cambirdge, 1998

- [ 3 ] Greshishchev Y M, Schvan P. Si Ge clock and data recovery IC with line type PLL for 10 Gb/s SONET application. Proc 1999 Bipolar/ BiCMOS Circuits and Technology Meeting, 1999:169

- [4] Wurzer M, et al. 40- Gb/s integtated clock and data recovery circuit in a silion bipolar technology. Proc 1999 Bipolar/BiCMOS Circuits and Technology Meeting, 1998:136

- [ 5 ] Razavi B. A 3-GHz 25-mW CMOS phase-lock loop. IEEE Symposium on VLSI Circuits Digest of Technical Papers, 1994:131

- [ 6 ] Anand B A ,Razaiv B. A CMOS clock recovery circuit for 2.5-Gb/s NRZ data. IEEE J Solid-State Circuits ,2001 ,36(3) :432

- [7] Wang Zhao ,Liu Fei Ji Lijiu. A novel dual-path current-mode voltage controlled oscillator. Chinese Journal of Semiconductors ,2002 ,23(3): 305(in Chinese) [王钊,刘飞,吉利久. 新型双环路电流型压控振荡器. 半导体学报 ,2002 ,23(3):305]

- [8] Hajimiri A ,Lee T H. General theory of phase noise in electrical oscillators. IEEE J Solid-State Circuits ,1998 ,33:179

- [ 9 ] Razavi B. A study of phase noise in CMOS oscillators. IEEE J Solid-State Circuits ,1996 ,31:331

- [10] Hajimiri A ,Limotyrakis S ,Lee T H.Jitter and phase noise in ring oscillators. IEEE J Solid-State Ctruits ,1999 ,34(6):790

- [11] Razavi B. Design of analog CMOS integrated circuits. New York: Mc-Graw-Hill Companies, 2000

# Design of 11 GHz CMOS Ring VCO \*

Wang Xueyan, Zhu En, Xiong Mingzhen, and Wang Zhigong

(Institute of RF- & OE-ICs, Southeast University, Nanjing 210096, China)

**Abstract :** A full integrated high speed ring VCO is designed. The VCO consists of three stages and each consists of a fast path and a slow path whose output are summed and whose gains are adjusted by tail currents. The tail currents of fast and slow paths are controlled by the control voltage through current mirrors. The VCO is realized in 0.18µm standard CMOS process. Measurements show that the operating frequency covers 10.88 ~ 11.72 GHz. The phase noise is - 101 dBc/ Hz @10MHz and jitter is about 3.8ps rm. The power consumption is about 75mW at a supply voltage of 1.8V. Potential applications include PLLs and frequency synthesizers.

Key words: VCO; phase noise; RFIC

**EEACC:** 1230B

**Article ID**: 0253-4177 (2005) 01-0187-05

<sup>\*</sup> Project supported by National High Technology Research and Development Program of China (No. 2001AA312060)