## RTD 与 PHEMT 集成的几个关键工艺 <sup>1</sup>

## 王建林 $^1$ 刘忠立 $^1$ 王良臣 $^2$ 曾一平 $^3$ 杨富华 $^4$ 白云霞 $^2$

- (1 中国科学院半导体研究所 微电子研发中心, 北京 100083)

- (2 中国科学院半导体研究所 光电子研发中心, 北京 100083)

- (3 中国科学院半导体研究所 新材料部, 北京 100083)

(4 中国科学院半导体研究所 超晶格与微结构国家重点实验室, 北京 100083)

摘要:在新型的共振隧穿二极管 (RTD) 器件与 PHEMT 器件单片集成材料结构上,研究和分析了分立器件的制作工艺,给出了分立器件的制作工艺参数. 利用上述工艺成功制作了 RTD 和 PHEMT 器件,并在室温下分别测试了 RTD 器件和 PHEMT 器件的电学特性. 测试表明:在室温下,RTD 器件的峰电流密度与谷电流密度之比提高到 1.78; PHEMT 器件的最大跨导约为  $120\,\mathrm{mS}/\mathrm{mm}$ ,在  $V_\mathrm{gs}=0.5\mathrm{V}$  时的饱和电流约为  $270\,\mathrm{mA}/\mathrm{mm}$ . 这将为 RTD 集成电路的研制奠定工艺基础.

关键词:共振隧穿二极管;高电子迁移率晶体管;集成电路;工艺

**EEACC: 2550**

中图分类号: TN705 文献标识码: A 文章编号: 0253-4177(2005)02-0390-05

## 1 引言

共振隧穿二极管(RTD)是应用量子效应的一种新型纳米器件.它具有高速、低功耗、能实现特定逻辑功能、电路简单等优点<sup>[1,2]</sup>.目前,RTD集成电路是纳米器件集成电路的研究热点,人们已经研究了 InP基 RTD与 HEMT的集成<sup>[3]</sup>,RTD与HBT的集成<sup>[4]</sup>和RTD与MESFET的集成<sup>[5]</sup>等.逻辑单元 MOBILE(monostable-bistable transition logic element)是RTD数字集成电路的核心部分<sup>[1,3]</sup>.我们选用RTD与PHEMT器件集成实现MOBILE逻辑功能.由于RTD器件与PHEMT器件的制作工艺相互影响,必须关注二者制作工艺的兼容问题.为此,在RTD与PHEMT单片集成材料结构上,本文系统地研究和分析了RTD器件和PHEMT器件的制作工艺,并给出了两种器件的电学性能,为实现RTD与PHEMT的集成奠定了工艺基础.

## 2 实验材料

图 1 给出了分子束外延生长所得到的 RTD 器件与 PHEMT 器件单片集成材料结构. 首先在 i-

GaAs 层上生长 PHEMT 材料结构,其组成为 In<sub>0.15</sub> Ga<sub>0.85</sub>As导电沟道,Al<sub>0.25</sub> Ga<sub>0.75</sub>As 隔离层,Si-掺杂电子供给层,Al<sub>0.25</sub> Ga<sub>0.75</sub>As 过渡层等.然后生长 RTD 材料结构,其核心部分是双势垒单势阱系统 AlAs/ GaAs/ In<sub>0.15</sub> Ga<sub>0.85</sub>As/ GaAs/ AlAs.

| n +- GaAs                                  | 3 ×10 <sup>18</sup> cm <sup>-3</sup> | 30nm    |

|--------------------------------------------|--------------------------------------|---------|

| Al <sub>0, 22</sub> Ga <sub>0, 78</sub> As |                                      | 150nm   |

| Al <sub>0, 22</sub> Ga <sub>0, 78</sub> As |                                      | 3nm     |

| In <sub>0. 15</sub> Ga <sub>0. 85</sub> As |                                      | 5nm     |

| GaAs                                       |                                      | 0.5nm   |

| AlAs                                       |                                      | 1.7nm   |

| GaAs                                       |                                      | 0.5nm   |

| In <sub>0. 15</sub> Ga <sub>0. 85</sub> As |                                      | 4nm     |

| GaAs                                       |                                      | 0.5nm   |

| AlAs                                       |                                      | 1.7nm   |

| GaAs                                       |                                      | 2.5nm   |

| n- GaAs                                    | $2 \times 10^{17} \text{cm}^{-3}$    | 10nm    |

| n +- GaAs                                  | 3 ×10 <sup>18</sup> cm <sup>-3</sup> | 100nm   |

| AlAs                                       |                                      | 2 ~ 4nm |

| Al <sub>0. 25</sub> Ga <sub>0. 75</sub> As |                                      | 25nm    |

| Si- 掺杂                                     | 3 ×10 <sup>12</sup> cm <sup>-2</sup> | 2 ~ 4nm |

| Al <sub>0, 25</sub> Ga <sub>0, 75</sub> As |                                      | 4nm     |

| In <sub>0. 15</sub> Ga <sub>0. 85</sub> As |                                      | 15nm    |

| Buffer GaAs                                |                                      |         |

| SI GaAs substrate                          |                                      |         |

图 1 RTD 与 PHEMT 单片集成的材料结构

Fig. 1 Material structure for integration of RTDs and PHEMTs

<sup>\*</sup>国家重点基础研究专项经费(批准号: C001CB3095)和中国科学院特别支持资助项目 王建林 男,1975年出生,博士研究生,主要从事 RTD 器件及集成电路的研究. 2004-02-19 收到,2004-04-26 定稿

## 3 分步工艺

在研究两种器件的制作工艺时,首先,湿法腐蚀得到所需的器件台面,然后分别研究 RTD 器件和PHEMT 器件的制作工艺.文中给出的测试数据均来自惠普 Keithley4200 半导体参数测试仪.

#### 3.1 RTD 器件上下电极欧姆接触的制作

欧姆接触是 RTD 器件工艺中最重要的组成部分,欧姆接触特性严重影响器件的量子效应.不同的 RTD 器件材料结构要求不同的欧姆接触制作工艺.整个欧姆接触工艺需要控制的条件是半导体表面、合金组分配比、合金层厚度、合金化温度和时间以及加热和冷却的速度等.目前,大多数 GaAs 器件选用 Au GeNi 合金制作欧姆接触.在图 1 所示的结构上,我们系统地研究了退火温度和退火时间对 RTD 器件性能的影响.

为了研究 RTD 器件的欧姆接触制作工艺,首先用传统的湿法腐蚀确定大尺寸的 RTD 器件台面,然后溅射  $5\,\mathrm{nm}$  Ni/  $100\,\mathrm{nm}$  Au Ge/  $200\,\mathrm{nm}$  Au 的金属层,用剥离工艺形成器件的上电极和下电极.在 N<sub>2</sub> H<sub>2</sub> = 2 1 的混合气氛中,改变退火温度和退火时间,研究 RTD 器件的  $I\!-\!V$  特性.图 2 是制作的 RTD 器件示意图.

图 2 用于确定 RTD 欧姆接触的结构示意图 Fig. 2 Schematic structure for investigating

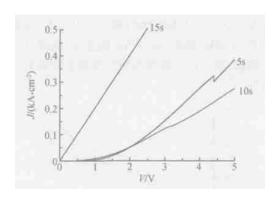

图 3 是在 400 及不同退火时间条件下,RTD 器件的 *J-V* 特性曲线. 从图 3 可以得知:在其他条件确定的情况下,退火时间为 5s 时出现负阻现象,但是欧姆接触的制作也是不理想的;选择 10s 的退火时间,器件的负阻现象消失,此时欧姆接触的制作是不理想的;然后再选择 15s 的退火时间,此时可形成欧姆接触. 因此,在 400 下,不改变其他条件,仅改变退火时间,是不能够同时得到负阻现象和良好欧姆特性的.

根据扩散理论,我们降低退火温度,增加退火时

图 3 在 400 ,不同退火条件下 RTD 器件的 J-V 曲线 Fig. 3 J-V curves for RTDs under different annealing times at 400

间,以期减小 Ge 等金属的扩散深度和提高金属与半导体界面 Ge 的浓度,制作良好的欧姆接触.我们选用的温度是 370 ,然后改变退火时间,研究器件的电特性的变化.所得实验结果如图 4 所示.

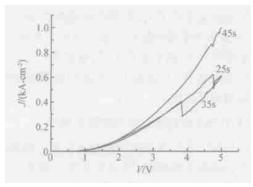

图 4 在 370 ,不同时间条件下退火制作的 RTD 器件 J-V 曲 线图

从图 4 可以得知:在其他条件确定的情况下,退火时间从 25s 变化到 45s,都可以看到器件负阻现象,但是所有的欧姆接触都是不理想的;退火时间为 35s 时,器件的负阻现象最明显,此时峰电流密度约为 0.40kA/cm²,谷电流密度约为 0.28kA/cm²,峰谷比为 1.4,共振电压约为 3.8V;当退火时间为 45s时,负阻现象几乎消失.因此,在 370 温度下,不改变其他条件,仅改变退火时间,是不能够同时得到负阻现象和良好的欧姆特性的.

把退火温度提高到 380 ,来研究不同退火时间下器件的电学特性,所得到的结果如图 5 所示.从图 5 可以得知:在其他条件确定的情况下,退火时间为 15s 时,器件具有良好的欧姆特性,同时具有明显的负阻现象,此时峰电流密度约为 0.54kA/cm²,谷

电流密度约为 0.43 kA/ cm², 峰谷比为 1.26, 共振电压约为 1.38 V. 因此,在 380 温度下,选择 15 s 的退火时间,器件可以同时得到负阻现象和良好的欧姆特性.

图 5 在 380 ,不同时间条件下退火制作的 RTD 器件 J-V 曲线 Fig. 5 J-V curves for RTDs under different annealing times at 380

上述研究表明了 RTD 器件欧姆制作的工艺为 RTD 集成电路的研制提供了重要的工艺参数. 进一步缩小器件尺寸,改善其他工艺,有望在更小的电压下发生共振隧穿,并提高 RTD 器件的峰电流密度与谷电流密度之比.

#### 3.2 PHEMT器件源漏欧姆接触的制作

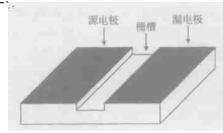

PHEMT 器件源漏欧姆接触的性能影响器件的跨导和器件的高频性能. 常用的接触金属是 Au-GeNi. 选用 5nm Ni/100nm Au Ge/200nm Au 的多层金属结构和厚度,同时在退火之前沉积 SiO<sub>2</sub>,以阻止退火时 As 的逸损和改善欧姆接触的电阻及形貌. 我们研究了不同退火温度、不同退火时间条件下制作的欧姆接触的电阻及形貌. 图 6 给出了示意测试图形.

图 6 示意测试图形

Fig. 6 Schematic testing image for Ohmic contact

在 400 温度下,分别选择不同的退火时间,观察欧姆接触的形貌可以发现,即使在 15s 的退火时间下表面仍然出现聚球现象,并且随退火时间增加,聚球现象更趋严重.为了获得良好的表面形貌,我们

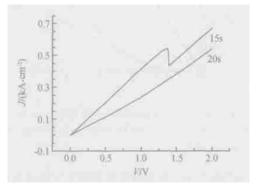

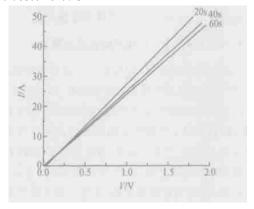

降低退火温度到 390 ,然后研究不同退火时间得到欧姆接触的电阻特性和表面形貌.在 20,40,60s 的退火时间下,所得的欧姆接触电学特性曲线基本相同(如图 7 所示),但是 60s 退火时间下欧姆接触的表面有聚球现象.

图 7 在 390 ,不同退火时间制作的欧姆接触的电学特性 Fig. 7 Electronics characteristics of ohmic contacts under different annealing times at 390

PHEMT 器件源漏的欧姆接触制作,既要求具有良好的欧姆特性,又要求合金到足够的深度.综合以上研究,选择如下工艺条件:退火温度 390 ,退火时间 40s.

#### 3.3 PHEMT栅的制作

由 PHEMT 的工作原理可知,栅条不能直接放在  $n^+$ - GaAs 上,因为这样栅的调制作用会被  $n^+$ - GaAs 屏蔽,无法达到调制沟道载流子的目的.因此,与栅对应的  $n^+$ - GaAs 必须腐蚀掉.实现办法是:在 25 条件下,用腐蚀液透过光刻胶形成的栅缝将暴露的  $n^+$ - GaAs 腐蚀掉,腐蚀液选用柠檬酸  $H_2O_2=7$  1(体积比).

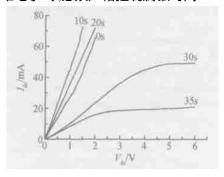

在腐蚀过程中,必须进行实时检测.测量如图 8 所示的结构的电流,图中标出了测试图形的各个区域.电流会随腐蚀时间增加而逐步减小,降到某一值时停止.

图 8 测试图形示意图

Fig. 8 Schematic testing image for ohmic contact

图 9 给出了栅槽为 4µm ×100µm 的源漏间 FV 测量曲线,从实验结果可知,对于 4µm ×100µm 栅槽来说,在腐蚀时间小于 20s 时,由于存在 n<sup>+</sup>- GaAs 层,测量的电流不饱和. 当腐蚀时间达到 30s 时,n<sup>+</sup>- GaAs 几乎被腐蚀干净,此时开始出现饱和电流现象. 然后轻微过腐蚀,以保证 n<sup>+</sup>- GaAs 被腐蚀干净,随着腐蚀时间的增加,电流饱和特性更好. 当饱和电流约为20mA 时,停止腐蚀.由此可见,为了能够比较准确地达到电流控制目的,不至于过腐蚀而伤及 掺杂层,破坏二维电子气,必须严格控制腐蚀时间.

图 9 刻蚀栅槽的源漏  $I_{ds}$   $V_{ds}$ 测量曲线

Fig. 9 Measured  $I_{ds}$ -  $V_{ds}$  curves for gate etching

#### 3.4 空气桥的制作

空气桥工艺在高速器件及集成电路互连线中得到广泛的应用. 空气桥具有寄生电容低,能消除边缘问题,可以通过大电流等优点. RTD 上电极引线采用空气桥工艺技术. 首先,通过光刻胶、曝光、显影打开金属桥墩窗口,溅射涂覆一薄层 CrAu 到整个片子上;其次涂覆第二次光刻胶,曝光、显影打开桥墩和桥面窗口,进行电镀;最后,再次涂覆光刻胶,曝光、显影,轻微腐蚀金属薄膜,并用有机溶剂去掉桥面下的光刻胶,形成空气桥,其形貌如图 10 所示.

图 10 采用空气桥技术制作的 RTD 器件 Fig. 10 RTD with air bridge

## 4 分立器件的实验结果

根据前面的工艺,在单片集成材料结构上,我们

分别制作了 RTD 和 PHEMT 器件. 下面给出分立器件的试验结果.

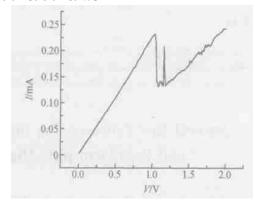

图 11 是采用空气桥技术制作 6 μm ×6 μm RTD 器件的 FV 特性曲线. 根据计算 ,RTD 器件的峰电流密度约为 0.64kA/cm²,谷电流密度约为 0.36kA/cm², 峰谷比为 1.78 ,共振电压约为 1.04V. 较小的峰电流密度 ,决定了 RTD 集成电路逻辑单元的最大工作电流比较小 ,有望实现极低功耗的集成电路. 另一方面,相对于不采用空气桥的大尺寸 RTD 器件 ,其峰谷比由 1.26 提高到 1.78. 另外 ,在图中 1.0~1.5V 之间存在一个尖峰 ,可能是由于器件在外加偏压作用下 ,发生低维到低维的隧穿[6].

图 11 室温下,6µm x6µm RTD 的 I-V 特性 Fig. 11 I-V curves of 6µm x6µm RTD at room temperature

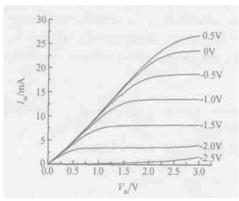

图 12 给出了  $1\mu m \times 100\mu m$  PHEMT 器件的电学特性.图 12 表明:根据前面的分立工艺在外延结构基础上成功制作了 PHEMT 器件. 室温下, PHEMT 器件阈值电压约为 - 2.5V ,最大跨导约为 120mS/mm,在  $V_{gs}=0.5V$  时的饱和电流约为 270mA/mm.

图 12 室温下  $,1\mu m \times 100\mu m$  PHEMT 器件的  $I_{ds}$   $V_{ds}$  曲线 Fig. 12  $I_{ds}$   $V_{ds}$  curves of  $1\mu m \times 100\mu m$  PHEMT at room temperature

### 5 结论

本文深入研究和分析了在新型的 RTD 与PHEMT单片集成材料结构上制作分立器件的工艺,确定了 RTD 电极的欧姆接触、RTD 上电极空气桥引线、PHEMT源漏电极的欧姆接触和 PHEMT栅电极等的制作工艺,给出了这些工艺的参数及实验结果. 利用这些工艺成功制作了 RTD 器件和PHEMT器件,同时给出了器件的电学特性. 这些工作有助于 RTD 与 PHEMT 的集成整合,为 RTD 集成电路的研制奠定了基础.

#### 参考文献

[1] Akeyoshi T, Matsuzaki H, Itoh T, et al. Application of resonant tunneling diodes to high-speed digital ICs. Eleventh International

- Conference on Indium Phosphide and Related Materials, 1999: 405

- [2] Mazumder P, Kulkarni S, Bhattacharya M, et al. Digital circuit applications of resonant tunneling devices. Proceedings of the IEEE, 1998, 86(4):664

- [ 3 ] Maezawa K,Osaka J, Yokoyama H, et al. Uniformity of the high electron mobility transistors and resonant tunneling diodes integrated on an InP substrate using an epitaxial structure grown by molecular beam epitaxy and metalorganic chemical vapour deposition. Jpn J Appl Phys, 1998, 37 (10):5500

- [4] Chen C Y, Wang W C, Chiou W H, et al. A comparative study of GaAs and InP-based superlattice emitter resonant tunneling bipolar transistors. Solid-State Electron, 2002, 46:1289

- [ 5 ] Chen K J ,Akeyoshi T ,Maezawa K. Monostable bistable transition logic elements (MOBILE) based on monolithic integration of resonant tunneling diodes and FETs. Jpn J Appl Phys ,1995 , 34(2)B:1199

- [6] Zhu Bangfen, Huang Kun. Self-consistent treatment of three-dimensional-two-dimensional and two-dimensional-two-dimensional resonant tunneling in double-barrier structures. Phys Rev B, 1993 48(7):4575

# Several Key Processes for Integration of Resonant Tunneling Diodes and Pseudomorphic High Electron Mobility Transistors \*

Wang Jianlin<sup>1</sup>, Liu Zhongli<sup>1</sup>, Wang Liangchen<sup>2</sup>, Zeng Yiping<sup>3</sup>, Yang Fuhua<sup>4</sup>, and Bai Yunxia<sup>2</sup>

- (1 Microelectronics R &D Center, Institute of Semiconductor, Chinese Academy of Sciences, Beijing 100083, China)

- (2 Optoelectronic R &D Center, Institute of Semiconductor, Chinese Academy of Sciences, Beijing 100083, China)

- (3 Novel Material Department, Institute of Semiconductor, Chinese Academy of Sciences, Beijing 100083, China)

$(4\ State\ Key\ Laboratory\ of\ Superlattices\ and\ Microstructures\ ,\ Institute\ of\ Semiconductors\ ,$

Chinese Academy of Sciences, Beijing 100083, China)

**Abstract:** Based on the new material structure for the integration of RTD devices and PHEMT devices, the fabrication processes of separate devices are systematically investigated and analyzed, and processes parameters are given. Besides, RTD devices and PHEMT devices according to these processes are fabricated successfully, and the electronics characteristics of fabricated RTD devices and PHEMT devices at room temperature are tested, respectively. These results show that the peak-to-valley current density ratio (PVCR) is increased to 1.78, the maximum transconductance is 120 mS/mm and saturated current at  $V_{gs} = 0.5$  is 270 mA/mm. The research will be helpful to establish the complete processes for integration of RTD devices and PHEMT devices.

Key words: resonant tunneling diodes; pseudomorphic high electron mobility transistors; integrated circuits; processes

**EEACC:** 2550

Article ID: 0253-4177 (2005) 02-0390-05

<sup>\*</sup> Project supported by the Special Funds of National Key Basic Research Plan of China (No. C001CB3095), the Special Project from Chinese Academy of Sciences