# Design and Fabrication of Schottky Diode with Standard CMOS Process \*

Li Qiang, Wang Junyu, Han Yifeng, and Min Hao

(State Key Laboratory of ASIC & System, Fudan University, Shanghai 200433, China)

**Abstract :** Design and fabrication of Schottky barrier diodes (SBD) with a commercial standard 0.35 $\mu$ m CMOS process are described. In order to reduce the series resistor of Schottky contact ,interdigitating the fingers of schottky diode layout is adopted. The *I*-*V*, *C*-*V*, and *S* parameter are measured. The parameters of realized SBD such as the saturation current, breakdown voltage ,and the Schottky barrier height are given. The SPICE simulation model of the realized SBDs is given.

**Key words :** CMOS; Schottky diode; integration **EEACC :** 2560H; 2570D **CLC number :** TN311<sup>+</sup>.7 **Document code :** A

### 1 Introduction

Schottky diodes have advantages such as fast switching speed and low forward voltage drop. Due to these excellent high frequency performance, they have been widely used in power detection and microwave network circuit<sup>[1]</sup>. Schottky diodes are often fabricated by depositing metals on n-type or p-type semiconductor materials such as GaAs and  $SiC^{[2 \sim 4]}$ . The properties of forward-biased Schottky diodes are determined by majority carrier, while minority carrier primarily determine those properties of p-n diodes. In order to improve high frequency performance and decrease supply voltage of IC, integrating the Schottky diode into modern IC is very important. But the process that can integrate Schottky diode is often not commercially available and not to integrate with CMOS circuits monolithically. Design about it has ever been introduced and the fabrication of Schottky in standard CMOS process with the additional CMOS process has been repoted while not shown the measured results<sup>[5,6]</sup>. In this paper we describe the way to design and layout a Schottky diode in a low cost commercial standard CMOS process without any process modification. The measured results and SPICE simulation model are offered.

Article ID: 0253-4177 (2005) 02-0238-05

### 2 Design and layout of Schottky diode

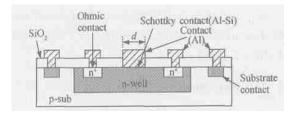

This design was performed through MPW(multi project wafer) in charted 0.35µm CMOS process. A Schottky diode is formed when a metal layer is deposited directly onto a low doped n-type or p-type semiconductor region. When these two materials are brought into contact with each other ,the difference in potential gives rise to a barrier height that the electrons have to overcome for current to flow. The metal on the low-doped semiconductor is the anode and the semiconductor material , which contacted through an ohmic contact , is the cathode. In our design only ntype Schottky diodes were used. A cross section of the Al-Si Schottky diode is shown in Fig. 1.

Received 24 May 2004 ,revised manuscript received 2 August 2004

<sup>\*</sup> Project supported by National High Technology Research and Development Program of China (No. 2003AA1Z1280)

Li Qiang male, PhD candidate. His research field emphases on analog integrate circuit design. Email : liqiang @fudan.edu.cn

Fig. 1 Cross section of Al-Si Schottky

In our design, there was no  $p^+$  active region under the contact in mwell, the contact material is aluminum with area A (equal to  $d \times d$ ). Therefore, the metal layer will connect directly to the low-doped mwell. As a result there forms a AFSi Schottky diode contact. For the foundry process determines most of the parameters such as work function of metal and density of n-well, we can only control the area A of Schottky diode to modify the *I-V* curve or other parameters of the diode.

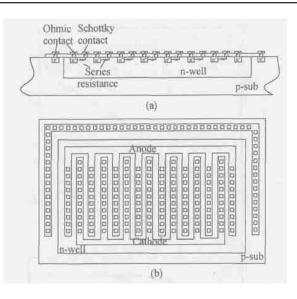

Figure 2 shows the layout of designed Schottky diode. In order to reduce the series resistance of the Schottky diode, firstly, the distance between the Schottky and ohmic contacts was set to the minimum allowable according to the design rules. Secondly, interdigitating the fingers of Schottky diode layout was adopted. The interdigitated layout offers the advantage of parallel connecting of each series resistance under Schottky contact.

# 3 Measurement results of the fabricated diode

Three types of interdigitating fingers Schottky diodes with different area have been fabricated in the charted standard 0.35µm CMOS process through MPW. The measured results are discussed.

#### **3.1** I-V performance

Considering the series resistor, the I-V function of Schottky diode can be express as<sup>[7]</sup>

$$I = I_{s} \exp\left(\frac{V - IR_{s}}{nV_{t}}\right) \left[1 - \exp\left(\frac{V - IR_{s}}{V_{t}}\right)\right] \quad (1)$$

Fig. 2 (a) Cross section layout of the realized Schottky diode; (b) Plane section layout of the realized Schottky diode

where V is the bias voltage,  $I_s$  is the saturation current,  $R_s$  is the series resistor,  $V_t$  is the thermal voltage which equals to kT/q, and n is the SBD ideality factor which can be calculated as:

$$n = I/(V_t \frac{\mathrm{d}I}{\mathrm{d}V}) \tag{2}$$

If the bias voltage is larger than 3 k T/q, Equation (1) can be simplified as

$$I = I_{s} \exp\left(\frac{V - IR_{s}}{nV_{t}}\right)$$

(3)

And the Schottky barrier height  $\phi_B$  can be calculated as

$$\phi_{\rm B} = V_{\rm t} \ln\left(\frac{AA^{*}T^2}{I_{\rm s}}\right) \tag{4}$$

where  $A^*$  is the effective Richardson constant.

The measured I-V curve is shown in Fig. 3.

By fitting Eq. (3) and the measured results, we can get the parameters of the realized SBDs, which are shown in Table 1.

Table 1 Parameters of the realized SBD

|      | Area/µm <sup>2</sup> | Finger number | $I_s/A$             | R <sub>s</sub> / |

|------|----------------------|---------------|---------------------|------------------|

| SBD1 | 16                   | 10            | 2 ×10 <sup>-8</sup> | 10               |

| SBD2 | 1.6                  | 2             | 5 ×10 <sup>-9</sup> | 90               |

| SBD3 | 0.64                 | 0             | 1 ×10 <sup>-9</sup> | 200              |

From Table 1, we can observe that with the number of interdigitating fingers increasing ,the series resistance can be reduced evidently.

Fig. 3 (a) Measured I-V curves at forward bias; (b) Measured I-V curves at reverse bias Area of SBD1, SBD2, and SBD3 are respectively 16, 1.6, and 0.64 $\mu$ m<sup>2</sup>.

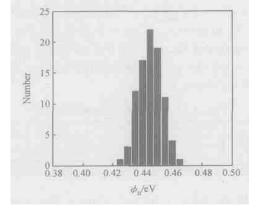

The measured statistic result of barrier height  $\phi_B$  for the realized SBD is shown in Fig. 4. There are total 90 samples that have been measured (30 samples for each of SBD1, SBD2, SBD3). And the barrier height of the realized SBD is about 0. 44eV.

Fig. 4 Statistic result of  $\phi_{\rm B}$  for the measured SBD (total 90 samples)

The breakdown voltage is about 4.5V. In future work, the breakdown voltage can be extended by some methods that have been used in normal SBD design, such as the fabrication of SBD with self aligned guard ring<sup>[8]</sup>.

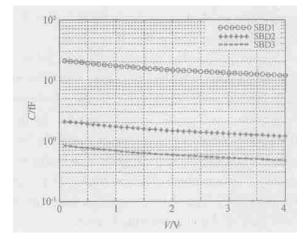

#### 3.2 C-V performance

The small signal junction capacitor  $C_j$  of Schottky diode is given below,

$$C_{\rm j} = A \sqrt{\frac{q_{\rm s} N_{\rm d}}{2(\phi_{\rm B} - \phi_{\rm n} - V)}}$$

(5)

where  $N_{\rm d}$  is the doping concentration of the m well,  $\phi_{\rm n}$  is the potential difference between the fermi level and the conduction band edge which equals to  $(E_{\rm C} - E_{\rm f})/q$ .

Figure 5 shows the measured reverse bias C-V curve for SBDs.

Fig. 5 Measured C-V curve f = 2.4 GHz

### 3.3 S parameter measurement and SBD high frequency modeling

In order to measure the high frequency S parameter of the designed devices, each SBD was laid with three probe pads. The size of middle signal pad is  $85\mu$ m ×85 $\mu$ m and top/ bottom ground size is  $85\mu$ m ×  $135\mu$ m. Using the GSG probe and network analysis instrument, we can get the S parameter of the designed SBD. But the directly measured results of S parameter include the parasitic capacitance of pads, metal line and overlays. For the designed device is very small, these parasitic parameters could not be neglected and must be subtracted from the directly measured *S* parameter by GSG probe. In our works, we fabricated two dummy GSG pads with no tested device. The dummy pads size is the same as that including SBD. One dummy GSG pads ' signal is connected with GND called short pad. The other dummy GSG pads ' signal is open which is called open pad. The *S* parameter of dummy pads should be measured. Then we can get the parasitic capacitance and resistance of the pad and metal line. And subtracting these parasitic parameter we can get the *S* parameter of SBDs with no parasitic capacitance and resistance. This method is called de-embedding technology<sup>[9]</sup>.

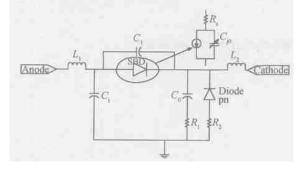

Using the measured *S* parameter, the SPICE model can be abstracted for high frequency simulation. Figure 6 shows the simulation model of the realized SBD.  $L_1$  and  $L_2$  exhibit the input and output serial inductance.  $C_i$  and  $C_o$  exhibit the anode input and cathode node output capacitance respectively.  $C_1$  exhibits the parasitic capacitance between the interdigitating fingers of Schottky diode 's two ports.  $R_1$  and  $R_2$  model for the resistance under the r-well which connects the place under NWLL to ground. The pn diode reflects the parasite n-well-p-sub diode. In our design, the parameter of the pn diode can be gotten from the charted 0.35µm analog CMOS process SPICE model.

Fig. 6 Simulation model of the realized SBD

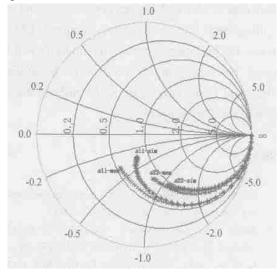

Figure 7 shows the measured and simulation *S* parameter of SBD1 (after de-embedding). Table 2 shows the parameter of SBD1 by the simulation model. The frequency is swept from 50MHz to 40GHz. And the model can match the measured results up to 30GHz. Figure 8 shows the photo of realized SBD un-

#### der probe measurement.

Fig. 7 Measurement and simulation *S* parameter of SBD1 from 50MHz to 40 GHz after detembedding

Fig. 8 Photo of the realized SBD under GSG probe measurement

Table 2 Component value of SBD1

|                | 1       |          |                       |

|----------------|---------|----------|-----------------------|

| $L_1$          | 0.005nH | L 2      | 0.005nH               |

| Ci             | 0.01pf  | Co       | 0.05pf                |

| $R_1$          | 200     | $R_2$    | 200                   |

| $C_1$          | 0.14pf  | Is       | 2 ×10 <sup>-8</sup> A |

| R <sub>s</sub> | 10      | $C_{i0}$ | 0.022pf               |

| B <sub>v</sub> | 4.5V    | Nbv      | 23                    |

### 4 Conclusion

Fabrication of Schottky barrier diode in standard CMOS process through MPW are performed. The barrier height of the Al-nSi contacts is about 0. 44eV. The measured FV, C-V, and S parameter of the re-

alized SBDs are shown in this paper. The advantages of this SBD design are low cost and can be integrated into commercial standard CMOS process. In the future work ,more emphasis will be focused on extension of the reverse breakdown voltage and frequency range of the SBDs designed on standard CMOS process.

#### References

- Sharma B L. Metal-semiconductor Schottky barrier junctions and their applications. New York: Plenum, 1984

- [2] Hudait M K, Vankateswarlu P, Krupanidhi S B. Electrical transport characteristics of Au/ n GaAs Schottky diodes on n Ge at low temperatures. Solid State Electron, 2001, 45(1):133

- [3] Zhang Yuming, Zhang Yimen, Alexandrov P, et al. Fabrication of 4HSiC merged PN-Schottky diodes. Chinese Journal of Semi-

conductors ,2001 ,22(3) :265

- [4] Zhang Haiyan, Ye Zhizhen, Huang Jingyun, et al. Fabrication of Schottky barrier diodes of high frequency based on thin silicon epilayer. Chinese Journal of Semiconductors, 2003, 24(6):622 (in Chinese)[张海燕,叶志镇,黄靖云,等. 在薄硅外延片上制 备高频肖特基势垒二极管.半导体学报,2003,24(6):622]

- [5] Milanovic V, Gaitan M, Marshall J C, et al. CMOS foundry implementation of Schottky diodes for RF detection. IEEE Trans Electron Devices, 1996, 43 (2):2210

- [6] Rivera B ,Baker R J ,Melngailis J. Design and layout of Schottky diodes in a standard CMOS process. International Semiconductor Device Research Symposium ,2001 :79

- [7] Rhoderick E H. Metal-semiconductor contacts. Second edition. Oxford :Oxford University Press ,1988

- [8] Cha S I, Cho Y H. Novel Schottky diode with selfaligned guard ring. Electron Lett, 1992:1221

- [9] Aktas A, Ismail M. Pad de-embedding in RF CMOS. IEEE Circuit and Devices Magazine, 2001, 17(3):8

## 标准 CMOS 工艺集成肖特基二极管设计与实现 '

李强王俊宇韩益锋闵昊

(复旦大学专用集成电路与系统国家重点实验室,上海 200433)

**摘要**:提出了一种在标准 CMOS 工艺上集成肖特基二极管的方法,并通过 MPW 在 charted 0.35µm 工艺中实现. 为了减小串连电阻,肖特基的版图采用了交织方法.对所设计的肖特基二极管进行了实测得到 *FV*, *CV* 和 *S* 参数,并计算得出所测试肖特基二极管的饱和电流、势垒电压及反向击穿电压.最后给出了可用于 SPICE 仿真的模型.

关键词:CMOS;肖特基二极管;集成 EEACC:2560H;2570D 中图分类号:TN311<sup>+</sup>.7 文献标识码:A 文章编号:0253-4177(2005)02-0238-05

李强男,博士研究生,研究方向为模拟集成电路设计. Email :liqiang @fudan.edu.cn

2004-05-24 收到,2004-08-02 定稿

<sup>\*</sup>国家高技术研究发展计划资助项目(批准号:2003AA1Z1280)