# A New Low Voltage RF CMOS Mixer Design \*

# Liu Lu<sup>1</sup> and Wang Zhihua<sup>2</sup>

(1 Department of Electronic Engineering, Tsinghua University, Beijing 100084, China)

(2 Institute of Microelectronics, Tsinghua University, Beijing 100084, China)

**Abstract:** A new architecture of CMOS low voltage downconversion mixer is presented. With 1. 452 GHz LO input and 1. 45 GHz RF input, simulation results show that the conversion gain is 15dB, IIP3 is - 4. 5dBm, NF is 17dB, the maximum transient power dissipation is 9. 3mW, and DC power dissipation is 9. 2mW. The mixer 's noise and linearity analyses are also presented.

Key words: downconversion mixer; CMOS process; noise and linearity analysis

**EEACC:** 1250

**CLC number:** TN432 **Document code:** A **Article ID:** 0253-4177 (2005) 05-0877-04

### 1 Introduction

In recent years low voltage has become a target in most digital and analog integrated circuit applications. The most commonly used CMOS mixer topology is Gilbert mixer<sup>[1]</sup>. It has stacked structure, which limits its use in low supply voltage applications. Recently, a lot of efforts have been spent on the development of low-voltage CMOS RF mixers. In Refs. [2,3], the presented mixer avoids the stacking of transistors; tradeoff is that it suffers from a lower conversion gain for a given power. In Ref. [4], MOS transistor is used as a four-terminal device, RF and LO signals are applied to the gate and the back gate while the mixing product is extracted from the drain; this kind of mixer can be working on a low supply voltage, but it is difficult to predict the mixer performance due to the lack of

adequate model for the transistor in such working mode. In Ref. [5], LC tanks are used in the mixer to achieve low voltage operation, but in CMOS technology, Q-value of the spiral inductor is relatively low, and the inductor occupies a lot of chips space.

In this paper, a high gain downconversion CMOS mixer with low supply voltage is presented; the topology of the mixer has never been reported previously. This new mixer does not need inductors, so it is relatively easy to fabricate.

### 2 Architecture of proposed mixer

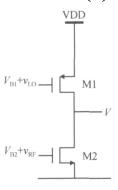

Figure 1 shows the basic operating principle of the mixer. In this mixer core, transistor M1 is working in the triode region, transistor M2 is working in the saturation region, the current flow through M1 and M2 is equal, so that

<sup>\*</sup> Project supported by National Natural Science Foundation of China (Nos. 60475018,60372021) and State Key Development Program for Basic Research of China (No. G2000036508)

Liu Lu female, PhD candidate. Her work focuses on the analog circuit design and RF front-end circuit design.

Wang Zhihua male ,professor. His research areas include analog/ mixed signal/ RF CMOS integrated circuit technology ,ASIC design for communication systems ,algorithm exploration and ASIC design of digital audio/ video signal processing systems ,design of integrated electronic systems and SOC.

$$\frac{1}{2} \mu_{n} C_{on} \left( \frac{W}{L} \right)_{2} (V_{B2} + \nu_{RF} - V_{Tn})^{2} = \mu_{p} C_{xo} \left( \frac{W}{L} \right)_{1} (VDD - V_{B1} - \nu_{LO} - / V_{Tp} /) (VDD - \nu)$$

(1)

Equation (1) can be changed into

$$v = VDD - \frac{\frac{1}{2} \mu_n \left( \frac{W}{L} \right)_2 (V_{B2} + \nu_{RF} - V_{Tn})^2}{\mu_p \left( \frac{W}{L} \right)_1 (VDD - V_{B1} - / V_{Tp} /)} \times \frac{1}{1 - \frac{\nu_{LO}}{VDD - / V_{Tp} / - V_{B1}}}$$

(2)

Fig. 1 Basic operating principle of the proposed mixer

$V_{\rm Tn}$  and  $V_{\rm Tp}$  are the threshold voltage of M2 and M1,  $\mu_{\rm n}$  and  $\mu_{\rm p}$  are the mobilities of charge carriers of NMOS and PMOS transistors, W, L, and  $C_{\rm ox}$  represent the transistor 's width, length, and gate capacitance per unit area, respectively,  $V_{\rm B1}$  and  $V_{\rm B2}$  are DC bias voltages. The bias voltage and the aspect ratio of transistors are selected to guarantee

$$\frac{v_{\text{LO}}}{\text{VDD} - / V_{\text{Tp}} / - V_{\text{BI}}} \ll 1 \tag{3}$$

Thus

$$\frac{1}{1 - \frac{v_{1.0}}{VDD - / V_{Tp} / - V_{B1}}} = \frac{1 + \frac{v_{1.0}}{VDD - / V_{Tp} / - V_{B1}}$$

Then equation (2) can be approximated to

$$v \quad VDD - \frac{\frac{1}{2} \mu_{n} \left(\frac{W}{L}\right)_{2} (V_{B2} + v_{RF} - V_{Tn})^{2}}{\mu_{p} \left(\frac{W}{L}\right)_{1} (VDD - V_{B1} - / V_{Tp} /)} - \frac{\frac{1}{2} \mu_{n} \left(\frac{W}{L}\right)_{2} (V_{B2} - V_{Tn})^{2} v_{LO}}{\mu_{p} \left(\frac{W}{L}\right)_{1} (VDD - V_{B1} - / V_{Tp} /)} - \frac{\mu_{n} \left(\frac{W}{L}\right)_{2} (V_{B2} - V_{Tn}) v_{RF} v_{LO}}{\mu_{p} \left(\frac{W}{L}\right)_{1} (VDD - V_{B1} - / V_{Tp} /)^{2}}$$

$$(4)$$

The last term in Eq. (4) is proportional to  $v_{RF} v_{LO}$ ; this term can be used to achieve mixing.

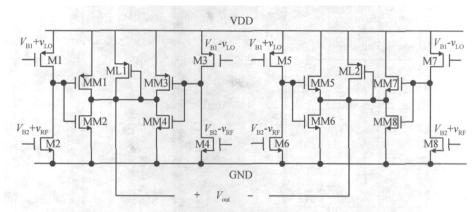

Figure 2 is the complete schematic diagram of

the proposed mixer it has four sections: section 1 is composed of M1, M2, MM1, and MM2; section 2 is composed of M3, M4, MM3, and MM4; section 3 is composed of M5, M6, MM5, and MM6; and section 4 is composed of M7, M8, MM7, and MM8. The functions of the four sections are equal; each section consists of a mixer core (for example M1 and M2) and an output transconductance stage (for example MM1 and MM2, which are used to convert the output voltage of the mixer core into current). Transistors ML1 and ML2 have equal sizes. They are used to add the output transconductance stages 'output current and convert the added current into voltage. Vout is the output voltage of the mixer. The balanced structure is chosen to reduce the feed through of LO and RF signals.

The commonly used active mixer, such as Gilbert mixer, is to achieve mixing through current, and it has a transconductance stage, which converts the RF input voltage into current, the LO signal switches the currents on and off, the output currents contains the mixing terms and are converted into voltage by using transistors or resistances as load. This kind of mixer has a procedure of converting voltage into current and then converting the current back into voltage, so the structure are complex and usually has stacked transistors. In this paper, first the RF input voltage is converted into current whose value is proportional to RF input voltage, then this current flows through LO controlled load, the resistance of this load has a term which is proportional to the LO voltage, so the output voltage has the mixing term. This kind of mixing procedure is rather simple; the mixer core only has two transistors, thus can be working in low supply voltage. The supply voltage can be adjusted lower depending on the system requirements.

Fig. 2 Complete schematic diagram of the mixer

## 3 Mixer noise and linearity analysis

The design of the mixer requires a compromise, and the performance parameters of the mixer should be carefully specified for different applications. In this paper, the mixer is designed with high gain and low operating voltage, moderate NF (noise figure), and IIP3 (input referred third-order intercept point).

The noise contribution of each transistor of the proposed mixer can be simulated and calculated by Cadence SpectreRF. This mixer is a low IF downconversion mixer, and the thermal noise is the primary noise source.

$I_{\rm d}^2(f)$  represents the thermal noise current in the drain due to the channel resistance. If the transistor operates in the triode region,

$$I_{\rm d}^2(f) = \frac{4kT}{r_{\rm ds}} \tag{5}$$

Where  $r_{ds}$  is the channel resistance<sup>[6]</sup>.

For the long-channel transistor working in the saturation  $region^{[6]}$ ,

$$I_{\rm d}^2(f) = 4kT g_{\rm m} \tag{6}$$

The coefficient is derived to be equal to 2/3 for long-channel transistors and may be needed to be replaced by a larger value for submicron MOS-FETs.

Transistors M1, M3, M5, and M7 are working in the triode region; their noise can be reduced by increasing their lengths. Simulation results show that transistors M2, M4, M6, and M8 contribute to

most of the noise. As they are working in saturation region, the transconductance of them should be large enough to minimize their equivalent noise voltage at the circuit input. After adjusting the parameter value of the mixer, simulation shows that it has a NF of 17dB.

Linearity is an important consideration in mixer design from Eqs.  $(1 \sim 4)$ , it can be seen that to achieve high linearity, the condition of Eq. (4) must be satisfied. The linearity of the mixer is also determined by the linearity of mixer core and output transconductance stage. The linearity of the mixer core is determined by the lower MOS transistor in the mixer core, which is the RF input transconductance stage. Transconductance linearity can be improved by increasing the gate overdrive voltage, but increasing the gate overdrive will increase power consumption. To increase the linearity of the output transconductance stage, the aspect ratio of the two transistors of the transconductance stage is carefully chosen to cancel the nonlinear terms.

### 4 Simulation results

The mixer circuit is simulated using Cadence SpectreRF based on Dongbu 0.25µm CMOS process. The simulation result of this mixer is summarized in Table 1. It is a low supply voltage high gain mixer, with moderate IIP3 and NF. The frequency of RF signal is 1.452 GHz; LO signal frequency is 1.45 GHz; this is because the mixer is de-

signed for L-band DAB applications.

Table 1 Mixer performance

| 1                                   |                |

|-------------------------------------|----------------|

| Supply voltage                      | 2V             |

| DC power dissipation                | 9. 2mW         |

| Maximum transient power dissipation | 9. 3mW         |

| Conversion gain                     | 15dB           |

| IIP3                                | - 4. 5dBm      |

| NF                                  | 17dB           |

| LO frequency                        | 1. 45 GHz      |

| RF frequency                        | 1. 452 GHz     |

| LO amplitude                        | 0dBm           |

| Technology                          | Dongbu 0. 25µm |

|                                     |                |

### 5 Conclusion

In this paper, a new CMOS RF downconversion mixer is presented. The mixer first converts the RF input voltage signal into current, then this current flows through a transistor working in the triode region whose resistance is modulated by the LO signal. This kind of mixer can work in a relatively low supply voltage.

This mixer achieved a simulated conversion

gain of 15dB, IIP3 of - 4.5dBm, and NF of 17dB, with a DC power consumption of 9.2mW from a single 2V supply.

#### References

- [ 1 ] Chi Baoyong ,Shi Bingxue. CMOS mixers for 2. 4 GHz WLAN transceivers. Chinese Journal of Semiconductors ,2003 ,24(5): 472

- [2] Cui Fuliang ,Ma Dequn ,Huang Lin ,et al. Low voltage CMOS Glbert mixers for bluetooth transceiver. Chinese Journal of Semiconductors ,2004 ,25 (9) :1066

- [ 3 ] Kan T K K,Mak K C,Ma Dongsheng,et al. A 2-V 900-MHz CMOS mixer for GSM receivers. IEEE International Symposium on Circuits and Systems, 2000, 1:327

- [4] Wang Hongmo. A 1-V multigigahertz RF mixer core in 0. 5µm CMOS. IEEE J Solid-State circuits, 1998, 33(12):2265

- [5] Tang C C ,Lu W S ,Van L D ,et al. A 2. 4-GHz CMOS down-conversion doubly balanced mixer with low supply voltage. IEEE International Symposium on Circuits and Systems, 2001,4:794

- [6] Johns D, Martin K. Analog integrated circuit design. New York:John Wiley & Sons, Inc, 1997:199

## 一种新的射频 CMOS 混频器结构 \*

#### 刘 璐 王志华2

- (1 清华大学电子工程系, 北京 100084)

- (2 清华大学微电子研究所, 北京 100084)

摘要:提出了一种低电压高增益 CMOS 下变频混频器的新结构.这个结构避免了堆叠晶体管,因此可以在低电压下工作.在 LO 信号的频率为 1.452 GHz,RF 信号频率为 1.45 GHz 的情况下,仿真结果表明:混频器的增益为 15dB,IIP3 为 -4.5dBm,NF 为 17dB,最大瞬态功耗为 9.3mW,直流功耗为 9.2mW.并对该混频器的噪声特性和线性度进行了分析.

关键词:下变频混频器; CMOS 工艺; 噪声和线性度分析

**EEACC:** 1250

中图分类号: TN432 文献标识码: A 文章编号: 0253-4177(2005)05-0877-04

<sup>\*</sup>国家自然科学基金(批准号:60475018,60372021)和国家重点基础研究发展计划(批准号:G2000036508)资助项目

刘 璐 女,博士研究生,研究方向为模拟电路及射频前端电路设计.

王志华 男,教授,研究方向包括 CMOS 模拟、数模混合及射频集成电路技术,通信专用集成电路设计,数字音频及视频信号处理及专用集成电路和电子系统集成及片上系统.