# An Accurate 1. 08 GHz CMOS LC Voltage-Controlled Oscillator \*

Tang Zhangwen, He Jie, Jian Hongyan, and Min Hao

(State Key Laboratory of ASIC & System, Fudan University, Shanghai 200433, China)

Abstract: An accurate 1. 08 GHz CMOS LC voltage-controlled oscillator is implemented in a 0. 35µm standard 2P4M CMOS process. A new convenient method of calculating oscillator period is presented. With this period calculation technique, the frequency tuning curves agree well with the experiment. At a 3. 3V supply, the LC-VCO measures a phase noise of - 82. 2dBc/ Hz at a 10kHz frequency offset while dissipating 3. 1mA current. The chip size is 0. 86mm ×0. 82mm.

Key words: MOS varactor; LC tank; voltage controlled oscillator; oscillator tuning curve

**EEACC:** 1230B

#### 1 Introduction

The explosive growth in wireless communications has driven universities and companies to produce wireless transceivers at low-cost, low-power, and compact size. Recently, all of RF components, such as low-noise amplifiers (LNAs), mixer, local oscillators (LOs), and IF filters, seem possible to be integrated in CMOS scaled technology. On-chip passive elements such as spiral inductors and varactors make on-chip implementation of LC-tank voltage-controlled oscillators (VCOs) easy.

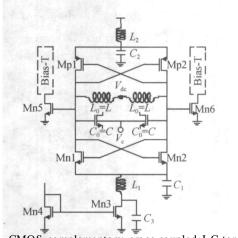

A complementary cross-coupled negative  $G_m$  LC-tank oscillator is shown in Fig. 1, which employs both nMOS and pMOS cross-coupled pairs. Many published papers<sup>[1~3]</sup>, have employed this type of LC-tank VCO, but oscillator 's tuning curves were obtained from SPICE simulations or measurements. The prediction of oscillator 's tun-

ing curves is quite challenging due to highly nonlinear characteristics of varactors. A numerical method is shown in Ref. [3], but it is quite complex and time-consuming. The tuning curves must be numerically computed again if bias current changes.

Fig. 1 CMOS complementary cross-coupled LC-tank

<sup>\*</sup> Project supported by System-Design-Chip Program of Shanghai Science & Technology Committee (No. 037062019) and Shanghai Applied Material Funds (No. 0425)

Tang Zhangwen male ,was born in 1977 ,assistant professor. His research interests are in low-phase-noise LC VCO and RF TV tuner.

$He\ Jie\quad male\ , was\ born\ in\ 1978\ , PhD\ candidate.\ His\ research\ interest\ is\ fully-integrated\ RF\ frequency\ synthesizers.$

In this paper, we investigate the FV locus of step-like MOS varactors in a LC-VCO and predict the tuning curves through the oscillating period calculation of a serial LC tank in time domain<sup>[4,9]</sup>. An accurate 1.08GHz CMOS LC voltage-controlled oscillator is implemented in a 0.35µm standard 2P4M CMOS process. The theoretical analyses agree perfectly with the simulation and measurement of a CMOS complementary LC-tank VCO.

### 2 Circuit design

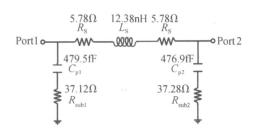

The complementary cross-coupled negative  $G_{\rm In}$  LC-tank voltage-controlled oscillator in Fig. 1 has been implemented in 0. 35µm 2P4M 3. 3V CMOS process. On-chip spiral inductor is a symmetric differential multilayer inductor. Four metals are parallelly and serially connected with a lot of vias to decrease the serial resistor of spiral inductor and increase the inductance in unit silicon area. And a center-connected patterned ground shield (PGS) is employed to improve quality of inductors at low frequency  $(1 \sim 2\,{\rm GHz})^{[5]}$ . On-chip differential spiral inductor is 12. 4nH, so the single-ended inductor features 6. 2nH. The maximum Q arrives seven at 1. 1 GHz. The compact equivalent PI model shown in Fig. 2 is extracted with ASITIC<sup>[6]</sup>.

Fig. 2 PI model of on-chip spiral inductor

The transconductances of cross-couple nMOS and pMOS devices are chosen to be equal so that DC voltage of LC-tank oscillator is maintained at approximately  $V_{\rm dd}/2$ . First, the oscillating waveform can have the maximum swing. Secondly, the VCO gain ( $K_{\rm V}$ ) can be decreased and the phasenoise performance can be improved. The MOS de-

vices are implemented using the minimum gate length (0.  $35\mu m$ ). The open-drain nMOS devices are the output buffers, which is used to drive the off-chip bias T circuits. In order to decrease the Miller-effect capacitor, the length of open-drain nMOS devices is  $60\mu m$ . The lengths of current-mirror are larger than the minimum length so that the channel length modulation (CLM) is attenuated and 1/f noise is decreased.

Two additional inductors, L1 & L2, resonate at double frequency with the parasitic capacitors C1 & C2 at each common-source node, to avoid Q-degradation by triode region MOS transistors in the stacked differential pairs<sup>[7]</sup>. The filtering capacitor C3 is used to low the 1/f noise and effect of channel length modulation (CLM)<sup>[1]</sup>.

### 3 Frequency tuning characteristic

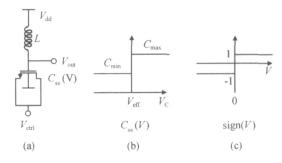

Most of varactors used in LC-tank VCO circuits are inversion-MOS (FMOS) and accumulation-MOS(A-MOS). Their characteristics both are step-like, and have large nonlinearity. The tuning curves of an LC-VCO will substantially deviate from the ideal curve  $1/\sqrt{LC}$  when a step-like varactor is used [3]. Both FMOS and A-MOS are step-like capacitors (Figs. 3(b) and (c)). The small-signal capacitance is given by

$$C_{\rm ss}(V) = \begin{cases} C_{\rm max}, & V & V_{\rm eff} \\ C_{\rm min}, & V < V_{\rm eff} \end{cases}$$

(1)

where  $V_{\text{eff}} = V_{\text{ctrl}} + V_{\text{TH}}$  is effective control voltage (ECV).

Fig. 3 Serial LC-tank and step-like varactor (a) Serial LC tank; (b) Step-like varactor; (c) Unit step function

The presence of on-chip inductors in Fig. 1 imposes that the DC value of differential oscillating voltages has to be a constant voltage  $V_{\rm dc}$ . Neglecting the tank losses in on-chip inductors and varactors, the half circuit of LC-tank VCO can be considered as a serial LC-tank structure (Fig. 3 (a)). The value of inductor is L, and the step-like varactors can be mathematically represented as below

$$C_{ss}(V) = \frac{1}{2} (C_{max} + C_{min}) + \frac{1}{2} (C_{max} - C_{min}) \operatorname{sign}(V - V_{eff})$$

(2)

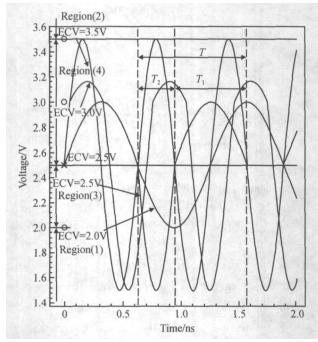

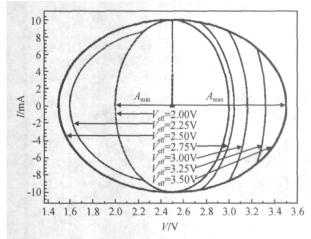

Figure 4 shows the oscillating voltage waveforms of the serial LC tank simulated in HSPICE. Each waveform consists of two segmental sinusoids

Fig. 4 Voltage waveforms of a varactor at different ECV

with different size, which join at the effective control voltage (ECV). With the ECV from low to high, there exist four regions as below:

- (1) When  $V_{\text{eff}}$   $V_{\text{dc}}$   $A_{\min}$ , the oscillating waveform is a sinusoid with the minimum amplitude  $A_{\min}$  and minimum frequency  $\min$ ;

- (2) When  $V_{\text{eff}}$   $V_{\text{dc}} + A_{\text{max}}$ , a sinusoid with the maximum amplitude  $A_{\text{max}}$  and maximum frequency  $M_{\text{max}}$ ;

- (3) When  $V_{\rm dc}$   $A_{\rm min}$   $V_{\rm eff}$   $V_{\rm dc}$ , two partial sinusoids join at ECV. One is over  $V_{\rm eff}$  with the am-

plitude  $A_{\min}$  and frequency  $_{\min}$ ; the other is below  $V_{\text{eff}}$  with the amplitude  $_{1}A_{\max}$  ( $_{1}$  is an ellipse similar factor, ESF) and frequency  $_{\max}$ ;

(4) When  $V_{\rm dc}$   $V_{\rm eff}$   $V_{\rm dc}$  +  $A_{\rm max}$ , it consists of two segmental sinusoids joined at ECV. One is above  $V_{\rm eff}$  with the amplitude  $_2A_{\rm min}$  ( $_2$  is another ESF) and frequency  $_{\rm min}$ ; the other is below  $V_{\rm eff}$  with the amplitude  $A_{\rm max}$  and frequency  $_{\rm max}$ .

The FV locus of a step-like varactor in the serial LC-tank circuit is shown in Fig. 5. It consists of two ellipses of different size joined at the ECV. The above four regions satisfy the following ellipses 'equations:

Fig. 5 FV locus of a varactor

(1) When  $V_{\text{eff}}$   $V_{\text{dc}}$  -  $A_{\text{min}}$ , the FV locus holds  $\left(\frac{V - V_{\text{dc}}}{A_{\text{min}}}\right)^2 + \left(\frac{I}{\text{min } C_{\text{max}} A_{\text{min}}}\right)^2 = 1$  (3)

(2) When

$$V_{\text{eff}}$$

$V_{\text{dc}} + A_{\text{max}}$ , it holds

$$\left(\frac{V - V_{\text{dc}}}{A_{\text{max}}}\right)^{2} + \left(\frac{I}{\text{max } C_{\text{min}} A_{\text{max}}}\right)^{2} = 1$$

(4)

(3) When  $V_{dc}$  -  $A_{min}$   $V_{eff}$   $V_{dc}$ , two segmental sinusoids respectively hold

$$\left\{ \left( \frac{V - V_{dc}}{A_{\min}} \right)^{2} + \left( \frac{I}{\min C_{\max} A_{\min}} \right)^{2} = 1, \quad V \quad V_{eff} \\ \left( \frac{V - V_{dc}}{A_{\max}} \right)^{2} + \left( \frac{I}{\max C_{\min} A_{\max}} \right)^{2} = \frac{2}{1}, \quad V < V_{eff} \\ (5)$$

where the ESF  $_1$  satisfies  $A_{\min}/A_{\max}$   $_1$  1. Especially when  $V_{\text{eff}} = V_{\text{dc}}$  and  $_1 = 1$ , it satisfies

$$I_{\text{max}} = \min_{\text{min}} C_{\text{max}} A_{\text{min}} = \max_{\text{max}} C_{\text{min}} A_{\text{max}}$$

(6)

where  $I_{\text{max}}$  is the maximum current in the inductor or varactor.

(4) When  $V_{\rm dc}$   $V_{\rm eff}$   $V_{\rm dc}$  +  $A_{\rm max}$ , two segmental sinusoids respectively hold

$$\left\{ \left( \frac{V - V_{dc}}{A_{\min}} \right)^{2} + \left( \frac{I}{\min C_{\max} A_{\min}} \right)^{2} = \frac{2}{2}, \quad V \quad V_{\text{eff}} \right.$$

$$\left( \frac{V - V_{dc}}{A_{\max}} \right)^{2} + \left( \frac{I}{\max C_{\min} A_{\max}} \right)^{2} = 1, \quad V < V_{\text{eff}}$$

(7)

where the ESF 2 satisfies 1 2  $A_{\text{max}}/A_{\text{min}}$ .

The oscillating periods in the above four regions can be calculated mathematically.

(1) When  $V_{\rm eff}$   $V_{\rm dc}$  -  $A_{\rm min}$  ,the oscillating period is

$$T = T_{\text{max}} = 2 \sqrt{L C_{\text{max}}} \tag{8}$$

(2) When  $V_{\rm eff} = V_{\rm dc} + A_{\rm max}$ , the oscillating period is

$$T = T_{\min} = 2 \sqrt{L C_{\min}}$$

(9)

(3) When  $V_{\rm dc}$  -  $A_{\rm min}$   $V_{\rm eff}$   $V_{\rm dc}$ , the oscillating period is a sum of two intervals,  $T = T_1 + T_2$ , as shown in Fig. 4.  $T_1$  is the time on the first ellipse;  $T_2$  is the time on the second ellipse. At the ECV, the voltage and current of the varactor are  $V_{\rm eff}$  and  $I_{\rm eff}$ . From Eqs. (6),(8), and (9), we obtain the amplitude ratio

$$\frac{A_{\text{max}}}{A_{\text{min}}} = \sqrt{\frac{C_{\text{max}}}{C_{\text{min}}}} \tag{10}$$

Substituting Eq. (10) to (5) leads to the ESF 1

$$1 = \sqrt{-\left(\frac{V_{\text{eff}} - V_{\text{dc}}}{A_{\min}}\right)^2 + \left(\frac{V_{\text{eff}} - V_{\text{dc}}}{A_{\max}}\right)^2}$$

(11)

Thus, the oscillating period is,

$$T = T_{1} + T_{2} = \frac{1}{2} + \arcsin\left(\frac{V_{\text{eff}} - V_{\text{dc}}}{A_{\text{min}}}\right) T_{\text{max}} + \frac{1}{2} - \arcsin\left(\frac{V_{\text{eff}} - V_{\text{dc}}}{1A_{\text{max}}}\right) T_{\text{min}} = \frac{1}{2} \left(T_{\text{max}} + T_{\text{min}}\right) + \frac{1}{2} \left(\arcsin\left(\frac{V_{\text{eff}} - V_{\text{dc}}}{A_{\text{min}}}\right) T_{\text{max}} - \arcsin\left(\frac{V_{\text{eff}} - V_{\text{dc}}}{1A_{\text{max}}}\right) T_{\text{min}}\right)$$

$$(12)$$

(4) When  $V_{\rm dc}$   $V_{\rm eff}$   $V_{\rm dc}$  +  $A_{\rm max}$ , similarly to Case (3). Solving Eq. (7), we can obtain the ESF and oscillating period,

$$_{2} = \sqrt{-\left(\frac{V_{\text{eff}} - V_{\text{dc}}}{A_{\text{max}}}\right)^{2} + \left(\frac{V_{\text{eff}} - V_{\text{dc}}}{A_{\text{min}}}\right)^{2}}$$

(13)

$$T = \frac{1}{2} \left( T_{\text{max}} + T_{\text{min}} \right) + \frac{1}{2 \cdot A_{\text{min}}} \left( - \arcsin \left( \frac{V_{\text{eff}} - V_{\text{dc}}}{2 \cdot A_{\text{min}}} \right) T_{\text{max}} + \arcsin \left( \frac{V_{\text{eff}} - V_{\text{dc}}}{A_{\text{max}}} \right) T_{\text{min}} \right)$$

$$(14)$$

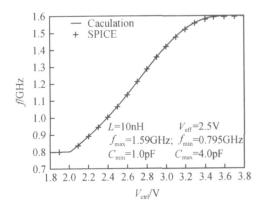

To validate the above method of oscillating period calculation, an ideal LC tank in Fig. 3 (a) is simulated in HSPICE. Its parameters are  $L=10 \, \mathrm{nH}$ ,  $C_{\mathrm{max}}=4 \, \mathrm{pF}$ ,  $C_{\mathrm{min}}=1 \, \mathrm{pF}$ , and  $A_{\mathrm{min}}=0.5 \, \mathrm{V}$ . In Fig. 6, the cross line is the simulation result in HSPICE, and the solid line is the calculation result from Eqs. (12) and (14). The simulation agrees well with the calculation.

Fig. 6 Oscillator tuning curve: simulated in SPICE, and calculated by Eqs. (12) and (14)

As the oscillator has a very large signal swing (nearly full power supply), the oscillating period is interpolated between  $T_{\rm max}$  and  $T_{\rm min}$ . The resulting frequency-voltage  $(f^-V)$  curve, which is shown in Fig. 6, varies linearly with ECV in a range defined by the oscillation amplitude. Although the capacitance-voltage  $(C^-V)$  characteristic of MOS varactors is step-like, the  $f^-V$  curve is well linear. Contrary to widely held beliefs in Ref. [8], the linear  $C^-V$  relationship of MOS varactors is unnecessary.

# 4 Experiment validation

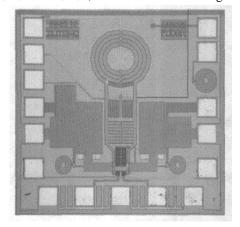

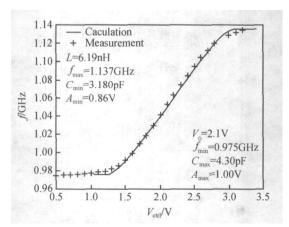

Figure 7 shows the microphotograph of LC VCO in Fig. 1. At a 3. 3V supply ,the tail current of LC-VCO is 3. 1mA, and the centre frequency is 1. 08 GHz. The oscillator 's tuning curve in Fig. 8 is obtained by the measurement of the fundamental frequency at different control voltages. On-chip dif-

ferential spiral inductor is 12. 38n H, so the single-end inductor features 6. 19n H. The maximum and minimum capacitances in LC-VCO are 4. 30p F (Cmax) and 3. 180p F (Cmin). The maximum and minimum frequencies are 1. 137 GHz and 0. 975 GHz respectively. And the DC voltage is 2. 1V, the minimum amplitude is 0. 86V, the maximum amplitude is 1. 0V calculated by Eqs. (10). In Fig. 8, the cross lines are the results of measurement, and the solid lines are calculated by Eqs. (12) and (14). The measurement agrees well with the results obtained from the theoretical oscillator tuning curves 'equations (12) and (14), over the entire tuning range.

Fig. 7 Microphotograph of CMOS LC VCO

Fig. 8 f-V tuning curve of the measurement and calculation

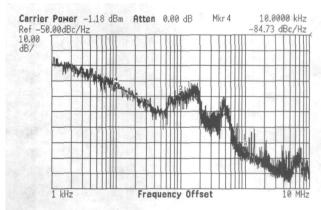

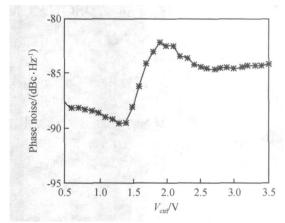

COB packaged chips are measured on a Agilent E4440A (3 Hz ~ 26.5 GHz) PSA series spectrum analyzer with phase noise module. Figure 9 shows a typical phase noise at 1.7V control voltage. The phase noise measured at different ECV

voltages, is shown in Fig. 10. The worst phase noise is - 82. 2dBc/ Hz at a 10kHz frequency offset.

Fig. 9 Phase noise

Fig. 10 Phase noise at 10kHz frequency offset

### 5 Conclusions

An accurate 1. 08 GHz CMOS LC-tank voltage-controlled oscillator is implemented in a 0. 35µm standard 2P4M CMOS process. A new convenient method of calculating frequency tuning curves is proposed. The calculated *f-V* curves agree perfectly with the experiment. At 3. 3V power supply ,the phase noise of the LC-VCO is measured to be - 82. 2dBc/ Hz at a 10kHz frequency offset. The tail current is 3. 1mA.

Acknowledgements The authors would like to thank Liu Chenbo, Yi Wei, and Jiang Qifeng of Shanghai Research Center for Integrated Circuit Design, for the support of MPW service, and thank 872 半 导 体 学 报 第 26 卷

Huang Hao, Qian Dahong for chip testing.

#### References

- [1] Hajimiri A, Lee T H. Design issues in CMOS differential LC oscillators. IEEE J Solid-State Circuits, 1999, 34:717

- [2] Tiebout M. Low-power low-phase-noise differentially tuned quadrature VCO design in standard CMOS. IEEE J Solid-State Circuits ,2001 ,36:1018

- [3] Levantino S, Samori C, Bonfanti A, et al. Frequency dependence on bias current in 5- GHz CMOS VCOs: impact on tuning range and flicker noise upconversion. IEEE J Solid-State Circuits, 2002, 37:1003

- [4] Tang Zhangwen, He Jie, Jian Hongyan, et al. Prediction of

- LC-VCOs 'tuning curves with period calculation technique. IEEE Asia South Pacific Design Automation Conference, Shanghai, China, 2005

- [5] Yue C P, Wong S S. Orrchip spiral inductors with patterned ground shields for Si-based RF IC 's. IEEE J Solid-State Circuits, 1998, 33:743

- [6] http: rfic.eecs.berkeley.edu/~niknejad/asitic.html

- [7] Hegazi E, Sjoland H, Abidi A A. A filter technique to lower LC oscillator phase noise. IEEE J Solid-State Circuits, 2001, 36:1921

- [8] Svelto F, Erratico P, Manzihi S, et al. A metal-oxide semiconductor varactor. IEEE Electron Device Lett, 1999, 20:164

- [ 9 ] Tang Zhangwhen. LC voltage-controlled oscillators. PhD dissertation of Fudan University, 2004

## 精确的 1. 08 GHz CMOS 电感电容压控振荡器 \*

### 唐长文 何 捷 菅洪彦 闵 昊

(复旦大学专用集成电路与系统国家重点实验室,上海 200433)

摘要:在  $0.35 \mu$ m 2P4M 标准 CMOS 工艺上,设计了一个精确的 1.08 GHz CMOS 电感电容压控振荡器。提出了一种有效计算压控振荡器周期的新方法,采用该方法计算的频率-电压调谐曲线与实验结果吻合得很好。在电源电压 3.3 V 下,消耗电流 3.1 mA,压控振荡器的相位噪声在 10 k Hz 频偏处为 - 82.2 dBc/ Hz. 芯片面积为 0.86 mm × 0.82 mm.

关键词: MOS 管可变电容; 电感电容回路; 压控振荡器; 振荡调谐曲线

**EEACC:** 1230B

中图分类号: TN752 文献标识码: A 文章编号: 0253-4177(2005)05-0867-06

<sup>\*</sup>上海市科学技术委员 2003 年度集成电路设计科技专项(批准号:037062019)和上海应用材料研究与发展基金(批准号:0425)资助项目 唐长文 男,1977 年出生,助理研究员,主要研究方向为低相位噪声电感电容压控振荡器和 CMOS 射频电视调谐器.

何 捷 男,1978年出生,博士研究生,主要研究方向为全集成射频频率综合器设计.