# Elevated Source/Drain Engineering by Novel Technology for Fully-Depleted SOI CMOS Devices and Circuits

Lian Jun and Hai Chaohe

(Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China)

**Abstract :** 0. 35µm thin-film fully-depleted SOI CMOS devices with elevated source/drain structure are fabricated by a novel technology. Key process technologies are demonstrated. The devices have quasi-ideal subthreshold properties; the subthreshold slope of nMOSFETs is 65mV/decade, while that of pMOSFETs is 69mV/decade. The saturation current of 1. 2µm nMOSFETs is increased by 32 % with elevated source/drain structure, and that of 1. 2µm pMOS-FETs is increased by 24 %. The per-stage propagation delay of 101-stage fully-depleted SOI CMOS ring oscillator is 75ps with 3V supply voltage.

Key words: FDSOI; CMOS; elevated source/drain EEACC: 2560 CLC number: TN386 Document code: A

Article ID: 0253-4177 (2005) 04-0672-05

# 1 Introduction

As CMOS technology continues to scale down,fully-depleted SOI (FDSOI) technology assumes a prominent position as a potential solution to the problems associated with continued device scaling<sup>[1]</sup>. Some of the benefits of using FDSOI are reduction of junction capacitance ,immunity for radiation ,latch up-free for complementary metal-oxide-semiconductor (CMOS)<sup>[2]</sup>, suppression of the short-channel effects<sup>[3]</sup>, process simplicity<sup>[4]</sup>, higher device packing density ,and so on. FDSOI devices are also superior to thick-film, partially-depleted SOI (PDSOI) devices, because FDSOI MOSFETs have no body effect<sup>[5]</sup>.

The FDSOI technology offers a potential solution to control short channel effects by reducing the silicon film thickness. However ,aggressive silicon film thickness reduction increase the parasitic source/ drain series resistance<sup>[6]</sup>. Furthermore ,conventional process cannot be used on this ultra-thin silicon film due to incomplete silicide formation. The resulting high parasitic source/ drain series resistance degrades the device performance and obscures the advantages of FDSOI<sup>[7]</sup>. Therefore , reducing the source/ drain resistance has become an important issue for ultra-thin FDSOI MOS devices.

In order to suppress and avoid the risk of siliciding the whole silicon film, a new technology to form elevated source/drain structure is brought forward firstly. With this technology, the problem of high source/drain series resistance can be resolved and enough thickness of silicon was provided to form TiSi<sub>2</sub>.

Received 3 June 2004 , revised manuscript received 2 December 2004

Lian Jun male ,was born in 1976 ,PhD candidate. His main research field is fully-depleted SOI CMOS devices and circuits. Email :junlian @ hotmail.com

Hai Chaohe male, was born in 1942, professor. His main research fields are SOI SRAM, radiation hardening process technologies, and Bi-CMOS devices and circuits.

# 2 Device fabrication

#### 2.1 Fabrication flow

The SIMOX wafers used were fabricated by Shanghai Simgui Technology Co. Ltd. The SIMOX wafer had buried oxide layer with the thickness of 370nm and SOI film layer with the thickness of 190nm.

Until the gate formation ,the process technology is conventional CMOS technology. The process flow is described as below.

The SOI film thickness was thinned down to ~ 50nm by two-step oxidation and oxide strip. The isolation technology used is LOCOS. BF2 + was implanted with energy of 40keV and dose of 4  $\times 10^{12}$ cm<sup>-2</sup> as nMOSFETs V<sub>T</sub> adjust implant ,and 40keV 6  $\times 10^{11}$  cm<sup>-2</sup> as pMOSFETs V<sub>T</sub> adjust implant. After growing a 12nm gate oxide, 300nm polysilicon layer was deposited.  $P^+$  with energy of 70keV and dose of 8  $\times 10^{15}$  cm<sup>-2</sup> was implanted into the polysilicon. The gate was patterned and etched to 0.35 ~ 1.  $2\mu$ m range. Then phosphorus with energy of 10keV and dose of 3  $\times 10^{13}$  cm<sup>-2</sup> was implanted in nMOSFETs.BF2<sup>+</sup> with energy of 10keV and dose of 3  $\times 10^{13}$  cm<sup>-2</sup> was implanted in pMOSFETs. The purpose of the implantation is to form LDD structure.

### 2.2 Novel technology

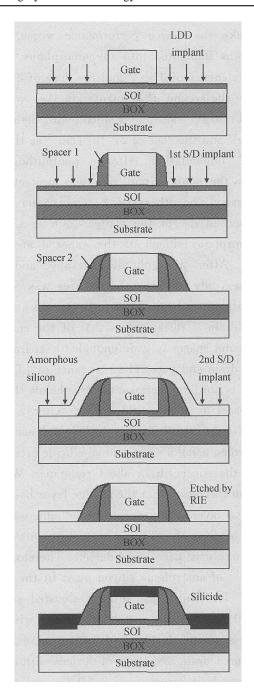

The next process is to produce elevated source/drain structure by a novel technology. Figure 1 shows an abbreviated process flow of thinfilm FDSOI device with elevated source/drain structure. After LDD implantation, 180nm thick TEOS oxide was deposited. The first spacer was formed by RIE process. Then  $BF_2^+$  was implanted with energy of 40keV and dose of  $2 \times 10^{15}$  cm<sup>-2</sup> as the first p<sup>+</sup> implantation. As<sup>+</sup> was implanted with energy of 60keV and dose of  $2 \times 10^{15}$  cm<sup>-2</sup> as the first n<sup>+</sup> implantation. Second TEOS oxide with the thickness of 300nm was deposited after first

Fig. 1 Process flow of novel technology to form elevated sourced/ drain structure

source/ drain implantation. After the second spacer formation, a layer of amorphous silicon with the thickness of 45nm was deposited by LPCVD. This layer of amorphous silicon is to form the elevated source/ drain structure. The reason of not using polysilicon is the deposition temperature of amorphous silicon is much lower than that of polysilicon. This reduces the dopant diffusion effect that can make the device performance worse. Then BF2<sup>+</sup> was implanted into the amorphous silicon with the energy of 35keV and the dose of 2  $\times 10^{15}$  $cm^{-2}$  as the second  $p^+$  implantation. As<sup>+</sup> was implanted into the amorphous silicon with the energy of 50keV and the dose of 2  $\times 10^{15}$ /cm<sup>-2</sup> as the second  $n^+$  implantation. After a photolithography process, the source/drain area was protected by photoresist. The other area of amorphous silicon was exposed except the source/drain area. Then the amorphous silicon of the exposed area was etched. After the photolithography and RIE processes, only the source/drain area was covered by amorphous silicon. Therefore, the thickness of source/drain is thicker than that of the channel. The second spacer is wide enough to separate the source/ drain and gate. The resistance of LDD extension is not large because the area below the second spacer is  $n^+$  or  $p^+$  region. After a RTA process, 30nm thick Ti was deposited. Then TiSi2 was formed using a conventional silicide process to reduce the source/drain sheet resistance. We can see from the figure that the silicide layer has eaten some SOI layer. The purpose is to eliminate the interface between the SOI and the amorphous silicon since there may have some defects. Therefore, the thickness of amorphous silicon must fit the thickness of Ti. The device without elevated source/ drain structure cannot supply the silicon with that thickness, so the thickness of Ti is around 20nm. The source/ drain resistance of devices with elevated source/drain structure is 3.8 / , and that of devices without elevated source/drain structure and 20nm thick Ti to form silicide is 5.8 / .

### **3** Discussion

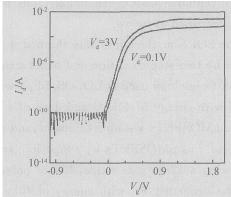

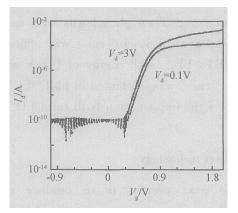

Figures 2 and 3 show the subthreshold characteristics of nMOSFETs and pMOSFETs, respectively. The gate length is 0. 35µm, the gate oxide thickness is 12nm. The channel dopant of nMOS-FETs(pMOSFETs) is  $BF_2^+$  with concentration of 4 ×10<sup>12</sup> cm<sup>-2</sup> (6 ×10<sup>11</sup> cm<sup>-2</sup>). It is obviously that the both nMOSFETs and pMOSFETs have quasi-ideal subthreshold properties; the subthreshold slope of nMOSFETs is 65 mV/ decade, while that of pMOSFETs is 69 mV/ decade. When the silicon thin-film enters into the fully-depleted region, its subthreshold slope is much better with value close to the ideal case- (kT/q) (ln10) mV/ decade due to the buried oxide isolation between the channel and the grounded substrate. Furthermore, we can see from the Figs. 2 and 3 that the DIBL effect is very little in either nMOSFETs or pMOSFETs.

Fig. 2 Subthreshold characteristics of nMOSFETs

Fig. 3 Subthreshold characteristics of pMOSFETs

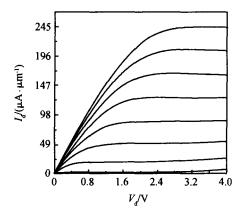

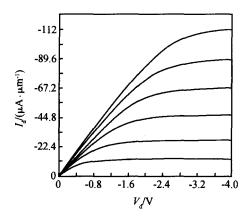

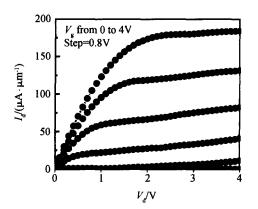

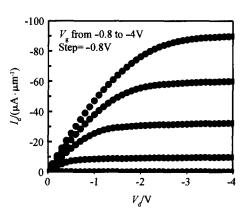

The comparison of saturation currents between elevated source/ drain devices and normal devices is shown in Figs.  $4 \sim 7$ . In this case, we use 1. 2µm gate length devices because we have no 0. 35µm devices experiments results before. The gate oxide thickness is 12nm, too. The channel dopant and concentration of nMOSFETs and pMOS-FETs are same with that of the 0. 35µm gate length devices. The processes of the two kinds of

Fig. 4 Output characteristics of 1. 2µm nMOSFETs with elevated source/ drain structure

Fig. 5 Output characteristics of 1. 2µm pMOSFETs with elevated source/ drain structure

Fig. 6 Output characteristics of 1. 2µm nMOSFETs without elevated source/ drain structure

devices are almost same except the processes to form elevated source/drain structure. The saturation current of nMOSFETs was increased by 32 % with elevated source/drain structure, while the sat-

Fig. 7 Output characteristics of 1. 2µm pMOSFETs without elevated source/ drain structure

uration current of pMOSFETs was increased by 24 %. Using the elevated source/ drain structure by novel process technology, the drain current has been improved substantially.

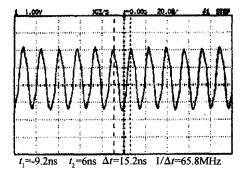

Figure 8 shows the propagation delay of 101stage thin-film FDSOI CMOS ring oscillator. The per-stage propagation delay of 101-stage SOI CMOS ring oscillator is 75ps with 3V supply voltage. The speed of FDSOI CMOS circuits is faster than that of partially-depleted SOI CMOS circuits and bulk circuits due to high mobility, high transconductance, and low parasitical capacitance.

Fig. 8 Propagation delay of 101-stage FDSOI CMOS ring oscillator

## 4 Conclusion

We have successfully fabricated the thin-film FDSOI devices with elevated source/drain structure. The novel technology to form elevated source/drain structure is brought forward first. Both nMOSFETs and pMOSFETs have quasi-ideal subthreshold properties. The DIBL effect of them is little. The saturation current is improved substantially with the elevated source/drain structure. The per-stage propagation delay of 101-stage FD-SOI CMOS ring oscillator is 75ps with 3V supply voltage.

#### References

- Bagchi S, Grant J M, Chen J, et al. Fully depleted SOI devices with TiN gate and elevated source-drain structure. IEEE International SOI Conference, 2000:56

- [2] Liu Xinyu, Sun Haifeng, Liu Hongmin, et al. Fully depleted CMOS/ SOI technology. Chinese Journal of Semiconductors,

2003,24(1):104(in Chinese)[刘新宇,孙海峰,刘洪民,等.全 耗尽 CMOS/SOI工艺.半导体学报,2003,24(1):104]

- [3] Veeraraghavan S, Fossum J G. Short-channel effects in SOI MOSFET 's. IEEE Trans Electron Devices, 1989, 36:522

- [4] Wang Wenping, Huang Ru, Zhang Guoyan. Structure optimization analysis of sub-100nm SOI device. Chinese Journal of Semiconductors, 2003, 24(9):986(in Chinese)[王文平,黄如, 张国艳.亚100nm SOI器件的结构优化分析.半导体学报, 2003, 24(9):986]

- [5] Colinge J P. Reduction of floating substrate effect in thin-film SOI MOSFET 's. IEEE Trans Electron Devices ,1995 ,42:187

- [6] Chau R, Kavalieros J, Doyle B, et al. A 50nm depleted substrate CMOS transistor (DST). IEDM Tech Digest, 2001:621

- [7] Su L T, Sherony M J, Hu H, et al. Optimization of series resistance in sub-0. 2-µm SOI MOSFET 's. IEDM Tech Digest, 1993:723

# 采用新的抬高源漏工艺技术制作的全耗尽 SOI CMOS 器件和电路

### 连 军 海潮和

(中国科学院微电子研究所,北京 100029)

摘要:采用新的工艺技术,成功研制了具有抬高源漏结构的薄膜全耗尽 SOI CMOS 器件.详细阐述了其中的关键 工艺技术.器件具有接近理想的亚阈值特性,nMOSFETs 和 pMOSFETs 的亚阈值斜率分别为 65 和 69mV/dec.采 用抬高源漏结构的 1. 2µm nMOSFETs 的饱和电流提高了 32 %,pMOSFETs 的饱和电流提高了 24 %.在 3V 工作 电压下 101 级环形振荡器电路的单级门延迟为 75ps.

关键词: FDSOI; CMOS; 抬高源漏

EEACC: 2560

中图分类号: TN386 文献标识码: A 文章编号: 0253-4177(2005)04-0672-05

连 军 男,1976年出生,博士研究生,主要从事全耗尽 SOI CMOS 器件及电路的研究工作. Email :junlian @hotmail.com 海潮和 男,1942年出生,研究员,博士生导师,主要从事 SOI SRAM、抗辐射工艺以及 BiCMOS 器件和电路的研制工作. 2004-06-03 收到,2004-12-02 定稿 ©200