CHINESE JOURNAL OF SEMICONDUCTORS

# A VHF PECVD Micro-Crystalline Silicon Bottom Gate TFT with a Thin Incubation Layer \*

Li Juan<sup>1</sup>, Zhao Shuyun<sup>1</sup>, Liu Jianping<sup>1</sup>, Wu Chunya<sup>1</sup>, Zhang Xiaodan<sup>1</sup>, Meng Zhiguo<sup>1</sup>, Zhao Ying<sup>1</sup>, Xiong Shaozhen<sup>1</sup>, Zhang Lizhu<sup>2</sup>, and Jang Jin<sup>3</sup>

(1 Institute of Photo Electronic Thin Film Devices and Technology, School of Information, Key Laboratory for Photoelectronic Thin Film Devices and Technology of Tianjin, Nankai University, Tianjin 300071, China)

(2 Tianjin Institute of Mechanic and Electric Professional Technology, Tianjin 300131, China)

(3 A dvanced Display Research Center, Department of Information Display,

Kyung Hee University, Dong daemoomku, Seoul 130-701, Korea)

**Abstract:** The incubation layer with amorphous structure between the substrate and crystalline layer may obviously affect the performance for a microcrystalline Si thin film transistor ( $\mu$ c Si TFT), especially for the bottom gate TFT (B G TFT). It is found that decreasing the ratio of Si H<sub>4</sub>/ (H<sub>2</sub> + Si H<sub>4</sub>) is an effective way to decrease the incubation layer thickness of  $\mu$ c Si directly deposited by VHF PECVD without any further thermal or laser treatment. Based on the  $\mu$ c Si with a thin incubation layer, the B G TFT with Al/SiN<sub>x</sub>/ $\mu$ c Si/n<sup>+</sup>- $\mu$ c Si/Al structure is fabricated. The ratio of on-state current to off-state current is up to  $10^6$ , the mobility is around 0. 7cm<sup>2</sup>/ (V · s), and the threshold voltage is about 5V.

Key words: microcrystalline silicon; incubation layer; silicon concentration; bottom gate µc-Si TFT

PACC: 7360; 7360F; 7390

**CLC number:** TN321<sup>+</sup>. 5 **Document code:** A **Article ID:** 0253-4177 (2005) 06-1121-05

#### 1 Introduction

With the development of new panel display technology, such as AMOLED, thin film transistors with good performance and low cost are required. Recently, intrinsic µc-Si (microcrystalline silicon) without any further treatment by thermal or laser annealing is extremely appealing due to its higher mobility and better stability than amorphous sili-

con (a-Si) TFT and lower cost than polycrystalline (poly-Si) TFT<sup>[1,2]</sup>. Compared with the mature a-Si TFT technology ,µc-Si TFT could be used in higher-resolution displays ,or it would allow the use of smaller size TFT to increase optical aperture. Furthermore , the fabrication process of bottom-gate (BG) µc-Si TFTs is almost compatible with that of the a-Si TFTs ,that is to say ,the same product line with which today produce a-Si TFT could easily be switched to BG µc-Si TFT production. Generally

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (Nos. 60437030,60077011, and 69907002), the National High Technology Research and Development Program of China (No. 2002AA303261), and the Natural Science Fundation of Tianjin (No. 02360211)

Li Juan female ,was born in 1976 ,PhD candidate. Her research work focuses on thin film opto-electronic devices and thin film transistors. Email: 1j1018 @nankai.edu.cn

Zhao Shuyun female, was born in 1981, master candidate. Her work focuses on micro-electronics and solid physics. Email: shuyunzhao @sina.com.cn

speaking ,technology of a-Si TFTs is relatively mature and the research for poly-Si TFTs also has been developed widely and much novel technologies<sup>[3]</sup> have been applied. However ,research for µc-Si TFT is still in the beginning steps ,its performance is far from perfect and the factors that affect its characteristics are complex. One of them is that an incubation layer with amorphous structure clings on top of the substrate though the rest of the film may exhibit a high crystallinity<sup>[4-6]</sup>. The incubation layer may obviously affect the performance for TFT ,especially for BG µc-Si TFT. In this paper ,the studies on the incubation layer are presented and the performance of a BG µc-Si TFT with a thin incubation layer is shown.

# 2 Experimental details

µc-Si thin films were deposited by VHF-PECVD with the active frequency of 60MHz, the silicon concentration diluted by hydrogen (S<sub>c</sub> =  $Si H_4/(Si H_4 + H_2)$ ) was varied from 0.67% to 8 %, film thickness changed from 10nm to 1000nm and the pressure and substrate temperature were fixed at 120Pa and 220 , respectively. The same excited power, 25W, was applied for all samples. The crystallinity of  $\mu c$ -Si is measured by Raman scattering using a 632. 8nm He-Ne laser. Here ,the crystalline volume fraction  $(X_c)$  was used to describe the crystalline degree of the films. As well known, the  $X_c$  of the sample can be deduced from its Raman scattering spectra by the ratio of  $X_c$  =  $I_c/(I_c + I_a) = (I_{520} + I_{510})/(I_{520} + I_{510} + I_{480})$ , where Ic is the crystalline intensity peak at 520 and 510, and I<sub>a</sub> is the amorphous intensity at 480cm<sup>-1</sup>. Conduction activation energy (Ea) was measured utilizing the equipment designed by ourselves. The film thickness is measured by an AMBIOS Technology Inc. XP-2<sup>TM</sup> Profilometer with an ability to measure precision step heights from under 10nm to as large as 100µm and to measure micro-roughness, with 0. 1nm resolution over short distance, as well as waviness.

For the fabrication of the BG µc-Si TFT, a four-mask process with specially designed layout was used. First, we thermally evaporated Al, and patterned it using reactive ion etching to form the gate electrode. Then, deposited 200nm SiNx as the gate insulator. Next ,160nm of intrinsic µc-Si as the channel layer and 50 ~ 100nm of n<sup>+</sup> µc-Si as the contact layer were grown on the SiN<sub>x</sub> substrate orderly without breaking vacuum. Afterwards, the channel was defined by photolithography and wet etching, then Al was thermally evaporated and patterned by wet etching to form the source and drain electrodes. The active channel was configurated by conventional back-channel etching. Finally, we opened the contact holes to the TFT gate electrode.

#### 3 Results and discussion

#### 3.1 Incubation layer

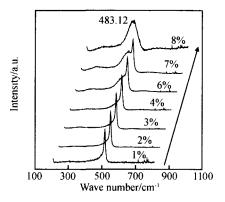

To achieve a good  $\mu$ c-Si TFT, crystallinity of the  $\mu$ c-Si film is an essential factor. Figure 1 shows the Raman spectra of the 1000nm thick  $\mu$ c-Si film with increasing hydrogen dilution under other identical deposition conditions. It can be observed that the Raman spectra peak gradually changes from an amorphous band at  $480 \text{cm}^{-1}$  to the crystal band at  $520 \text{cm}^{-1}$  above a certain threshold dilution ratio around the  $S_c$  of 6 %. However, it is different when a thinner ( < 0.  $2\mu$ m)  $\mu$ c-Si is used as the TFT chan-

Fig. 1 Raman spectra of the 1000nm µc-Si film

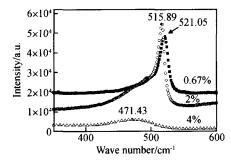

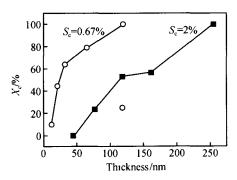

nel as shown in Fig. 2. For the thinner  $\mu$ c-Si film, the phase transition point is around 4% of  $S_c$ . This could be attributed to the effect of the initial amorphous layer that is called the incubation layer, existing between the substrate and the crystalline layer. Apparently, the thinner the  $\mu$ c-Si film is, the more obvious the effect of the incubation layer is, which will make the  $\mu$ c-Si TFT, especially the bottom gate TFT, show characteristics of an a-Si TFT instead of the advantages of a  $\mu$ c-Si TFT. According to our experiment results, decreasing  $S_c$  is an effective way to thin the incubation layer.

Fig. 2 Raman spectra of the 160nm  $\mu$ c-Si film with variable  $S_c$

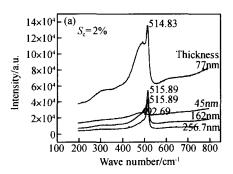

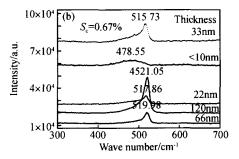

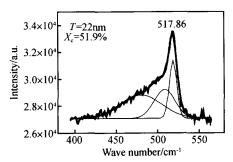

When  $S_c = 4$  %, the thickness of the incubation layer is above 200nm, which is thicker than the channel thickness of  $\mu$ c-Si TFT, while it is down to  $60 \sim 70$ nm for  $S_c = 2$  % and becomes thinner (about 20nm) for  $S_c = 0$ . 67 % as shown in Figs. 3 (a) and (b), respectively. From Fig. 4, it is important to note that for  $\mu$ c-Si film deposited at  $S_c = 0$ . 67 %, the  $X_c$  of its 20nm incubation layer is nearly 50 %, which can be seen in Fig. 5. Increasing the film thickness,  $X_c$  tends to rise slowly.  $X_c$  of the  $\mu$ c-Si film deposited at  $S_c = 2$  % with 60nm incubation layer is nearly 20 % and shows the same trendency.

Thus far, we have effectively thinned the initial amorphous incubation layer in the  $\mu$ c-Si film by simply using high H dilution of Si H<sub>4</sub>. However, the drawback of too high an H dilution is that it results in a lower deposition rate and lower activation energy ( $E_a$ ). The deposition rate of a  $\mu$ c-Si film deposited at  $S_c = 0.67\%$ , 25W, and 120Pa is only 0.968nm/s and the  $E_a$  is about 0.1eV. The film

Fig. 3 Raman spectra for  $\mu$ c Si film deposited at  $S_c = 2\%$  (a) and 0. 67 % (b) with variable film thickness

Fig. 4 Variation of  $X_c$  with the thickness of  $\mu$ c-Si thin film at different silicon concentration

Fig. 5 Analysis of Raman for 22nm at  $S_c = 0.67 \%$

with so low an  $E_a$  can not be used to make a TFT. The drastic decreasing of  $E_a$  may be caused by the oxygen contamination. For the growth of µc-Si, atomic hydrogen reaching the film-growing surface breaks weak Si -Si bonds in the amorphous network structure, leading to a removal of Si atoms weakly bonded to another Si. This site is replaced with a new film precursor Si H<sub>3</sub>, creating rigid and strong Si -Si bonds, giving rise to an ordered structure<sup>[6]</sup>. Under too high an H dilution condition, the role of the atomic hydrogen etching is too great, which leads to much void in the µc-Si film between the columnar grains, and then oxygen penetration into it<sup>[7]</sup>. Strong oxygen contamination makes the threshold voltage of the TFT negative and gives rise to a large leakage current as well as the deterioration of gate modulation effect. In addition, Schropp et al. has found that oxygen incorporation increases linearly with decreasing deposition rate<sup>[8]</sup>. Therefore from the view of an oxygen contamination point, the Sc should not be too low.

Considering the incubation layer thickness and the oxygen contamination, we try to choose the  $S_c$  for the  $\mu$ c-Si film used as the TFT channel as 2%. In this case, its  $E_a$  is 0.45eV and the thickness of the incubation layer is about 60nm ( $X_c$  of the incubation layer is about 30%), which may be relatively suitable for the BG  $\mu$ c-Si TFT. The optimum structure has to be studied further in the future.

#### 3.2 BG \u2209c-Si TFT

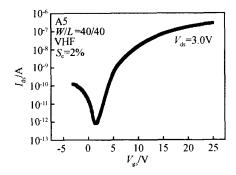

Bottom gate TFTs were fabricated with the  $\mu$ c-Si deposited at an  $S_c$  of 2%. The almost same fabrication processes as those for making a-Si TFT were employed to fabricate a  $\mu$ c-Si TFT. The transfer characteristic curve of the resulted TFT without any other treatment and LDD structure is shown in Fig. 6. The ratio of on-state current to the off-state current ( $I_{on}/I_{off}$ ) is up to  $10^6$ , the mobility is around 0.  $7 \text{cm}^2/(\text{V} \cdot \text{s})$ , and the threshold voltage is about 5V. The TFT characteristics are comparable to those of the  $\mu$ c-Si TFT reported by other research groups. Further optimization, such as the  $\mu$ c-Si grain size, the film density, and interface treatment, is still required to make the BG  $\mu$ c-Si

TFT show more obvious advantages than a-Si TFT.

Fig. 6 Transfer characteristics of µc-Si TFT

### 4 Conclusion

Decreasing the silicon concentration is an effective way to achieve a µc-Si film with an ultrathin (< 20nm) incubation layer or much less by VHF-PECVD. However, too high an H dilution leads to too a low deposition rate and serious oxygen contamination. From the view of the above two points, a µc-Si film deposited at Sc of 2 % is suitable for the application of the bottom gate TFT and this TFT without any other treatment and LDD structure shows relatively good performances. Nevertheless, further optimization of the µc-Si film is still required to achieve a better bottom gate µc-Si TFT.

## References

- [1] Schropp R E I, Stannowski B, Rath J K. New challenges in thin film transistor (TFT) research. Journal of Non Crystalline Solids, 2002, 299 ~ 302:1304

- [2] Wu Chunya, Meng Zhiguo, Xiong Shaozhen. A 2.1-inch AMOLED display based on metal-induced laterally crystallized polycrystalline silicon technology. Proceeding of The Symposium on Information Display, 2004

- [3] Zhang Shengdong, Han Ruqi, Wang Yangyuan, et al. A novel ultra-thin channel poly-Si TFT technology. Chinese Journal of Semiconductors, 2000, 21(4):317 (in Chinese) [张盛东,韩汝琦,王阳元,等. 多晶硅超薄沟道薄膜晶体管研制. 半导体学报, 2000, 21(4):317]

- [4] Zhou Jianghuai ,Ikuta K , Yasudab T ,et al. Control of crystallinity of microcrystalline silicon film grown on insulating glass substrates. Journal of Non-Crystalline Solids , 1998 , 227 ~ 230:857

- [5] Meiling H, Brockhoff A M, Rath J K, et al. Hydrogenated a-morphous and polycrystalline silicon TFTs by hot-wire CVD. Journal of Non-Crystalline Solids, 1998, 227 ~ 230:1202

- [6] Fontcuberta i Morral A ,Bertomeu J ,Roca i Cabarrocas P ,et al. The role of hydrogen in the formation of microcrystalline silicon. Materials Science and Engineering ,2000 ,B69/70:559

- [7] Gupta N D, Chaudhuri P. Effect of oxygen contamination on

- the properties of the silicon hydrogen alloy materials deposited under conditions near the microcrystalline silicon formation regine. Journal of Non-Crystalline Solids ,2001 ,289:168

- [8] Schropp R E I, Alkemade P F A, Rath J K, et al. Poly-silicon lms with low impurity concentration made by hot wire chemical vapour deposition. Solar Energy Materials & Solar Cells, 2001,65:541

# 薄起始层的 VHF PECVD 底栅微晶硅薄膜晶体管 \*

李 娟' 赵淑云' 刘建平' 吴春亚' 张晓丹' 孟志国' 赵 颖' 熊绍珍' 张丽珠<sup>2</sup> 张 震<sup>3</sup>

(1 南开大学光电子研究所,天津市光电子薄膜器件与技术重点实验室,天津 300071) (2 天津机电职业技术学院,天津 300131)

(3 庆熙大学信息显示系 先进显示研究中心, 汉城 130-701, 韩国)

摘要: 对微晶硅薄膜晶体管 ,尤其对底栅型晶体管 ,在衬底和晶化层间存在一层非晶相起始层 ,这将严重影响器件性能. 文中采用降低硅烷浓度的方法简便有效地减薄了用超高频化学气相法直接沉积的微晶硅薄膜起始层的厚度 ,得到起始层厚度小于 20nm 的微晶硅薄膜. 在硅烷浓度为 2 %的条件下采用四版工艺制备了具有  $Al/SiN_x/\mu_{CC}Si/n^+-\mu_{CC}Si/Al$  结构的底栅微晶硅 TFT ,其开关比 (  $I_{on}/I_{off}$  )达到  $10^6$  ,场效应迁移率为  $0.7\,cm^2/(V\cdot s)$  ,阈值电压为 5V 左右.

关键词:微晶硅;起始层;硅烷浓度;底栅薄膜晶体管

**PACC:** 7360; 7360F; 7390

中图分类号: TN321<sup>+</sup>.5 文献标识码: A 文章编号: 0253-4177(2005)06-1121-05

<sup>\*</sup>国家自然科学基金(批准号:60437030,60077011和69907002),国家高技术研究发展计划(批准号:2002AA303261)和天津市自然科学基金 (批准号:02360211)资助项目

李 娟 女 ,1976 出生 ,博士研究生 ,从事薄膜光电子器件技术和薄膜晶体管的研究. Email :lj1018 @nankai. edu. cn

赵淑云 女、1976年出生、硕士研究生、专业为微电子学和固体物理、Email:shuyunzhao @sina.com.cn

刘建平 男,1980年出生,硕士研究生,专业为平板显示. Email:liujianping @sina.com.cn