Supplement Dec., 2006

# 集成抗 ESD 二极管的 SOI LIGBT/LDMOS 器件结构及其制作方法\*

张海鹏 $^{1,\dagger}$  汪  $\%^2$  孙玲玲 $^3$  高明煜 $^1$  李文钧 $^3$  吕幼华 $^1$  刘国华 $^1$  汪  $洁^1$

(1 杭州电子科技大学电子信息学院,杭州 310018) (2 浙江万里学院计算机科学与信息学院,宁波 315100) (3 杭州电子科技大学电子信息学院 IC CAD 研究所,杭州 310018)

摘要:为探索与国内 VLSI 制造工艺兼容的新型 SOI LIGBT/LDMOS 器件与 PIC 的设计理论和工艺实现方法,首次提出含有抗 ESD 二极管的集成 SOI LIGBT/LDMOS 器件截面结构和版图结构,并根据器件结构给出了阻性负载时器件的大信号等效电路.探讨了该结构器件的 VLSI 工艺实现方法,设计了工艺流程.讨论了设计抗 ESD 二极管相关参数所需考虑的主要因素,并给出了结构实现的工艺控制要求.

关键词: ESD; SOI; LIGBT/LDMOS; 器件结构; 工艺; PIC

**EEACC**: 2570

中图分类号: TN432 文献标识码: A 文章编号: 0253-4177(2006)S0-0279-04

#### 1 引言

1985 年以来,高频功率半导体器件及其集成电路(PIC)已占国际功率半导体产业总产值的 3/4 左右,仅其中的功率 IC 一项就占约 45%的份额.该转变主要是因为,这些器件或 IC 能以更高频率工作,从而更节能、节材,能大幅减小设备体积和重量.尤其是基于绝缘层上硅(SOI)横向绝缘栅双极晶体管/横向双扩散或者双注入金属氧化物半导体场效应管(LIGBT/LDMOS)的高集成度单片功率集成系统(PSOC),它能把传感器、信号处理电路、接口电路、功率器件和驱动控制电路等集成在单个 SOI 芯片上,使其具有按照负载要求精密调节输出和按照过热、过压、过流、抗静电(ESD)等情况进行自我保护的智能功能.因此国际专家把它的发展誉为第二次电子学革命[1].

目前,我国已经掌握了部分 IGBT 器件的核心设计和制造技术,由于 IGBT 制造工艺水平和材料制造水平还与国外有很大差距,器件性能不够理想,生产线因故闲置,以至于国内市场使用的 IGBT 器件绝大部分仍需依靠国外进口[2].然而,我国集成电路制造水平已经达到 0.18~0.9 µm,接近国际先进水平.以上海新傲公司为首的企业和科研机构,开展新型的集成电路基础材料——SOI 材料研究、制造

和销售 SOI,使我国成为国际上少数 SOI 圆片生产国之一. 2002 年 7 月,新傲公司开始生产  $100 \sim 150$ mm 注氧隔离 SOI 圆片,经中美两国技术检测,性能指标达到国际先进水平,已批量投放市场<sup>[3]</sup>.

SOI 技术以其理想的全介质隔离性能、相对简单的隔离工艺、显著减弱的寄生效应,使其速度高、功耗低、耐高温运行,便于多器件、高密度、小型化和三维智能功率集成,且与互补金属-氧化物-半导体(CMOS)超大规模集成电路(VLSI)制造工艺兼容而倍受瞩目.因此,我们试图探索与国内 VLSI 制造工艺兼容的治型 SOI LIGBT/LDMOS 器件与 PIC的设计理论和工艺实现方法.有关具有抗 ESD的 SOI LIGBT/LDMOS 器件的研究至今未见报道.所以首先研究了集成抗 ESD 二极管的 SOI LIGBT/LDMOS 器件单元版图结构和截面结构、阻性负载时器件的大信号等效电路、器件的工艺实现方法、部分关键结构的设计考虑与工艺控制要求等.

## 2 集成抗 ESD 二极管的 SOI LIGBT/ LDMOS 器件单元结构

SOI LIGBT/LDMOS 器件含有 MOS 结构,在 封装、运输、装配及使用过程中,容易引起千伏以上 的高压静电.如果没有钳位二极管保护,由于栅氧化 层很薄而易被这种高压静电击穿造成器件永久失

<sup>\*</sup>国家自然科学基金(批准号:60306003)及浙江省自然科学基金(批准号:y104599)资助项目

<sup>†</sup>通信作者.Email:islotus@163.com

效.这种由于高压静电引起栅击穿所造成的器件永久失效称为静电损伤(ESD).此外,与 SOI LDMOS 器件相比,如果没有栅极抗 ESD 二极管保护,由于通态时 SOI LIGBT 阳极向漂移区注入的大量少数载流子在器件关断过程中改变了器件内部的电势分布,引起控制栅区域电场集中,容易导致 SOI LIGBT 器件过早失效<sup>[4]</sup>.目前,商业化的 SOI LIGBT/LDMOS 器件在使用中需要外接分立稳压二极管加以保护,这样就增加了体积、重量和成本.

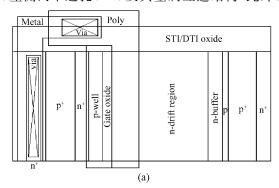

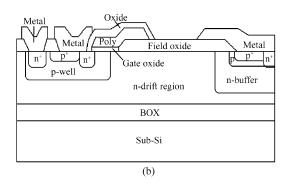

进一步研究发现,为了改善 SOI LIGBT 器件 栅极抗 ESD 特性,可以在器件的源/体引出区远离源掺杂区一侧增加一个与源区掺杂类型相同的区域,并将该区域的电极引出金属与多晶硅栅极相连,就可以实现集成栅极抗静电损伤二极管的 SOI LIGBT/LDMOS 器件结构,而且不需要增加任何工艺步骤,只是稍微增加了版图设计复杂度,器件单元结构示意如图 1 所示. 其中,为了便于显示,在图 1 (a)中未给出与图 1(b)相对应的场氧层(field oxide)和源/漏区金属层(metal)的结构版图示意,但是给出了集成栅极抗 ESD 二极管阴极引出金属及其与多晶硅栅极之间的互连结构版图示意,见图 1 (a)左侧两个通孔(via)及其金属互连结构.此外,在

图 1 集成栅极抗 ESD 二极管的 SOI LIGBT/LDMOS 器件单元结构 (a)版图结构;(b)截面结构

Fig. 1 Cell structure diagram of SOI LIGBT/LDMOS integrated with anti-ESD diode (a) Mask structure; (b) Cross section structure

图 1(a)中还给出了器件单元之间的沟槽隔离氧化层(STI/DTI oxide)结构版图示意. 如果将阳极区的  $p,p^+$ 掺杂区域代之以  $n^+$ 掺杂,就可以得到相应的 SOI LDMOS 器件.

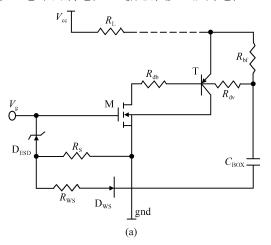

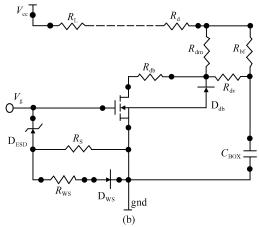

这种集成栅极抗 ESD 二极管的 SOI LIGBT/LDMOS 器件在阻性负载情况下的大信号简化等效电路如图 2 所示. 其中, M 是由  $n^+$  源区、p-well 体区、poly 栅区和  $n^-$ -drift 漏区构成的 nMOSFET, T是由 p-well 集电区、 $n^-$ -drift + n-buffer 基区和  $p^+$  发射区构成的 pnp 型双极结型晶体管 (BJT), $p_{ESD}$  是集成栅极抗 ESD 二极管, $p_{WS}$  是 p-well 和  $p_{WS}$  是 p-well 和  $p_{WS}$  是原端, $p_{WS}$  是隐埋氧化层寄生电容, $p_{WS}$  是源端  $p_{WS}$  是以对接触电阻, $p_{WS}$  是 p-well 区横向电阻, $p_{WS}$  是 T 的基区等效电阻, $p_{WS}$  是 T 的基区到  $p_{WS}$  和  $p_{WS}$  是 T 的基区到  $p_{WS}$  和  $p_{WS}$  是 T 的基区到  $p_{WS}$  和  $p_{WS}$  是  $p_{WS}$  和  $p_{WS}$  和  $p_{WS}$  是  $p_{WS}$  和  $p_{W$

图 2 集成栅极抗 ESD 二极管的 SOI LIGBT (a)和 LDMOS (b)器件在阻性负载情况下的大信号简化等效电路

Fig. 2 Simplified big signal equivalent circuits of SOI LIGBT (a) and LDMOS (b) integrated with anti-ESD diode LDMOS

### 3 集成抗 ESD 二极管的 SOI LIGBT/ LDMOS 器件工艺实现

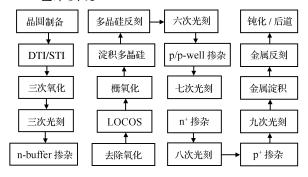

根据图 1 所示集成栅极抗 ESD 二极管的 SOI LIGBT/LDMOS 器件单元结构,设计其工艺实现方法与流程如图 3 所示. 其中,DTI 工艺与 STI 有些类似,有关 STI 工艺详见文献[5],有关局部氧化隔离(LOCOS)工艺详见文献[6]. 利用沟槽隔离工艺形成相互隔离的硅岛,每个硅岛分别用于制作 SOI LIGBT/LDMOS 器件或其驱动控制电路. LOCOS 工艺用来形成硅岛中的场氧层,也可以考虑采用 STI 工艺来实现.

图 3 集成抗 ESD 二极管的 SOI LIGBT/LDMOS 器件结构 工艺流程图

Fig. 3 Process flow of SOI LIGBT/LDMOS integrated with anti-ESD diode

### 4 集成抗 ESD 二极管结构的设计

根据 pn 结二极管反向击穿原理,对于单边突变  $n^+p$  结,其击穿电压近似由下式决定,

$$BV_{D} = \frac{\varepsilon_{r} \varepsilon_{0} E_{Cr}^{2}}{2 q N_{A}}$$

(1)

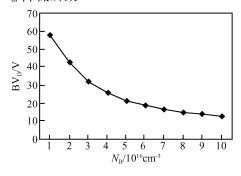

式中  $\varepsilon_r = 11.9$  是硅的介电常数;  $\varepsilon_0 = 8.854 \times 10^{-12}$  F/m 是真空介电常数;  $q = 1.602 \times 10^{-19}$  C 是电子电荷量. 当低掺杂一侧的掺杂浓度  $N \in [10^{16} \,\mathrm{cm}^{-3} \sim 5 \times 10^{17} \,\mathrm{cm}^{-3}]$ 范围时, 硅的临界雪崩击穿电场强度约为  $E_{\mathrm{Cr}} = (4 \sim 8) \times 10^5 \,\mathrm{V/cm}$ . 通过调整  $N_{\mathrm{A}}$  可以改变  $\mathrm{BV_D}$ , 如图 4 所示.

对于线性缓变 pn 结,其击穿电压近似由下式 决定,

$$BV_{D} = \frac{4E_{Cr}^{3/2}}{3} \sqrt{\frac{2\varepsilon_{r}\varepsilon_{0}}{q\alpha_{i}}}$$

(2)

由上式可见,通过降低线性缓变 pn 结掺杂浓度梯度降低最大电场强度  $E_m$ ,从而可以提高其击穿电压.而在条件相似情况下,硅双边突变 pn 结的击穿电压明显高于硅单边突变 pn 结的击穿电压,这是因为 pn 结耗尽区的电场分布变稀疏引起最大电场

强度  $E_{\rm m}$  降低所致.

图 4 硅单边突变 pn 结击穿电压与低掺杂侧掺杂浓度的关系 Fig. 4 Breakdown voltage of single side abrupt pn junction versus concentration of low doped side

抗 ESD 二极管的  $n^+$  区与 p-well 欧姆接触区的版图间距主要由这样几部分距离决定:(1)抗 ESD 二极管的横向最大耗尽层宽度;(2)抗 ESD 二极管  $n^+$  区的横向注入结深;(3) p-well 欧姆接触区的横向注入结深;(4)工艺控制裕量.

抗 ESD 二极管的 n<sup>+</sup> 区面积主要根据击穿瞬间放电电流、击穿瞬间散热和工艺控制裕量要求进行计算. 根据 SOI LIGBT/LDMOS 器件版图结构的不同,一个抗 ESD 二极管单元可能为相邻两个或多个 SOI LIGBT/LDMOS 器件单元所共用,所以进行抗 ESD 二极管的 n<sup>+</sup> 区面积设计时需要考虑共用 SOI LIGBT/LDMOS 器件单元的总体要求. 而且, 当一个抗 ESD 二极管单元可能为相邻两个或多个 SOI LIGBT/LDMOS 器件单元所共用时,版图设计的结果将与图 1 所示的结构有明显不同,处于边界的器件单元则差别不大.

# 5 集成抗 ESD 二极管结构的工艺控制要求

在 MOS 型半导体器件和集成电路制作中,栅氧化层绝大多数采用高质量热氧化  $SiO_2$ ,其临界击穿电场强度接近  $10^7$  V/cm,即 1 V/nm. 因此,对于常用的  $25\sim40$  nm 厚栅氧化层,其耐压在  $25\sim40$  V之间. 为了便于智能化功率集成,当器件处于工作状态时,栅极驱动电压一般取 5 V. 那么,为了确保 SOI LIGBT 器件不受 ESD 且能在有一定干扰情况下正常工作,要求抗 ESD 二极管的耐压至少是栅极驱动电压的 2 倍以上,即大于 10 V.

如果采用单边突变结,考虑到工艺控制裕量,根据(1)式可以推算出 p-well 的掺杂浓度不宜高于1.3×10<sup>17</sup> cm<sup>-3</sup>.为了改善 SOI LIGBT 器件抗可控硅闩锁效应能力,必须尽可能地减小 p-well 的横向电阻,这要求 p-well 的掺杂浓度尽可能高.为解决

这一矛盾,我们提出首先利用离子注入的通道效应,对 p-well 进行离子注入掺杂时在掺杂窗口的中心区域一定范围内加大深注入杂质离子剂量;然后在退火推进过程中令杂质离子在一定范围内再分布,这样可以在几乎不影响 p-well 表面掺杂浓度的情况下适当提高 p-well 内部的掺杂浓度,从而既可以保证抗 ESD 二极管的耐压、MOS 管的阈值电压和SOI LIGBT 器件的阻断耐压要求,又可以改善 SOI LIGBT 器件抗闩锁能力.

此外,在抗 ESD 二极管的 n<sup>+</sup> 区掺杂时,可以考虑采用氧化层掩膜注入形成杂质的缓变分布,这样就可以获得非突变 pn 结,从而可以降低对 p-well 表面掺杂浓度的要求,即 p-well 表面掺杂浓度可以比突变结时高一些,因此也可以缓解这一矛盾.不过这样会令工艺复杂性稍有增加.

#### 6 结束语

集成栅极抗 ESD 二极管的 SOI LIGBT/LD-MOS 器件结构实现、性能实现与设计复杂度约束、工艺复杂度约束、SOI LIGBT 器件其他性能的实现和芯片面积成本约束之间存在一定的矛盾关系.为了实现良好的性能,且不显著增加器件实现成本,有必要进一步细致和深入研究,并进行必要的仿真和实验.

#### 参考文献

- [1] Institute of Science & Technology of China [EB/OL]. Power Electronics Association: Standardization of key words in power semiconductor field is needed. http://www.cinic.org.cn/Article\_Show2.asp? ArticleID = 1820717, 2004.11. 23(in Chinese) [中国科学技术信息研究所.电力电子学会:功率半导体领域关键名词需要标准化.http://www.cinic.org.cn/Article Show2.asp? ArticleID = 1820717,2004.11.23]

- [2] Electrical Technology Association of China. Series of electrical high technologies(No. 6 fascicule). Beijing: Publishing House of Mechanic Industry, 2000(in Chinese)[电工高新技术丛书,第6分册.北京:机械工业出版社,2000]

- [3] General Office of Chinese Academy of Science. Promoting the development of new type SOI silicon materials of our country in leap mode. Briefing of experimental unit of knowledge innovation engineering of Chinese Academy of Science, 2003(in Chinese)[中国科学院办公厅. 新傲公司推进我国 SOI 新硅材料跳跃式发展. 中国科学院知识创新工程试点工作简报,2003]

- [4] Garner D M, Udrea E, Ensell G, et al. Failure mechanisms of SOI high-voltage LIGBTs and LDMOSes under unclamped inductive switching. IEEE ISPSD, 2001;335

- [5] Wang Xinzhu, Xu Qiuxia, Qian He, et al. Isolation technology of deep sub-micrometer——STI technology. Chinese Journal of Semiconductors, 2002,23(3);323(in Chinese)[王新柱,徐秋霞,钱鹤,等. 深亚微米隔离技术——STI 工艺. 半导体学报,2002,23(3):323]

- [6] Quirk M, Serda J. Semiconductor manufacturing technology.

Translated by Hang Z S, et al. Beijing; Publishing House of Electronics Industry, 2004

# Device Structure and Fabricating Method for SOI LIGBT/LDMOS Integrated with Anti-ESD Diode\*

Zhang Haipeng<sup>1,†</sup>, Wang Qin<sup>2</sup>, Sun Lingling<sup>3</sup>, Gao Mingyu<sup>1</sup>, Li Wenjun<sup>3</sup>, Lü Youhua<sup>1</sup>, Liu Guohua<sup>1</sup>, and Wang Jie<sup>1</sup>

(1 School of Electronics and Information, Hangzhou University of Electronics and Science Tecnology, Hangzhou 310018, China)

(2 Computer Science and Information Technology College, Zhejiang Wanli University, Ningbo 315100, China)

(3 IC CAD Institute, Hangzhou University of Electronics and Science Tecnology, Hangzhou 310018, China)

**Abstract:** To explore the way to realize SOI LIGBT/LDMOS devices and PIC with VLSI technology, the structure and fabricating method for the devices integrated with anti-ESD diode are presented, according to which the equivalent circuits at resistive load are given. Then the process flowchart is designed. The main factors which impact the design of parameters related to anti-ESD diode are discussed in details. At last, the requirements for process control are introduced simply.

**Key words:** ESD; SOI; LIGBT/LDMOS; device structure; technology; PIC **EEACC:** 2570

Article ID: 0253-4177(2006)\$0-0279-04

<sup>\*</sup> Project supported by the National Natural Science Foundation of China(No. 60306003) and the Natural Science Foundation of Zhejiang Province(No. y104599)

<sup>†</sup> Corresponding author. Email: islotus@163.com