## 硅基微纳光子器件制备工艺问题及解决方案\*

陈少武 居晓光 余和军 樊中朝 徐学俊 余余中

(中国科学院半导体研究所 集成光电子国家重点实验室, 北京 100083)

摘要:讨论了硅基微纳光子器件制备过程中涉及的几个关键工艺问题,包括:电子束/光学光刻的电子束/光学邻 近效应;纳米线光波导 ICP-RIE 刻蚀的侧壁粗糙问题;光栅及 MOS 绝缘栅氧化硅填充致密度问题. 这些问题可影 响器件的结构均匀性、波导传输损耗、光栅的散射损耗以及 MOS 绝缘栅的绝缘性能. 在分析实验结果的基础上,提 出了一些解决方案.

关键词: 硅基微纳光子器件; 电子束/光学邻近效应; ICP-RIE 刻蚀; 光波导侧壁粗糙度; CVD

EEACC: 2250; 2250E; 2250G

中图分类号: TN256 文献标识码:A 文章编号: 0253-4177(2007)S0-0568-04

#### 1 引言

在未来的全光网和光互连芯片中,分立的光器 件将被光子集成芯片(PIC)所取代,以谋求更全面 的功能集成、更大的传输带宽、更高的调制速率、更 低的损耗和功耗、更廉价的制备成本,以及更稳定可 靠的性能, 硅基光子学在近三年来取得了几项突破 性进展,如 Intel 成功研制出硅基高速电光调制器[1] 和 Raman 激光器<sup>[2]</sup>,使硅基光子学的发展上了一 个新的台阶. 硅将成为光子集成最为理想的平台, 硅 基光子时代已经来临.

SOI 纳米线波导是近几年来新出现的一种先讲 技术,其技术背景是当前 CMOS 加工线宽已经达到 65nm(实验室甚至达到 30nm),能够满足微纳光子 器件制备的一般要求. SOI 纳米线波导是指在 SOI 上形成的截面尺寸为纳米量级的光波导,其 Si 核心 层和  $SiO_2$  包层之间大的折射率差异( $\Delta n = 2$ )使得 SOI 纳米线波导对光场有很强的限制作用,并且在 光通信波段(1.3~1.55μm)仍然能够实现单模传 输.由于这种强的限制作用,波导的弯曲半径能够小 到几个微米量级,这就为波导器件的小型化和高密 度集成化提供了巨大的便利.同时,波导中传输的光 功率密度也会大大得到增强,由此还会出现一些在 弱场情况下不易出现的新性质,如受激 Raman 散 射(SRS)、四波混频(FWM)、双光子吸收(TPA)等 非线性光学效应,从而实现某些非线性光学器件. SOI 纳米线波导因其横截面尺寸小,能够有效降低 载流子的渡越时间,因而成为高速硅基调制器的发

展趋势[3].

硅基纳光子器件的制备工艺在很大程度上与目 前的微电子 CMOS 工艺兼容,但由于纳光子器件有 别于微电子器件的特殊要求,在某些关键工艺环节 仍然存在挑战.本文就我们在研制硅基光子晶体器 件和 MOS 高速电光调制器过程中遇到的一些工艺 问题做一个分析讨论,所涉及的具体工艺包括,电子 束/光学光刻的电子束/光学邻近效应:纳米线光波 导 ICP-RIE 刻蚀的侧壁粗糙问题; 光栅及 MOS 绝 缘栅氧化硅填充致密度问题,

#### 2 光学/电子束光刻的光学/电子束邻 诉效应

光学/电子束邻近效应主要发生在二维光子晶 体器件的光学/电子束光刻工艺过程中,首先讨论光 学邻近效应.因为光子晶体是一种超高密度周期性 结构,其特征尺寸接近紫外光刻的照射波长,由于光 波的衍射,光子晶体相邻小孔之间的影像在光刻时 会发生交叠. 因此,处在光子晶体中间部分的"中央" 小孔和那些处在光子晶体边缘部分的所谓"半隔离" 小孔的曝光情况就有所不同. 如果相邻小孔之间是 干涉相长,则光刻后"中央"小孔将比"半隔离"小孔 尺寸大;反之,如果相邻小孔之间是干涉相消,则光 刻后"中央"小孔将比"半隔离"小孔尺寸小.这就是 光学邻近效应(OPE). 光学邻近效应在均匀光子晶 体中不明显,只有在光子晶体的边缘部位,或者在光 子晶体微腔和线缺陷波导部位,"半隔离"小孔由于 在一个方向上缺乏相邻的小孔,而表现出邻近效应.

<sup>\*</sup>国家自然科学基金资助项目(批准号:60577044)

<sup>†</sup>通信作者. Email; swchen@semi.ac. cn

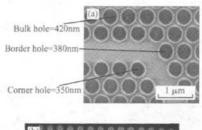

图 1(a)是比利时 Ghent 大学和 IMEC 制备的光子晶体弯曲波导<sup>[4]</sup>,线缺陷波导边上的"半隔离"小孔尺寸比"中央"小孔小 40nm,在波导转角处差别更大,达到 70nm.光子晶体波导器件的性能主要取决于线缺陷波导边上小孔的尺寸,邻近效应对器件的性能影响不可忽视,例如,对于 10nm 的小孔尺寸变化,光子禁带的中心波长可相差 20nm.

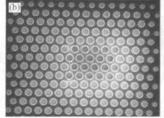

邻近效应不仅存在于光学光刻中,电子束光刻(EBL)时由于电子在光刻胶和衬底中的散射也会引起邻近效应.图 1(b)是我们用电子束直写光刻 EBL制备的二维光子晶体平板,边缘部分小孔尺寸明显小于中间小孔尺寸.但是由于电子束光刻是一个串行写人过程,不像基于并行写人的光学光刻那样存在干涉相长相消,电子束光刻邻近效应只是简单的非相干叠加,因此便于建立分析模型.而光学邻近效应由于相干本质而难于建立分析模型.

图 1 光学/电子束光刻的邻近效应 (a)比利时 Ghent 大学和 IMEC 用紫外光刻制备的光子晶体弯曲波导;(b)本文用电子束直写制备的光子晶体平板。

Fig. 1 Optical proximity effect (OPE) and proximity effect of e-beam lithography (EBL) (a) Photonic crystal waveguide bending fabricated by deep UV lithography by Ghent university and IMEC of Belgium; (b) Photonic crystal plate fabricated by e-beam lithography

校正光学邻近效应的办法是预先在光刻掩模版上给予"半隔离"小孔一定的尺寸偏置,以补偿光学邻近效应.显然,具体设计邻近效应补偿的掩模版需要定量了解邻近效应,方法是预先设计带有弯曲、微腔等结构的光子晶体波导器件,再改变其中"中央"小孔尺寸和"半隔离"小孔尺寸校正量,形成同一结构不同小孔尺寸的实验掩模版,然后进行光刻、刻蚀,根据实验数据即可得知正式掩模版所需的邻近

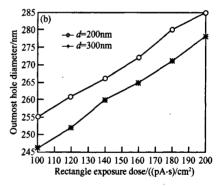

效应校正量. 校正电子束邻近效应的办法可用图 2 结合我们制备的具体光子晶体器件加以说明. 图 2 (a) 所示是光子晶体 Fabry-Perot 微腔,由光子晶体线缺陷波导中引入两组空气孔构成. 为了校正邻近效应,在晶格孔的两侧引入了两块大面积矩形图形,改变矩形同边缘晶格孔的距离,并改变矩形的电子束曝光剂量,进行多次实验,即可获得两组邻近效应校正数据,如图 2(b) 所示. 从实验曲线可知,要使边缘晶格孔的尺寸为 270nm,当矩形同边缘晶格孔的距离分别为 200 和 300nm 时,矩形的电子束曝光剂量应该分别取 158 和 180(pA·s)/cm².

图 2 电子束光刻邻近效应校正 (a) 光子晶体微腔及两侧补偿图形;(b) 邻近效应校正实验曲线

Fig. 2 Correction of proximity effect of e-beam lithography (a) Photonic crystal micro-cavity and compensation patterns at both sides; (b) Experimental curves for correction of proximity effect of EBL

## 3 ICP-RIE 刻蚀波导侧壁粗糙度

纳米线波导器件由于波导截面尺寸接近光波长量级,其传播模式受波导侧壁的散射影响相对于大截面波导更为显著.因此,为得到低传输损耗的纳米线波导,就必须采取有效措施降低 ICP-RIE 刻蚀波导形成的侧壁粗糙度.决定波导侧壁粗糙度的因素有:光刻掩模边缘状况,掩模-硅刻蚀选择比,ICP-RIE 刻蚀气体组分(决定侧壁钝化程度)和刻蚀速

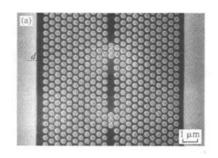

率等.边缘不平整的光刻掩模会将粗糙边缘直接转移到波导侧壁上,因此首先要确保光刻掩模的质量.在掩模边缘质量一定的情况下,通过降低偏压,可以降低掩模边缘的粗糙度向侧壁的传递.适当降低C4F8/SF6的比例,升高压强,可以起到减薄侧壁聚合物厚度、增加活性粒子对侧壁的刻蚀作用,在刻蚀建中可以有效减小从掩模边缘传递到侧壁的粗糙度,进而可以获得相对光滑的侧壁.进一步的侧壁光滑手段还包括波导表面热氧化处理以及湿法化学腐蚀.图3(a)是比利时 Ghent 大学和 IMEC 用紫外光刻制备的硅纳米线波导,图3(b)是我们用 EBL 加ICP-RIE 刻蚀工艺得到的 DBR 反射器.

图 3 (a) IMEC 用深紫外光刻制备的硅纳米线波导;(b) 用 EBL 加 ICP-RIE 刻蚀得到的 DBR 反射器

Fig. 3 (a) Silicon nanowire waveguide fabricated by deep UV lithography by IMEC of Belgium; (b) DBR reflector fabricated by EBL and ICP-RIE by us

### 4 CVD 窄槽沉积氧化硅

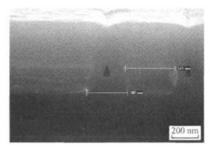

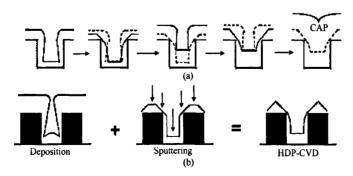

微纳光子器件制备工艺的另一个挑战就是在纳 米级的窄槽和小孔中填充致密无空腔的高质量 SiO<sub>2</sub> 层,例如 MOS 结构高质量栅氧层的形成以保 证有效的电学隔离,Si/SiO<sub>2</sub>-DBR 反射器 Si 槽中 SiO<sub>2</sub> 的沉积以保证低散射损耗,等离子体增强化学 气相沉积(PECVD)进行绝缘介质的填充对大于 0.8μm 的间隙具有良好的填孔效果,然而对小于 0.8μm 的间隙,用单步 PECVD 工艺填充具有大深 宽比的间隙时会在其中部产生夹断和空洞.图 4 是 我们用单步 PECVD 填充 Si/SiO2-DBR 反射器 Si 槽中 SiO<sub>2</sub> 时发生夹断产生空腔的情况. 为了解决这 一难题,淀积-刻蚀-淀积循环工艺被用以填充 0.5~ 0.8μm 的间隙,具体工艺是在初始淀积完成部分填 孔尚未发生夹断时,紧跟着进行刻蚀工艺以重新打 开间隙入口,之后再次淀积以完成对整个间隙的填 充,如图 5(a) 所示. 显然,为了填充越小的间隙,越 来越多的工艺循环需要被执行,在不断降低产量的

图 4 单步 PECVD 工艺填充 DBR 反射器 Si 槽中 SiO<sub>2</sub> 时发 生夹断产生空腔

Fig. 4 Micro-cavity formed in the grating groove of DBR reflector when using single step PECVD process to deposit  $SiO_2$  into Si slot

图 5 (a) PECVD 淀积-刻蚀-淀积循环工艺填充窄槽示意图; (b) HDP-CVD 同步淀积-刻蚀工艺填充窄槽示意图 Fig. 5 (a) Schematic diagram for slot filling by PECVD-etching-PECVD circulatory process; (b) Schematic diagram for slot filling by HDP-CVD deposition-etching synchronous process

同时也显著增加了芯片成本,而且由于本身工艺的局限性,即便采用循环工艺,PECVD 对小于  $0.5\mu m$  的间隙还是无能为力.为了增强填孔能力,提高淀积质量,可采用高密度等离子体化学气相淀积(HDP-CVD)工艺,以解决线宽  $0.25\mu m$  以下窄槽和微孔的填充难题. HDP-CVD 工艺是在同一个反应腔中同步进行淀积和刻蚀的工艺(图 5(b)),具体来说,在常见的 HDP-CVD 制程中,淀积工艺通常是由 Ar和  $O_2$  的溅射来完成. HDP-CVD 高的等离子体密度加上硅片偏压产生的方向性,使 HDP-CVD 可以填充深宽比为 4:1 甚至更高的间隙.

#### 5 结束语

就我们在研制硅基光子晶体器件和 MOS 高速 电光调制器过程中遇到的一些工艺问题进行了分析 讨论,所涉及的具体工艺包括:电子束/光学光刻的电子束/光学邻近效应;纳米线光波导 ICP-RIE 刻蚀的侧壁粗糙问题;光栅及 MOS 绝缘栅氧化硅填充的致密性问题,并根据实验结果对上述问题提出了相应的解决办法.

#### 参考文献

- [1] Liu A, Jones R, Liao L, et al. A high-speed silicon optical modulator based on a metal-oxide-semiconductor capacitor. Nature, 2004, 427,615

- [2] Rong H,Jones R,Liu A, et al. A continuous-wave Raman silicon laser. Nature, 2005, 433, 725

- [3] Barrios C A, Almeida V R, Panepucci R, et al. Electrooptic modulation of silicon-on-insulator submicrometer-size waveguide devices. J Lightwave Technol, 2003, 21, 2332

- [4] Bogaerts W, Dumon P, Wiaux V, et al. Nanophotonic waveguides in silicon-on-insulator fabricated with CMOS technology. J Lightwave Technol, 2005, 23(1):401

# Challenges and Solution of Fabrication Techniques for Silicon-Based Nano-Photonics Devices\*

Chen Shaowu<sup>†</sup>, Tu Xiaoguang, Yu Hejun, Fan Zhongchao, Xu Xuejun, and Yu Jinzhong

(State Key Laboratory on Integrated Optoelectronics, Institute of Semiconductors, Chinese Academy of Sciences, Beijing 100083, China)

Abstract: This paper deals with several key fabrication techniques for silicon-based nano-photonics devices, including correction of optical proximity effect (OPE) of deep UV lithography and proximity effect of e-beam lithography (EBL), reduction of side wall roughness of silicon nanowire waveguide fabricated by ICP-RIE technique, compactness of silicon dioxide CVD filling for DBR grating grooves and MOS isolation gates. Based on the experimental results, some solutions were proposed and discussed.

Key words: silicon-based nano-photonics; optical proximity/e-beam lithography proximity effect; ICP-RIE; side wall roughness of silicon nanowire waveguide; CVD

EEACC: 2250; 2250E; 2250G

Article ID: 0253-4177(2007)S0-0568-04

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (No. 60577044)

<sup>†</sup> Corresponding author. Email: swchen@semi.ac.cn