# A New Structure for a CMOS Audio Power AMP with Extremely Low THD and Low Power Consumption \*

Cao Zhengxin<sup>†</sup> and Xiong Shaozhen

(Tianjin Key Laboratory for Photor Electronic Thin Film Devices and Technology, Institute of Photor Electronics, Nankai University, Tianjin 300071, China)

Abstract: A new system-corrected CMOS audio power AMP is presented. Consisting of four single-end OPAs, this structure is a pseudo-differential system. Compared to conventional CMOS power AMPs, it has the merits of low power consumption, extremely low THD, easy compensation, and good driving capability. With 1st silicon 0. 25µm 1P4M CMOS technology and a 3V power supply, the output range can be 4Vpp when driving an 8 300p F load, while its power dissipation is less than 3mW. The THD is better than 0. 003 % at 1kHz. A new over-current protection circuit, which can effectively protect the power output circuits on the chip, is also demonstrated.

Key words:system-corrected structure;CMOS power AMP;over-current protectionEEACC:1210;1220CLC number:TN722Document code:AArticle ID:0253-4177 (2006) 09-1552-05

# 1 Introduction

With the continuing development of high quality portable terminals, the requirement of high quality audio power amplifiers (AMPs) is becoming more popular. An audio power AMP requires the characteristics of low power consumption, low total harmonic distortion (THD), a large dynamic range, and a large driving capacity. Thus, it is a big challenge to design a CMOS audio power AMP.

According to the feedback theory equation,  $THD_{CLOSED} = THD_{OPEN} \frac{1}{1 + A(\ ) F}$ , increasing the loop gain, especially the open loop gain A(), is the most effective method. Generally, due to power supply limitations, a multi-stage OPA is chosen. However, with more stages, there are more poles, which induce stability issues.

Hwang and Lee<sup>[2]</sup> contrived an adaptive Qcurrent controlled class AB structure that can effectively decrease cross-over distortion. However, the structure is very complicated and consumes large current.

Brigati and Francesconi<sup>[3]</sup> adopted the pseudo source follower structure. They used a Pre AMP and an Error AMP to increase the open loop gain. The Error AMP plus the output stage MOS constituted the pseudo source follower structure. Since an offset exists, the gain of the Error AMP is no more than  $10^{[4.5]}$ , which contributes little to improve the THD.

Pernici *et al*.<sup>[6]</sup> proposed a four-stage cascaded structure to increase the open loop gain. In order to solve the stability problem, the Nested Miller Compensation was adopted. Though the open loop gain has been dramatically improved, a complicated compensation method and huge capacitor have also been introduced. Moreover, for the limited gain band width product (GBW), the THD has not been improved greatly.

Recently, Fujimoto *et al*.<sup>[7]</sup> used a sigma-delta technique to realize an audio power AMP, and Forejt *et al*.<sup>[8]</sup> designed a CLASS D audio AMP with 90nm technology. Excellent THDs have been achieved with their circuits. However, both of them require a high precision clock and costly external inductance.

A new system-corrected CMOS audio power AMP will be presented in this paper. It provides extremely high open loop gain with a simple structure and a negative zero to compensate the pole

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (No. 60437030)

<sup>†</sup>Corresponding author. Email:carnivorous21 @gmail.com

Received 16 January 2006, revised manuscript received 29 April 2006

effects and enhance the systematic phase character. When it is used to drive an 8 300pF load, the output voltage range can exceed 4Vpp with 3V supply voltage. The static dissipation is less than 3mW, and the THD is better than 0.003%. The structure of the system-corrected CMOS audio AMP will be described in detail, and a die photograph and the test results will also be presented.

# 2 Structure of the system-corrected power AMP

#### 2.1 Theory of the system corrected power AMP

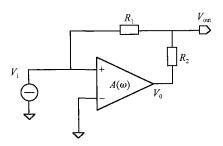

Consider the structure in Fig. 1. The signal source  $V_i$  is connected to the positive terminal of the AMP. Assuming that the signal source is ideal

Fig. 1 Pre AMP of the system-corrected structure

(inner resistor is zero), we get

**x** 7

$$V_{0} = A() V_{i}$$

(1)

we = (V\_{0} - V\_{i}) - \frac{R\_{1}}{R\_{1}} + V\_{i} (2)

$$\mathbf{v}_{out} = (\mathbf{v}_0 - \mathbf{v}_i) \mathbf{R}_1 + \mathbf{R}_2 + \mathbf{v}_i$$

(2)

Combining Eqs. (1) and (2) ,we get

H() =

$$\frac{V_{out}}{V_i} = \frac{R_1}{R_1 + R_2} (A() - 1) + 1 (3)$$

where A ( ) is the open loop gain of the AMP. When A ( )  $\gg 1$ ,

$$H() = \frac{V_{out}}{V_i} - \frac{R_1}{R_1 + R_2} A()$$

(4)

When  $A() \ll 1$ , Equation (3) becomes

H() =

$$\frac{V_{out}}{V_i}$$

=  $\frac{-R_1}{R_1 + R_2}$  + 1 =  $\frac{R_2}{R_1 + R_2}$  (5)

Assuming that the AMP has only one pole  $p_1$ , then

$$A( ) = \frac{A_0}{1 + \frac{s}{p_1}}$$

(6)

Substituting Eq. (6) into Eq. (3) ,we get

$$H( ) = \frac{V_{out}}{V_i} = \frac{R_1}{R_1 + R_2} \left( \frac{A_0}{1 + \frac{s}{p_1}} - 1 \right) + 1$$

$$= \frac{R_1 \left( A_0 - \left(1 + \frac{s}{p_1}\right) \right) + \left( R_1 + R_2 \right) \left(1 + \frac{s}{p_1}\right)}{\left( R_1 + R_2 \right) \left(1 + \frac{s}{p_1}\right)}$$

(7)

Setting the numerator of Eq. (7) to zero, we get

$$s = -A_0 p_1 \frac{R_1}{R_2} = -_0 \frac{R_1}{R_2}$$

(8)

where  $_0$  is the unity gain bandwidth. Equation (8) shows that a negative zero  $_z$  has been introduced in the path of  $R_1$  and  $R_2$ .

$$z = - 0 \frac{R_1}{R_2}$$

(9)

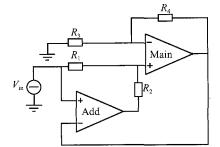

With this structure, a closed loop AMP has been connected to its output, and the system-corrected power AMP comes into being. For the sake of simplicity, the left AMP is named AddAmp, and the right AMP is named MainAmp. Figure 2 shows the unity feedback structure of the system-correc-

Fig. 2 Unity feedback structure of the system-corrected power AMP

ted power AMP. When the gain of MainAmp  $\gg 1$ , the open loop transfer function of the system corrected power AMP is

$$A_{s}() = H_{A}()(1 + \frac{R_{4}}{R_{3}})$$

(10)

Here  $H_A$  ( ) represents the transfer function of AddAmp. The nonlinear distortion of the systemcorrected power AMP mainly occurs in MainAmp. With the path of  $R_3$  and  $R_4$ , the THD of MainAmp is

$$THD_{M} = \frac{THD_{OPEN_{M}}}{1 + A_{M}}$$

(11)

where  $A_{\rm M}$  () is the open gain of the MainAmp,  $F_{\rm M}$  is the feedback coefficient of the MainAmp, and THD<sub>OPEN\_M</sub> is the open loop THD of the MainAmp. According to Eqs. (10) and (11), the closed unity feedback THD of the system corrected structure is

$$= \frac{THD_{\text{CLOSED_S}}}{(1 + A_{\text{M}}() \frac{R_3}{R_4 + R_3})(1 + H_{\text{A}}() (1 + \frac{R_4}{R_3}))}$$

(12)

When  $A_M() F_M \gg 1$ ,  $A_A() \gg 1$ , substituting Eq. (4) into Eq. (12) yields

THD<sub>closed\_s</sub>

$$\frac{\text{THD}_{\text{open}_M}}{A_M(\ )A_A(\ )(\frac{R_1}{R_2 + R_1})}$$

(13)

Equation (13) shows that the closed loop THD is dramatically decreased with the introduction of the AddAmp. The AddAmp also introduces a negative pole and a negative zero. Assuming that the open loop unity bandwidth of MainAmp is  $_{\rm OM}$ , the dominant pole of the MainAmp is

$$_{pM1} = _{0M} F = _{0M} \frac{R_3}{R_3 + R_4}$$

(14)

If the negative zero of the AddAmp cancels the dominant pole of the MainAmp, the system-corrected AMP will have just two poles. One is the dominant pole of the AddAmp,  $_{PA}$ , and the other is the second pole of the MainAmp,  $_{PM2}$ . That is,

$$_{zA} = _{pM1} = _{0M} \frac{R_3}{R_3 + R_4}$$

(15)

According to Eqs. (9) and (15), the unity gain bandwidth of the AddAmp is

$$_{0A} = _{0M} \frac{R_3}{R_3 + R_4} \times \frac{R_2}{R_1}$$

(16)

Combining Eqs. (13) and (16) ,when  $R_2 \gg R_1$  and  $R_3 \gg R_4$ , the THD of the closed loop reaches its minimum value. However, under the limitation of the output range of the AddAmp and the common mode input range of the MainAmp, we adopt  $R_3 = 2 R_4$ ,  $R_2 = R_1$  in practice.

In the above analysis, the inner resistor of the signal source has been set to zero. However, this is not true in fact. When the resistor value is bigger than  $\frac{R_1 + R_2}{A_A}$ , a positive feedback is produced in the AddAmp, which makes the system corrected power AMP less stable. Fortunately, a driving AMP with a low output resistor (a few ohms or tens of ohms) is often added before the power AMP. To keep the stability, the values of  $R_1$  and  $R_2$  must be several hundred kiloohms. In addition, increasing  $_{OM}$  can decrease the closed loop THD of the system. However, the load capacitor of the MainAmp is often several hundred pico-farads. In

this case, it is difficult to enlarge <sub>0M</sub>, and the consumed power will be very high.

In fact, Equation (15) is difficult to realize with the effects of temperature and the variety of the technology. To guarantee the stability of the system, we adopt the following condition:

$$_{pM1} < _{zA} < _{pM2}$$

(17)

A floating current source structure<sup>[9]</sup> has been chosen to realize the MainAmp, which can effectively control the static current and provide a large dynamic current. The unity bandwidth of the MainAmp is about 1MHz, with a differential 300p F capacitor load. The DC gain is 110dB, and the phase margin is about 60°. Since the load capacitor of the AddAmp is small, it is easy to design an AddAmp with low power dissipation. A simple cascode structure has been used in this design. The DC gain of the AddAmp is over 80dB, and the unity bandwidth is about 500kHz.

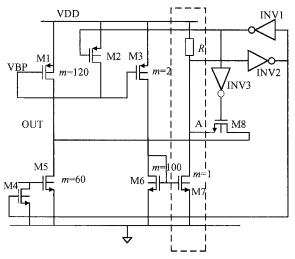

#### 2.2 Over-current protection circuit

Usually, an audio power AMP is used to drive a small resistor load, so it must have a good driving capacity. If the output of the power AMP is shorted to ground, the output MOS transistor will be damaged. Hence, an over-current protection circuit is necessary. Traditionally, a small resistor is placed in series with the output MOS transistor to limit the current ,but this dissipates much power in the normal mode. A new structure for an over-current protection circuit is shown in Fig. 3. The output current is attenuated by the mirror circuit M1/ M3 and M6/M7. When the current of the output transistors is large enough, the voltage of point A will drop to push the inverter change, and then transistors M2 and M4 will be closed while M1 and M5 will be cut off. Thus the output current is cut down. At the same time, the output of the INV3 is 'high', which sets the transistor M8 and shorts point A to the output. If the short ground path is not moved away, the over-current protection circuit will still work in the cut down mode. Once the short ground path is removed, the voltage of point A will rise immediately to push the inverter change ,and the transistors M2 and M4 will be cut off. Then the output of INV3 will be 'low', and the system will return to the normal mode. The threshold of the protection current can be set by adjusting the value of resistor R and the width and

Fig. 3 Over-current protection circuit

length of the transistors in INV2. The over-current protection circuit of M5 is very similar to that of M1, which is not mentioned here.

## **3** Photograph of the die

Figure 4 shows a die photograph of the system-corrected CMOS audio power AMP. It occupies 0.  $48 \text{mm}^2$  and has been fabricated with 0.  $25 \mu \text{m}$  1P4M technology in 1st silicon.

Fig. 4 Die photograph

## 4 Test results

Ten samples have been tested with the THD analyzer DF4120. The THD parameter is better than 0.003 % with an 8 300pF differential load and a 1kHz,4Vpp sine wave stimulus. The average static current of the samples is 890µA. When the output terminal is shorted to ground, the current of the system-corrected CMOS audio power AMP decreases to 560µA. Once the short-to-ground line is removed, the AMP returns to the normal state. This provides strong evidence for the function of the new over-current protection circuit. The parameters are listed in Table 1. For comparison, the parameters of other power AMPs are listed in Table 2.

| Table 1  | Parameters of | the | system-corrected | CMOS |

|----------|---------------|-----|------------------|------|

| power AN | 1P            |     |                  |      |

|                                                            | Average of the ten samples |  |

|------------------------------------------------------------|----------------------------|--|

| Static current                                             | 890µA                      |  |

| Input offset voltage                                       | 1.6mV                      |  |

| Current of short-to-ground connection                      | 560µA                      |  |

| SNR                                                        | $> 100 dB^{1)}$            |  |

| THD @1kHz 4Vpp 8 300pF load                                | < 0. 003 % <sup>2)</sup>   |  |

| Maximum efficiency @2.5V power supply, $THD < 0.\ 003\ \%$ | 70 %                       |  |

| PSRR @DC                                                   | 120dB                      |  |

| Minimum supply voltage                                     | 1.5V                       |  |

1) 100dB is the maximum value that can be detected by DF4120.

2) 0.003 % is the minimum value that can be detected by DF4120.

Table 2Parameters of the system-corrected powerAMP and the other power AMPs

|                        | System-corrected<br>power AMP | Adaptive<br>Q-current<br>controlled<br>class AB <sup>[2]</sup> | Class D <sup>[8]</sup> | Sigma-Delta<br>switching<br>power<br>AMP <sup>[7]</sup> |

|------------------------|-------------------------------|----------------------------------------------------------------|------------------------|---------------------------------------------------------|

| Supply voltage/ V      | 3                             | 5                                                              | 4.2                    | 5                                                       |

| Static power/ mW       | 2.7                           | 13                                                             | 7                      | 300                                                     |

| THD @1kHz              | < - 90 dB<br>$R_L = 8$        | -54dB<br>R <sub>L</sub> = 8                                    | < - 90 dB<br>$R_L = 8$ | - 96dB                                                  |

| A rea/ mm <sup>2</sup> | 0.48                          | 2.88                                                           | 0.44                   | 12.6 <sup>2</sup>                                       |

# 5 Conclusion

A new system-corrected power AMP has been presented on the basis of analyzing the traditional power AMP. It has the merits of low power consumption, extremely low THD, easy compensation, and good driving capability. With a 1kHz 4Vpp sine wave stimulus, the THD is better than 0.003 % when driving an 8 300pF load. It consumes only 2.7mW of static power. A new overcurrent protection circuit has also been mentioned, which is very suited for the CMOS power AMP. Furthermore, it can detect an external short-to-ground circuit and manage with the right function automatically.

#### References

- [1] Razavi B. Design of analog CMOS integrated circuit. McGraw-Hill Companies, 2001:455

- [2] Hwang J T, Lee H S. 1W 0. 8µm BiCMOS adaptive Q-current

controlled class-AB power amplifier for sound equipments. ISSCC, 2002

- [3] Brigati S, Francesconi F, Grassi G, et al. An 0. 8µm CMOS mixed analog-digital integrated audiometric system. ISSCC Dig Tech Papers ,San Francisco, USA ,1998:116

- [4] Ahuja B K, Gray P R, Baxter W M, et al. A programmable CMOS dual channel interface processor for telecommunications. IEEE J Solid-State Circuits, 1984, SC-19:892

- [5] Kih J, Chang B, Jeong D K, et al. Class-AB large-swing CMOS buffer amplifier with controlled bias current. IEEE J Solid-State Circuits, 1993, SC-29:1350

- [6] Pernici S, Nicollini G, Castello R. A CMOS low-distortion

fully differential power amplifier with double nested miller compensation. IEEE J Solid-State Circuits ,1993 ,28(7) :758

- [7] Fujimoto Y, R éP L, Miyamoto M. A Delta-Sigma modulator for a 1-bit digital switching amplifier. IEEE J Solid-State Circuits, 2005, 40(9):1865

- [8] Forejt B, Rentala V, Arteaga J D, et al. A 700 +-mW class D design with direct battery hook up in a 90-nm process. IEEE J Solid-State Circuits, 2005, 40(9):1880

- [9] Hogervorst R, Tero J P, Eschauzier R G H, et al. A compact power-efficient 3V CMOS rail-to-rail input/output operational amplifier for VLSI cell libraries. IEEE J Solid-State Circuits, 1994, 29 (12):1505

# 一种新型的超低 THD,低功耗 CMOS 音频功率放大器\*

#### 曹政新<sup>†</sup> 熊绍珍

### (南开大学光电子研究所,天津光电子薄膜器件及工艺重点实验室,天津 300071)

摘要:提出了一种新型的系统矫正结构 CMOS 音频功率放大器.该放大器是由 4 个单端运放组成的伪差分结构. 相对于传统的 CMOS 功率放大器,它具有低功耗、超低 THD、易于补偿、驱动能力强等优点.采用 1st silicon 0.25µm 1P4M 工艺制备,在 3V 电源电压下,驱动 8 300pF 的负载,其输出摆幅可以达到 4Vpp,静态功耗小于 3mW.在 1kHz 的正弦波激励下,其 THD 小于 0.003%.还提出了一种新型的过流保护电路,可以对片内大功率输 出级电路进行有效的保护.

关键词:系统矫正结构;CMOS 功率放大器;过流保护电路 EEACC:1210;1220 中图分类号:TN722 文献标识码:A 文章编号:0253-4177(2006)09-1552-05

<sup>\*</sup>国家自然科学基金资助项目(批准号:60437030)

<sup>†</sup>通信作者. Email :carnivorous21 @gmail.com