## Modeling of Gate Tunneling Current for Nanoscale MOSFETs with High- k Gate Stacks<sup>\*</sup>

Wang Wei<sup>1,†</sup>, Sun Jianping<sup>2</sup>, and Gu Ning<sup>1</sup>

(1 State Laboratory of Bioelectronics, Jiangsu Laboratory for Biomaterials and Devices, Southeast University, Nanjing 210096, China)

(2 Department of Electrical Engineering and Computer Science, University of Michigan, USA)

**Abstract :** A quantum model based on solutions to the Schrödinger-Poisson equations is developed to investigate the device behavior related to gate tunneling current for nanoscale MOSFETs with high- k gate stacks. This model can model various MOS device structures with combinations of high- k dielectric materials and multilayer gate stacks, revealing quantum effects on the device performance. Comparisons are made for gate current behavior between nMOSFET and pMOSFET high- k gate stack structures. The results presented are consistent with experimental data , whereas a new finding for an optimum nitrogen content in HfSiON gate dielectric requires further experimental verifications.

Key words: high- k; gate current; quantum modelEEACC: 2570ACLC number : TN386Document code : A

## 1 Introduction

The on-going research on materials, device structures and assembly methods for microelectronic devices with feature sizes smaller than 100nm carries the goal to keep Moore 's law in force beyond limits of current microchip technology. To understand the device behavior and provide design aids for sub-0. 1µm devices ,numerous studies have been conducted on the modeling of the gate current and gate capacitance of nanoscale MOSFETs. Control and reduction of gate leakage current bear practical significance for low power CMOS circuits and to alleviate the scaling limits. High-k gate stack structures as candidates to replace silicon dioxide layer for nanoscale MOSFETs have received great attention due to their promise in reduction of gate current and standby power consumption<sup>[1~5]</sup>. A number of high-k gate stack structures have been studied experimentally and theoretically, with most of the modeling approaches based on the WKB approximation. The WKB approaches have gained popularity recently due to

Article ID: 0253-4177 (2006) 07-1170-07

their simplicity and less numerical work. However, they have inherent shortcomings in that some physics aspects are parameterized, that it is unable to evaluate gate current and capacitance simultaneously. In addition, in principle, it cannot model combinations of various high-k stack dielectrics with interfacial layers properly. Therefore, most approaches existed are insufficient to carry out the tasks for significant engineering of high-k stack structures and silicon dielectric interface ,which are required due to complications associated with applicability and compatibility of the materials and processing of the high-k stacks with silicon technologies. Furthermore, most modeling work performed and published so far is mainly focused on nMOS-FETs with high-k gate stacks. For pMOSFETs, to our knowledge ,only modeling work published was presented in Ref. [6], in which the WKB approach was also employed.

In this work, a unified formulation is employed to model nanoscale n and pMOSFETs with high-kstacks as their gate dielectrics, aimed at the gate current reduction and evaluation of other relevant device properties. When the device feature sizes

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (Nos. 60371037, 20573019)

<sup>†</sup>Corresponding author. Email :wangwei @njupt.edu.cn

Received 24 January 2006, revised manuscript received 29 March 2006

reach nanoscale dimensions, a gate dielectric thickness of less than 2. Onm would be required for nanoscale MOS devices with power supply voltages of 1. 0 to 1. 5V. The simultaneous requirement to keep the same or greater gate capacitance and lower gate current entails the same or greater equivalent oxide thickness (EOT) as well as a thicker physical insulating layer for reduction of gate tunneling current. The same or larger gate capacitance is necessary for good gate control over the channel current and reduction of the short channel effects.

## 2 Method of calculation

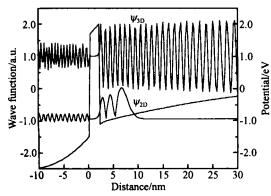

The present model is based on self-consistent solutions of the Schrödinger-Poisson equations previously developed for modeling quantum-tunneling devices<sup>[7,8]</sup>, with modifications made for nanoscale MOSFETs in the y direction perpendicular to the dielectric layers. The gate current components of the thermionic emission, FN tunneling, and direct tunneling through the oxide barrier are evaluated as a whole using a traveling wave calculation, hereafter referred to as  $J_{3D}$ , while the tunneling component from the inversion layer quantum well is evaluated by a transmission calculation, hereafter referred to as  $J_{2D}$ , both obtained from the solutions of the Schrödinger equation, self-consistently with its potential term determined by the Poisson equation. The calculated electron wave functions relevant to the current transport are shown in Fig. 1 to illustrate the current transport components originated from the 3D electrodes and 2D quantum well in the inversion layer. As an example of the 2D wave functions,

Fig. 1 Electron wave functions from the 3D and 2D electron states Only the third quasi-bound state in the inversion layer is shown.

<sub>2D</sub>, only the wavefunction at the third level of the quasi-bound states is shown.

We first calculate the self-consistent potential and charge distributions in the polysilicon and substrate regions from the coupled Poisson equation and Fermi distribution function. The electrostatic potential across the device in the y direction is determined by the doping profile and mobile charges, as governed by the Poisson equation.

$$\frac{\partial^{2} V(y)}{\partial y^{2}} = -\frac{q}{(y)} [N_{D}(y) - N_{A}(y) - n(y) + p(y)]$$

(1)

where (y) is the dielectric constant of individual high- k stack layers, n(y) is the electron density, and p(y) is the hole density in the quasi-equilibrium contact regions in terms of local Fermi levels,

$$n(y) = N_{C} \frac{2}{\sqrt{F_{1/2}}} F_{1/2} \frac{E_{F}(y) - E_{C}(y)}{k_{B} T}$$

(2)

$$p(y) = N_{v} \frac{2}{\sqrt{F_{1/2}}} \frac{E_{v}(y) - E_{F}(y)}{k_{B} T}$$

(3)

where  $N_{\rm C}$  and  $N_{\rm V}$  are the effective densities of states in the conduction band and valence band, respectively, and

$$F_{1/2}() = \frac{x^{1/2}}{1 + \exp(x - y)} dx \qquad (4)$$

is the Fermi-Dirac integral function. Note that Fermi levels  $E_F(y)$  are assumed to be constants, respectively, in the poly-silicon and silicon substrate regions and that conduction band and valence band edge are related to the potential by<sup>[7,8]</sup>

$$E_{C}(y) = E_{C}(\pm) - q[V(x) - V(\pm)]$$

(5)

$$E_{V}(y) = E_{C}(\pm) - q[V(x) - V(\pm)] - E_{g}$$

where  $E_g$  is the energy bandgap of silicon. The

Fermi integrals in Eqs. (2) and (3) can be expanded by rapidly converging power series in terms of the ratios  $r_1 = n(y) / N_c$  and  $r_2 = p(y) / N_v$ , respectively, based on the Joyce-Dixon approximation<sup>[7,8]</sup>:

$$\frac{E_{F}(y) - E_{C}(y)}{k_{B} T} - \lg r_{1} = \prod_{\substack{k=1 \\ N}}^{N} A(k) r_{1}^{k}$$

(7)

$$\frac{E_{V}(y) - E_{F}(y)}{k_{B} T} - \lg r_{2} = \prod_{k=1}^{k} A(k) r_{2}^{k}$$

(8)

with the coefficient A (k) determined using a least-squares fit technique. In each y point, Eqs. (1), (7), and (8) lead to three coupled nonlinear equations with three unknows, i.e., the electron density, hole density and potential, which are then

solved using the Newton iterative method with a sparse matrix technique. For the charges inside the quantum well of the inversion layer formed under positive gate bias voltages and for the gate current components through and/ or above the ultrathin oxide barrier, quantum calculations are performed by directly solving the Schrödinger equation:

$$-\frac{\hbar^{2}}{2} \times \frac{\partial}{\partial y} \left( \frac{1}{m^{*}(y)} \times \frac{\partial(y)}{\partial y} \right) + E_{C}(y) \quad (y) = E(y)$$

(9)

The self-consistent electron charge at the j-th energy subband in the i-th valley in the inversion layer is given by

$$n_{ij}(y) = \frac{\underline{m}_{i} \mathbf{k}_{B} \mathbf{T}}{\hbar^{2}} ln \left[ 1 + exp \left( - \frac{\underline{E}_{ij} - \underline{E}_{F}}{\underline{k}_{B} \mathbf{T}} \right) \right] \mathbf{x}$$

$$|_{ij}(\underline{E}_{ij}, y)|^{2}$$

(10)

where  $_{ij}$  (E<sub>ij</sub>, y) is the electron wavefunction at the *j*-th subband in the *i*-th valley from the solution of the Schrödinger equation in the inversion layer. The gate current evaluation is performed by the traveling wave calculations for the thermionic emission, Fowler-Nordheim (FN) tunneling, and direct tunneling through the oxide barrier, giving  $J_{3D} = -q\hbar = W(k) Im \begin{bmatrix} i \\ k \end{pmatrix} (y) = \frac{1}{2} \left( \frac{\partial_{ik}(y)}{\partial_{ik}(y)} \right)$

$$J_{3D} = -q\hbar \left[ W(k) Im \left[ \frac{k}{k}(y) \frac{1}{m^{*}(y)} \times \frac{\partial F(y)}{\partial y} \right] \right]$$

(11)

where weighting function W(k) is given by

$$W(k) = \frac{m^{*} k_{B} T}{2^{*} \hbar^{2}} ln \left(1 + \frac{E_{F} - E_{I}}{k_{B} T}\right)$$

(12)

and  $E_1 = \hbar^2 k_1^2 / 2 \text{ m}^*$  is the longitudinal energy of the electron with wave-vector  $k_1$ .

For the electron tunneling current from the inversion layer into the oxide and gate electrode, a transmission calculation is performed. Based on the wave functions calculated in the inversion layer, the transmission is given by

$$T_{ij} = \frac{|C_{tr,ij}|^2}{|A_{in,ij}|^2} \times \frac{k_{tr,ij}}{k_{in,ij}} \times \frac{m_{in,i}}{m_{tr,i}}$$

(13)

where  $C_{\text{tr},ij}$  is the transmitted wave amplitude in the  $\dot{r}$ th valley and the  $\dot{r}$ th subband ,and  $A_{\text{in},ij}$  the incident wave amplitude in the corresponding subband and valley. The 2D gate current component originated from the subbands in the inversion layers is then

$$J_{2D} = J_{i,j} = q n_{ij} T_{ij} f_{ij}$$

(14)

where  $T_{ij}$  is the electron transmission probability,  $f_{ij} = \frac{E_{ij}}{j \hbar}$  the electron impact frequency on the interface,  $n_{ij}$  the sheet electron density, and  $E_{ij}$  the quasi-bound state energies in the *i*-th valley and the *j*-th subband. The total gate current density is the sum of the 2D and 3D components.

In the present approach, we treat the thermionic emission, FN tunneling, and direct tunneling current components in a unified formulation. Most of other treatment to these current components involve complicated formulas and ,in many cases ,fitting parameters. We consider that the separation of the current transport components is a reflection of the historical development of the MOS scaling efforts toward nanoscale dimensions, and that, in principle, tunneling depends on the overall potential profile in the electron tunneling path, rather than a particular part of the potential profile. Therefore, the separation and delimitation of various gate current components may involve inconsistencies in the interfacing and integration of those components. In addition, the gradual potential barrier approximation inherent in the WKB approach may become improper for the sharp potential interfaces between the polysilicon and substrate for nanoscale MOSFETs. In our opinion, as the feature sizes approach nanoscale dimensions, the device structure in the direction of interest may well be treated as an integrated ,open quantum system ,and a fully self-consistent solution to the Schrödinger-Poisson equations is necessary and sufficient to model all the gate current transport components and obtain all the device terminal properties of interest.

An important feature of the present model lies in that the electrostatic potential V(y) and the material parameters can be accurately specified at each y point in the multilayered stack structures, allowing evaluation of various schemes of combination having different stack materials and different layers. Moreover, the possible fixed charge and interface charge distributions in the stacked layers can also be accommodated in Poisson 's equation, as long as these charge distributions are available. Therefore, the present approach enables us to study multilayer high-k stack structures of nanoscale MOSFETs, consisting of various dielectric materials for various configurations.

As the channel length is further reduced, the two-dimensional effects like the edge direct tunneling (EDT), drain-induced barrier lowering (DIBL) ,and  $V_{\rm T}$  roll-off become non-negligible. In the high drain bias, these problems cannot be described directly in 1D model. In this work, to solve the 2D problems such as EDT, we begin by using 2D Poisson equation and electron and hole current continuity equations to solve the charge and potential distribution throughout the device. Then, in ydirection (perpendicular to the dielectric layers), we solve the 1D Schrödinger-Poisson equations for each x position (assuming x-direction along the channel) using the calculated charge and potential distribution as input data. Using the gate current model given above, we can compute the tunneling current density for each x position, which we can integrate to obtain the total gate current.

## **3** Results and discussion

#### 3.1 Comparison with experiment

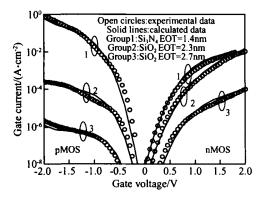

Figure 2 shows a comparison between the calculated and measured gate tunneling current characteristics of nMOS and pMOS structures (EOT of

Fig. 2 Comparison of gate current for pMOS and nMOS with calculated data and experimental data The experimental data are taken from Refs. [9,10]. The electron and hole barrier height, effective mass, are known for SiO<sub>2</sub> (3. 10eV/4. 5eV, 0.  $40m_0/0$ .  $32m_0$ ) and Si<sub>3</sub>N<sub>4</sub> (2. 10eV/1. 90eV, 0.  $50m_0/0$ .  $40m_0$ )<sup>[10]</sup>, and dielectric constant for SiO<sub>2</sub> (3. 9) and Si<sub>3</sub>N<sub>4</sub> (7. 8)<sup>[6]</sup>.

2. 3 or 2. 7nm for  $SiO_2$ , 1. 4nm for  $Si_3N_4$ ), with excellent agreement between the theory and experiment. The curves of Group 1 are for the  $Si_3N_4$  cases, and the curves of Group 2, 3 are for the cases of  $SiO_2$ . It is apparent that the gate current decreases with increasing dielectric thickness for  $SiO_2$ .

Furthermore ,for the same SiO<sub>2</sub> film thickness ,the gate current density for the n-MOS case is larger than that for the p-MOS case due to the lower conduction band offsets in the nMOS structures and higher valence band offsets in the pMOS structures<sup>[10]</sup>. However ,for the cases of Si<sub>3</sub>N<sub>4</sub> ,the gate current in pMOS is larger than that in nMOS due to the higher conduction band offset in nMOSFET for binary dielectric materials and the higher electron effective mass in the dielectric layer for nMOSFET ,as explained in Ref. [10].

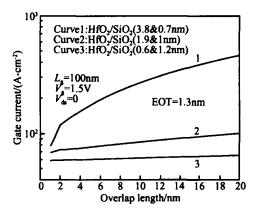

#### 3.2 Effects of high-k dielectric thickness

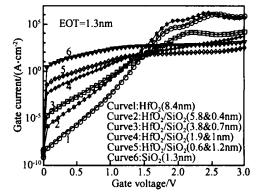

For high-k stack structures consisting of a single high-k layer and a SiO<sub>2</sub> layer, HfO<sub>2</sub> stacks are taken as an example of gate current dependence on the thickness of the high-k layer with the same EOT of 1. 3nm, as shown in Fig. 3. All the high-k stacks make a reduction of gate current as compared with SiO<sub>2</sub> gate dielectric layer, especially at lower gate voltages applicable for nanoscale

Fig. 3 Calculated gate current versus gate voltage with different physical thickness of the high-*k* dielectric with the same EOT (1. 3nm) for HfO<sub>2</sub>/SiO<sub>2</sub> gate stack structures The electron barrier height, effective mass, and dielectric constant for HfO<sub>2</sub> are 1.  $50eV^{[4]}$ , 0.  $20m_0^{[11]}$ , and  $25^{[4]}$ , respectively.

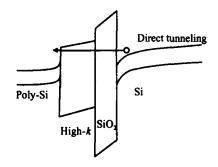

nMOSFETs, due to the additional physical width in the tunneling path for the lower energy electrons that contribute most of the gate current, as shown in Fig. 4. As expected, the physical thickness of the high-k layer plays a dominating role at the lower gate voltages. The difference can be as large as  $4 \sim$ 5 orders of magnitude between the high and low HfO<sub>2</sub>/SiO<sub>2</sub> thickness ratios for the same EOT, as observed in the Fig. 3. At higher gate bias voltages near and above the barrier height of the high-k dielectric layer, however, the gate current is dominated by FN tunneling and thermal emission. Therefore the magnitude of gate current of the high-k stack structure and the SiO<sub>2</sub> structure becomes comparable, and that the former can be orders of magnitude larger than that of the SiO<sub>2</sub> structure at even higher gate voltage. In other words, at lower gate bias, the gate current is mainly affected by the dielectric constant of the high-k dielectric material utilized, while at higher bias, it is mainly determined by its barrier height.

Fig. 4 Electron direct tunneling band diagram of highk gate stack nanoscale MOS structure

Other types of high-k stack structures using SiO<sub>2</sub>/Ta<sub>2</sub>O<sub>5</sub>/SiO<sub>2</sub> gate dielectrics<sup>[12]</sup> and adding Al<sub>2</sub>O<sub>3</sub> capping layer<sup>[13]</sup> have been proposed to alleviate the interfacial structure problems<sup>[12]</sup>. The present modeling approach is applied to study of this type of multiple layered structures, with the material and structural parameters specified accurately in the individual stacked layers.

Recent studies<sup>[14,15]</sup> have shown that the direct tunneling between the source/drain extension and gate overlap region, i. e. the edge direct tunneling (EDT), dominates the off-state current, especially in very short channel devices. This results from the fact that the ratio of the gate overlap to the total channel length is larger for the short channel device than that of the long channel device.

Figure 5 shows the simulated gate current versus the length of overlap region for high-k stack structures. In the figure, we can see that the gate currents are higher with larger overlap length. This effect is due to the fact that the flat-band voltage for channel region is negative, whereas the flatband voltage for the overlap region is almost zero, thus resulting in higher vertical electric field, and more leakage current density for the overlap region. It is also noted that the gate current is re-

Fig. 5 Calculated gate current versus the length of overlap region with different physical thicknesses of the high-k dielectric with the same EOT (1. 3nm) for HfO<sub>2</sub>/SiO<sub>2</sub> gate stack structures

duced with increasing dielectric thickness of  $SiO_2$ layer in the  $HfO_2/SiO_2$  stacks. This is attributed to the interplay among various factors of the structure and material parameters, such as the oxide barrier height, electron effective masses, and dielectric constant. However, EDT current is mainly affected by its barrier height. As expected, with increasing the length of overlap region, the EDT effect results in higher vertical field. Thus, the thickness of  $SiO_2$ plays a dominating role, due to  $SiO_2$  layer with higher barrier in the tunneling path for the higher energy electrons of EDT.

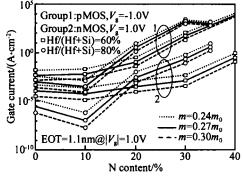

#### 3.3 Effects of nitrogen incorporation

It is reported that incorporation of nitrogen into hafnium silicate (HfSiO), hafnium aluminate (HfAlO) and HfO<sub>2</sub> greatly enhances the dielectric constant of silicates, suppresses dopant diffusion from gate poly-Si into the channel during high temperature annealing process, and increases crystallization temperature of the high- k stacks<sup>[16]</sup>. These properties are ascribed to the homogeneity of the bond structure in the film containing nitrogen through high temperature annealing. These improvements make these Hf-based materials more suitable for the CMOS process. The increase of nitrogen content leads to an increase of the dielectric constant but a decrease of the conduction band offset as well as the valence band offset. It is interesting to observe that, as the only exception among most high-k dielectrics, the conduction band offset with nitrogen incorporation may be larger than the valence band offset, such as in the case of HfSiON.

It is an advantage for the reduction of gate current in n-MOSFETs. For the pMOSFETs, however, such property would not be useful since the hole tunneling is dominant for the gate current.

In Fig. 6, the effects of nitrogen content on the gate current are shown for tunneling current through HfSiON dielectric film. Three different electron effective masses in between that of  $SiO_2$ , HfO<sub>2</sub>, and  $Si_3N_4$  were used in the calculations as the value of the electron and hole effective mass is not available, and such modeling calculations have

Fig. 6 Simulated tunneling current through HfSiON dielectric films of different nitrogen contents for nMOS-FET and pMOSFET

not been found in the open literature. However, the values of dielectric constant and barrier height were taken from experimental work<sup>[17]</sup> with the N content up to 40 % for the curves of Hf/(Hf + Si)being 60 %, and up to 35 % for the rest of the curves<sup>[16]</sup>. The results here show that for both cases, there is an optimum value of the N content (approximately 10%) where minimum gate current may be achieved. This is attributed to the interplay between the dielectric constant and barrier height; the incorporation of N leads to an increase of the dielectric constant while maintaining essentially the same barrier height until the N content reaches 10 % where the barrier height start decreasing significantly. This optimum value of N content is a new finding from this work, to be verified experimentally. It is also noted that the gate current in the pMOSFETs is larger than that of the nMOS-FETs with the same EOT and N content; this is because that ,with the virtually same dielectric constant ,the valence band offset in the pMOSFETs is smaller than the conduction band offset in the nMOSFETs.

## 4 Conclusion

Based on quantum modeling of electron tunneling, we have modeled the influence of quantum effects on the gate current of nanoscale p- and n-MOSFETs with high-k stack dielectric structures. The main feature of the present approach is that most of the effects of interest can be studied simultaneously and in a unified fashion, without having to use fitting parameters as done in approaches based on the WKB approximation. Moreover, since the material and structural parameters can be specified accurately at each structural point, various configurations of high-k stack materials and their combinations can be investigated properly. Therefore, the present approach can be used to provide guidelines for experimental studies of high-k stack structures for nanoscale MOSFETs. Our modeling results have demonstrated effects of dielectric film thickness, nitrogen incorporation, and various stack configuration ,on the gate current , showing consistency with experimental results. A new finding has also been generated as a result of this work ,indicating the optimum nitrogen content for nitrogen incorporation scheme. However, further experimental work is required to verify this result.

#### References

- Fan Y Y, Nieh R E, Lee J C, et al. Voltage and temperature dependent gate capacitance and current model : application to ZrO<sub>2</sub> MOSCAPs. IEEE Trans Electron Devices, 2002, 49 (11) :1969

- [2] Fan Y Y,Xiang Q,An J, et al. Impact of interfacial layer and transition region on gate current performance for high-k gate dielectric stack :its tradeoff with gate capacitance. IEEE Trans Electron Devices ,2003 ,50 (2) :433

- [3] Kizilyalli I C, Huang R Y S, Roy P K. MOS transistors with stacked SiO<sub>2</sub>-Ta<sub>2</sub>O<sub>5</sub>-SiO<sub>2</sub> gate dielectrics for giga-scale integration of CMOS technologies. IEEE Trans Electron Device Lett, 1998, 19(11):423

- [4] Zhao Y, White M H. Modeling of direct tunneling current through interfacial oxide and high-k gate stacks. Solid-State Electron, 2004, 48:1801

- [5] Zhang J, Yuan J S, Ma Y, et al. Design optimization of stacked layer dielectrics for minimum gate leakage currents. Solid-State Electron ,2000,44:2165

- [6] Yu H Y, Hou Y T, Li M F, et al. Investigation of hole tunneling current through ultrathin oxynitride/ oxide stack gate dielectrics for p-MOSFETs. IEEE Trans Electron Devices ,2002, 49(7):1158

- [7] Sun J P, Mains R K, Chen W L, et al. *CV* and *FV* characteristics of quantum well varactors. J Appl Phys, 1992, 72 (9):

2340

- [8] Sun J P, Haddad G I, Mazumder P, et al. Resonant tunneling diodes : models and properties. Proceedings of the IEEE, 1998, 86(4):641

- [9] Hou Y T,Li M F Jin Y,et al. Direct tunneling hole currents through ultrathin gate oxides in metal-oxide-semiconductor devices. J Appl Phys ,2002 ,91 (1) :258

- [10] Yeo Y C ,Lu Q ,Lee W C ,et al. Direct tunneling gate leakage current in transistors with ultrathin silicon nitride gate dielectric. IEEE Electron Device Lett ,2000 ,21 (11) :540

- Hou Y T,Li M F, Yu H Y,et al. Modeling of tunneling current through HfO<sub>2</sub> and (HfO<sub>2</sub>)<sub>x</sub> (Al<sub>2</sub>O<sub>3</sub>)<sub>1-x</sub> gate stacks. IEEE Electron Device Lett ,2003 ,24(2) :96

- [12] Cassan E, Galdin S, Dollfus P, et al. Analysis of electron energy distribution function in ultra-thin gate oxide mMOSFETs using Monte Carlo simulation for direct tunneling gate current calculation. Physica B, 1999, 272:550

- [13] Yang C W, Fang Y K, Chen C H, et al. Dramatic reduction of

gate leakage current in 1. 61nm HfO<sub>2</sub> high- k dielectric polysilicon gate with Al<sub>2</sub>O<sub>3</sub> capping layer. Electron Lett ,2002 ,38 : 1223

- Yang K N, Huang H T, Chen M J, et al. Characterization and modeling of edge direct tunneling (EDT) leakage in ultrathin gate oxide MOSFETs. IEEE Trans Electron Devices ,2001,48 (6) :1159

- [15] Choi C H ,Nam K Y ,Yu Z P ,et al. Impact of gate direct tunneling current on circuit performance: a simulation study. IEEE Trans Electron Devices ,2001 ,48 (12) :2823

- [16] Koyama M, Kaneko A, Ino T, et al. Effects of nitrogen in Hf-SiON gate dielectric on the electrical and thermal characteristics. IEDM Tech Dig ,2002:849

- [17] Koike M, Ino T, Kamimuta Y M, et al. effect of Hf-N bond on properties of thermally stable amorphous HfSiON and applicability of this material to sub-50nm technology node LSIs. IEDM Tech Dig ,2003:107

# 高 k 栅介质纳米 MOSFET 栅电流模型<sup>\*</sup>

### 王 **伟** $^{1,\dagger}$ 孙建平<sup>2</sup> 顾 宁<sup>1</sup>

(1 东南大学生物电子学国家重点实验室,江苏省生物材料与器件重点实验室,南京 210096)(2 美国密西根大学电气工程和计算机科学系,美国)

摘要:介绍了一种纳米 MOSFET(场效应管)栅电流的统一模型,该模型基于 Schrödinger Poisson 方程自洽全量子数值解,特别适用于高 k 栅介质和多层高 k 栅介质纳米 MOSFET.运用该方法计算了各种结构和材料高 k 介质的 MOSFET 栅极电流,并对 p MOSFET和 n MOSFET 高 k 栅结构进行了分析比较.模拟得出栅极电流与实验结果符合,而得出的优化氮含量有待实验证实.

关键词:高 k; 栅电流;量子模型

PACC: 7340G; 7340Q

中图分类号: TN386

文献标识码: A

文章编号: (

文章编号: 0253-4177(2006)07-1170-07

<sup>\*</sup>国家自然科学基金资助项目(批准号:60371037,20573019)

<sup>†</sup>通信作者. Email :wangwei @njupt.edu.cn 2006-01-24 收到,2006-03-29 定稿