# Automatic IQ Phase Calibration Design in a 2. 4 GHz Direct Conversion Receiver \*

Liu Ruifeng<sup>†</sup>, Li Yongming, Chen Hongyi, and Wang Zhihua

(Institute of Microelectronics, Tsinghua University, Beijing 100084, China)

**Abstract :** An automatic IQ phase calibration method implemented in a 2 4GHz direct conversion receiver is proposed. It uses a delay locked loop (DLL) with a proposed quadrature phase detector to greatly reduce the phase error. The receiver is fabricated in a 0. 18µm CMOS process. Measurements show that the IQ phase error can be calibrated within 1°, which satisfies the system requirement.

Key words:direct conversion receiver;IQ phase calibration;CMOS process;quadrature phase detectorEEACC:1205;2570DCLC number:TN402Document code:AArticle ID:0253-4177 (2006) 09-1531-06

### 1 Introduction

Direct conversion transceivers have become increasingly popular in recent years for their high integration ability. Direct conversion is the natural approach to translate a signal band from RF to baseband or from baseband to RF. The image problems in superheterodyne and low intermediate frequency (IF) conversion architectures are circumvented because the IF is zero. The LNA does not need to drive a 50 load because no image rejection filter is required<sup>[11]</sup>. All of these advantages make direct conversion transceivers easy to integrate on a chip with less power and area consumption.

However, there are still some drawbacks to the direct conversion architecture, such as IQ mismatch. IQ mismatch is mostly caused by imbalance between I and Q local oscillator (LO) signals. In heterodyne transceivers, the LO signals for IQ generation or summation are IF signals. The IQ imbalance can be made negligible. However, the LO signals in direct conversion transceivers are RF signals. Owing to the limitations of LO generation circuits and parasitics, the IQ performance cannot be very good, resulting in a reduced signal-to-noise ratio (SNR) and hence performance degradation<sup>[2]</sup>. In complex modulation schemes, such as 64-QAM, an IQ phase accuracy better than 1 ° and an amplitude accuracy better than 1 % are required to guarantee that the inaccuracy does not limit the overall performance<sup>[2]</sup>. To reach such a goal ,a good circuit and layout are usually insufficient. Calibration should be performed to guarantee good IQ performance.

In this paper, an automatic IQ phase calibration method implemented in a direct conversion receiver is presented. The receiver has been fabricated in a 0. 18µm CMOS process. Measurements are also presented to verify the calibration effect.

### 2 **Receiver architecture**

The direct conversion receiver with automatic IQ phase calibration is shown in Fig. 1. A low noise amplifier (LNA) is placed as the first block of the receiver chain to amplify the small RF signal without adding much noise. The amplified RF signal is mixed down by two IQ mixers to generate IQ baseband signals. The variable gain amplifiers (VGAs) adjust the amplitude of the received signals. The channel filtering is done by the channel filters. Output buffers are designed to drive the off-chip impedances. A delay line (DL) is inserted into the Q side to generate an IQ phase error for measurement. The DL is composed of a resistor ( $R_{d2}$ ), a ca-

Received 28 February 2006, revised manuscript received 2 April 2006

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (Nos. 60475018,90407006,60236020) and the Science and Technology Plan of Beijing City (No. D0305003040111)

<sup>†</sup>Corresponding author. Email :pinnaxuan97 @mails. tsinghua.edu.cn

7 Ĩ Channe Output Mixer VGA -Enable/Power down filter buffer  $V_{\rm ci}$  $S_1$ VDL  $I_{IIP}$  $C_1$ NA ۰O olypha OPD LPF filter ~90 DΝ  $C_{2}$ VDL S, Channel Output buffer Mixer filter Ř<sub>d2</sub>  $C_{d2}$ Q æ DL

pacitor  $(C_{d2})$ , and a unity gain buffer. The unity

Fig. 1 Direct conversion receiver with automatic IQ phase calibration

The IQ LO signals are generated by a twostage passive polyphase filter with an external input<sup>[3]</sup>. Perfect quadrature performance is only obtained at a certain frequency point ,which is usually located at the center point of the operating band. IQ mismatch is thus unavoidable.

### **3** IQ phase calibration

#### 3.1 Calibration loop design

The IQ phase calibration loop is based on a delay locked loop (DLL)<sup>[4]</sup> using a quadrature phase detector (QPD) ,as shown in Fig. 1. In the calibration mode, the switches  $(S_1 \sim S_4)$  are turned on. The quadrature phase error between I and Q is translated to a DC voltage through the QPD, charge pump , and loop capacitor  $(C_{\rm F})$ . A unity-gain buffer is inserted between the loop capacitor and the low-pass filter (LPF) for isolation. The lowpass filtered DC voltages ( $V_{ci}$  and  $V_{cq}$ ) adjust the phase shifts of the variable delay lines  $(V_{DL})$  so that the phase difference between the I and Q signals approaches 90°. At the end of the calibration, all switches are turned off. The circuits in the dashed square are powered down. The proper control voltages are stored in the capacitors  $C_1$  and  $C_2$ .

#### 3.2 VDL design

The VDL is composed of a capacitor ( $C_{d1}$ ) and an nMOS transistor (NM<sub>d</sub>) as a variable resistor<sup>[5]</sup>, as shown in Fig. 1. NM<sub>d</sub> works in the linear region. Thus the variable resistor value  $(R_{d1})$  is inversely proportional to the gate voltage of  $NM_d(V_c)$ . The transfer function of the VDL is

gain buffer is used to drive the off-chip load.

$$\frac{V_{LOo}}{V_{LOi}} = \frac{j_{LO} R_{dl} C_{dl}}{1 + j_{LO} R_{dl} C_{dl}}$$

(1)

where LO is the LO signal frequency.

Thus the phase difference between  $V_{\rm LOo}$  and  $V_{\rm LOi}$  is

$$Ph_{dif} = 90^{\circ} - tan^{-1} (L_0 R_{d1} C_{d1})$$

(2)

Since  $R_{d1}$  is controlled by  $V_c$ , the phase difference between  $V_{LO_0}$  and  $V_{LO_i}$  can be adjusted by changing  $V_c$ . In this design,  $C_{d1}$  is set to be 0. 6p F and the transistor  $NM_d$  size is  $20\mu m/0$ .  $35\mu m$ .

### 3.3 QPD design

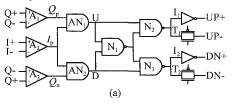

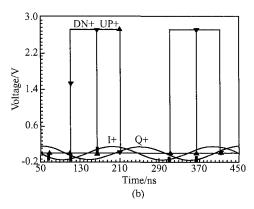

The QPD schematic is shown in Fig. 2 (a). Amplifiers  $A_1$ ,  $A_2$ , and  $A_3$  convert sinusoidal inputs into square waves  $(I_p, Q_p, and Q_n)$ . To minimize common mode effects on the duty cycle of the square waves, these amplifiers are designed with differential inputs. The UP signal is simply the product of  $I_p$  and  $Q_p$ , and the DN signal is the product of  $I_p$  and  $Q_n$ . Because the transition edge of AND gates AN1 and AN2 cannot be a step change, there exists a positive pulse overlap of the UP and DN signals. NAND gates N1, N2, and N3 are used to eliminate this pulse overlap, so that the up and down current sources in the charge pump will not be turned on simultaneously. Inverters  $(I_1 \text{ and } I_2)$ and transmission gates  $(T_1 \text{ and } T_2)$  convert singleended inputs to differential outputs to minimize the effects of switches on current sources in the charge

pump. A phase difference between the I and Q signals results in unequal positive pulse widths of the UP and DN signals<sup>[4]</sup>.

Figure 2 (b) shows the simulation waveforms when the signal frequencies of I and Q are 10M Hz and the quadrature phase error is about 5°. The positive pulse width of UP + is smaller than that of  $DN^+$ , resulting in a decrease in the charge pump output voltage.

Fig. 2 Quadrature phase detector (a) Schematic diagram; (b) Waveforms with 10M Hz inputs

#### 3.4 Charge pump design

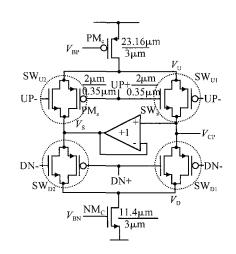

Figure 3 gives a simplified schematic of the current charge pump. The sizes of transistors  $PM_c$  and  $NM_c$  are set to be 23.  $16\mu$ m/  $3\mu$ m and 11.  $4\mu$ m/  $3\mu$ m. The channel length of the transistor is chosen to be  $3\mu$ m to make the ratio of transistor width to length less sensitive to process variance. A smaller size of  $2\mu$ m/ 0.  $35\mu$ m is chosen for all of the switching transistors to minimize capacitive coupling between UP (DN) and V<sub>CP</sub>.

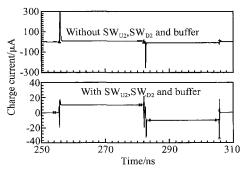

Because  $SW_{U1}$  and  $SW_{D1}$  are turned on alternately,  $V_U (V_D)$  does not follow  $V_{CP}$  when  $SW_{U1}$  ( $SW_{D1}$ ) is off. This results in glitches in the charge current at the moment when  $SW_{U1}$  (or  $SW_{D1}$ ) is turned on.  $SW_{U2}$ ,  $SW_{D2}$ , and a unity gain buffer are used to reduce the glitches. For example, when  $SW_{D1}$  is turned on,  $SW_{U2}$  is on and  $SW_{U1}$  and  $SW_{D2}$  are off. Thus,  $V_U$  varies with  $V_S$ . Since  $V_S$  is almost identical to  $V_{CP}$ ,  $V_U$  thus equivalently follows  $V_{CP}$ . Therefore,  $V_U$  does not experience a

1533

Fig. 3 Simplified schematic of the charge pump

step change when  $SW_{U1}$  is turned on. The glitches in the current through  $SW_{U1}$  are consequently reduced. Figure 4 shows that the current glitches are reduced from nearly 300 to  $30\mu A$ .

Fig. 4 Reduction of charge pump current glitches

### 3.5 Resolution analysis

In a real QPD circuit, there exists a width mismatch between the positive pulse widths ( $T_{\rm UP}$  and  $T_{\rm DN}$ ) of the UP and DN signals when I and Q are exactly in quadrature. There is also a mismatch between  $I_{\rm UP}$  and  $I_{\rm DN}$ . For a phase error of d er between I and Q, the voltage increment of V<sub>ci</sub> or V<sub>cq</sub> after n signal cycles is

$$dV_{n} = \frac{TI_{0}}{4C_{F}}(+-\frac{-d_{er}+d_{1}+...+d_{n-1}}{90^{\circ}})$$

(3)

where is the mismatch between  $T_{UP}$  and  $T_{DN}$ , is the mismatch between  $I_{UP}$  and  $I_{DN}$ , T is the signal cycle of I and Q,  $I_0$  is the ideal charge pump current, and d<sub>i</sub> is the phase shift between I and Q caused by dV<sub>i</sub>. If dV<sub>n</sub> equals zero, the loop locks. Thus the residual phase error after calibration is

$(-d_{er} + d_1 + ... + d_{n-1}) = 90^{\circ} \times (+)$

Equation (4) shows that the residual phase error (namely calibration resolution) is directly proportional to the QPD and charge pump mismatches. Ideally, and are both zero, which means the calibration resolution is 0°. Careful design of the QPD and charge pump reduces + to be about 0. 4% on average ,resulting in a 0. 36° residual phase error<sup>[4]</sup>.

### 4 Simulation results

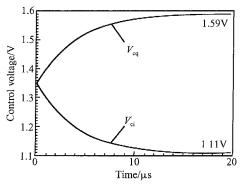

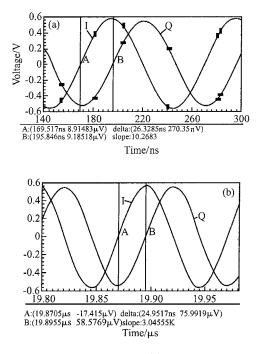

The receiver with the calibration loop is simulated using Cadence Spectre RF with a 0. 18µm CMOS process and a 2. 7V supply voltage. The RF input signal and the LO signal are set at 2. 41 GHz and 2. 4 GHz, respectively. Thus the baseband signal for calibration is 10MHz. The loop filter  $C_F$  is set at 3. 6pF. The resistor  $R_{d2}$  and capacitor  $C_{d2}$  in the DL are set at 1. 4k and 1pF to generate a 5° quadrature phase error between I and Q. Figure 5 plots the waveforms of  $V_{ci}$  and  $V_{cq}$  during the calibration process. Figure 6 plots the waveforms of I and Q before and after calibration. The initial 5° phase error is reduced to only 0. 18°.

Fig. 5 V<sub>ci</sub> and V<sub>cq</sub> lock-in process

### 5 Layout design and measured results

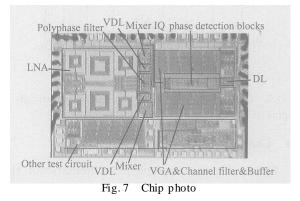

This design has been fabricated in a 0.  $18\mu$ m CMOS process. The chip was bonded in a 24-pin QUAD package. A photo of the chip is shown in Fig. 7, including the receiver and some other test circuits. The receiver size is about 2.  $3mm^2$ .

#### 5.1 Layout design

The receiver layout is made as symmetrical as possible to improve its quadrature performance, as shown in Fig. 7. The IQ phase detection blocks, including the QPD, charge pump, loop filter, buffer,

Fig. 6 Waveforms of I and Q (a) Before calibration; (b) After calibration

and LPF, are placed between the I and Q baseband paths to maintain the layout symmetry. The two VDLs are also placed symmetrically on the LO signal paths.

#### 5.2 Measured results

The whole calibration circuit consumes about 1. 8mA in calibration mode and less than 2nA in power-down mode from a 2. 7V supply. The RF signal is 2. 41 GHz and the LO signal is 2. 4 GHz.

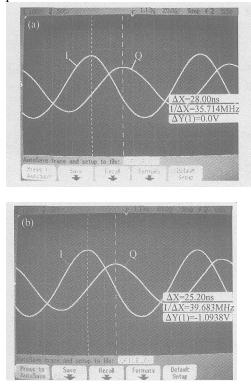

The IQ signals are measured using an Agilent 54622D 100M Hz mixed signal oscilloscope. Figure 8(a) shows that the time difference between I and Q before calibration is about 28ns. Thus the IQ phase error is  $28/100 \times 360^{\circ}$ -  $90^{\circ}$ = 10. 8 °. In addition to the 5 ° phase error of the DL, the receiver

contributes an extra 5. 8 °phase error. Figure 8(b) shows that the time difference after calibration is about 25. 2ns. The IQ phase error is thus 25. 2/100  $\times 360$  °- 90 °= 0. 72 °. The measured results show that the calibrated IQ phase error is smaller than the requirement of 1 °.

Fig. 8 Measured I/Q waveforms (a) Before calibration; (b) After calibration

The measured performance departs somewhat from the simulation result. The possible reason is that the QPD and charge pump performances are not as good as in the simulation. Figure 8 also shows that the IQ amplitude error is a bit large, which needs to be eliminated in future design.

### 6 Performance comparison

The receiver IQ phase calibration methods can be classified into categories: (1) digital calibration implemented in the baseband DSP chip<sup>[6,7]</sup>; (2) mixed method of analog and digital calibration with the help of the DSP chip<sup>[8]</sup>; (3) calibration integrated in the transceiver chip<sup>[9,10]</sup>. Calibration methods of (1) and (2) rely on the baseband DSP chips ,which increases the complexity of the baseband DSP chips and lowers the compatibility between the transceiver chips and the baseband DSP chips. The selection range of DSP chips for transceiver providers is also reduced. Thus method (3) is preferred for both transceiver and baseband DSP chip providers. The IQ phase calibration method proposed in this design is classified into method (3).

The calibrated IQ phase errors are  $0.3^{\circ}$  in Ref. [9] and  $1^{\circ}$  in Ref. [10]. Thus the measured performance of this design is between the results of Refs. [9] and [10], all satisfying the system requirement of  $1^{\circ}$ .

### 7 Conclusions

An automatic IQ phase calibration method implemented in a 2.4 GHz direct conversion receiver is presented. The calibration loop is based on a delay locked loop using a proposed quadrature phase detector (QPD). The QPD schematic and the loop resolution are given and analyzed. The receiver has been fabricated in a 0. 18µm CMOS process. Measurements show that the IQ phase error after calibration is less than 1°, which satisfies the system requirements.

#### References

- [1] Razavi B. Design considerations for direct-conversion receivers. IEEE Trans Circuits and System : Analog and Digital Signal Processing, 1997, 44 (6):428

- [2] Ahola R, Aktas A, Wilson J, et al. A single-chip CMOS transceiver for 802. 11a/ b/g wireless LANs. IEEE J Solid-State Circuits, 2004, 39(12):2250

- [3] Behbahani F, Kishigami Y, Leete J, et al. CMOS mixers and polyphase filters for large image rejection. IEEE J Solid-State Circuits ,2001,36(6):873

- [4] Liu Ruifeng ,Li Yongming ,Chen Hongyi. Analysis and design of an auto-IQ phase calibration circuit based on DLL using a quadrature phase detector. Analog Integrated Circuits and Signal Processing ,accepted

- [5] Sanderson D I, Svitek R M, Raman S. A 5-6-GHz polyphase filter with tunable I/Q phase balance. IEEE Microwave and Wireless Components Letters, 2004, 14(7):364

- [6] Vassiliou I, Vavelidis K, Georgantas T, et al. A single-chip digitally calibrated 5. 15-5. 825-GHz 0. 18-µm CMOS transceiver for 802. 11a wireless LAN. IEEE J Solid-State Circuits, 2003, 38(12):2221

- [7] Vitali S, Franchi E, Gnudi A. A gain/phase mismatch calibration procedure for RF I/Q downconverters. IEEE International Symposium on Circuits and Systems, 2005, 3:2108

- [8] Zhang Pengfei, Nguyen T, Lam C, et al. A 5-GHz direct-conversion CMOS transceiver. IEEE J Solid-State Circuits, 2003,38(12):2232

- [9] Ahola R, Aktas A, Wilson J, et al. A single-chip CMOS transceiver for 802. 11a/ b/g wireless LANs. IEEE J Solid-State

Circuits ,2004 ,39(12) :2250 [10] Hsieh Y H, Hu W Y, Lin S M, et al. An auto-I/Q calibrated CMOS transceiver for 802. 11g. IEEE J Solid-State Circuits, 2005,40(11):2187

## 2.4GHz 零中频接收机中正交相位的自校准设计\*

刘瑞峰† 李永明 陈弘毅 王志华

(清华大学微电子学研究所,北京 100084)

摘要:提出了实现在一个24GHz零中频接收机中的一种正交相位自校准方法.这种方法基于一个采用提出的正 交相位检测器的延迟锁定环路来大大减小正交相位误差.该接收机采用0.18µm CMOS 工艺实现.测试结果显示 正交相位误差可以被校准到13以内,满足了系统的要求.

关键词:零中频接收机;正交相位校准;CMOS 工艺;正交相位检测器

EEACC: 1205; 2570D

中图分类号:TN402

文献标识码:A

文章编号: 0253-4177(2006)09-1531-06

<sup>\*</sup>国家自然科学基金(批准号:60475018,90407006,60236020)和北京市科技计划(批准号:D0305003040111)资助项目

<sup>†</sup>通信作者. Email :pinnaxuan97 @mails. tsinghua. edu. cn