## 高散热变 k 介质埋层 SOI 高压功率器件 $^*$

### 罗小蓉\* 李肇基 张 波

(电子科技大学 IC 设计中心,成都 610054)

摘要:针对常规 SOI 器件纵向耐压低和自热效应两个主要问题,提出了变 k 介质埋层 SOI(variable k dielectric buried layer SOI,VkD SOI)高压功率器件新结构.该结构在高电场的漏端采用低 k 介质以增强埋层电场,在高电流密度的源端附近采用高热导率的氮化硅埋层,从而器件兼具耐高压和降低自热效应的优点.结果表明,对于  $k_1$  = 2,  $k_2$  = 7.5(Si<sub>3</sub> N<sub>4</sub>),漂移区厚 2 $\mu$ m,埋层厚 1 $\mu$ m 的器件,埋层电场和器件耐压分别达 212V/ $\mu$ m 和 255V,比相同厚度的常规 SOI 器件的埋层电场和耐压分别提高 66%和 43%,最高温度降低 52%.

关键词: SOI; 低 k 介质埋层; 纵向电场; 击穿电压; 自热效应

EEACC: 2560B; 2560P

中图分类号: TN386 文献标识码: A 文章编号: 0253-4177(2006)10-1832-06

#### 1 引言

SOI 器件的高速、低功耗、高集成度以及便于隔 离等优越性能使其在 VLSI 领域得到广泛关注[1]. 但 SOI 器件有两个重要缺点——较低的纵向击穿 电压和自热效应.近年来,学者们提出了一系列新结 构以提高器件纵向耐压,如在Si层/埋氧层的界面 插入 n<sup>+</sup> 薄层<sup>[2]</sup>、SIPOS 层<sup>[3]</sup>、屏蔽槽 SOI 结构<sup>[4~6]</sup>、 可变低 k 介质层 SOI 结构<sup>[7]</sup>. Merchant 等人还设 计了超薄漂移区横向线性掺杂 SOI 结构[8]. 但这些 方法都未能缓解自热效应,其中后两种方法使自热 效应更为突出. 硅窗口在源端的 partial SOI(PSOI) 结构既能提高纵向耐压,又能克服自热效应[9,10],但 是它却牺牲了 SOI 寄生电容小、无衬底漏电流的优 点;后有人提出采用热导率高的 Si<sub>3</sub>N<sub>4</sub> 替代 SiO<sub>2</sub> 作 为埋层以降低自热效应[11,12],但  $Si_3N_4$  的高 k 降低 了埋层纵向电场和器件纵向耐压,突显了 SOI 器件 纵向耐压低的弱点.

本文在对可变低 k 介质层 SOI(variable low k dielectric layer, VLkD SOI) 高压器件研究的基础上<sup>[77]</sup>,提出 VkD SOI LDMOS 高压功率器件新结构. 该结构将热导率高的 Si<sub>3</sub>N<sub>4</sub> 引入电流密度高的源端以降低自热效应,在电场最强的漏端采用低 k 介质埋层提高器件纵向耐压,同时,不同 k 的埋层对横向电场的调制作用使器件横向耐压提高. 另外,漏端低 k 埋层可降低漏极-衬底间的电容,提高开关频率. 借助二维器件仿真器 MEDICI 研究了击穿特

性和热特性与器件结构参数的关系. 结果表明, VkD SOI 结构能在提高器件耐压和缓解自热效应 二者之间取得良好折中.

#### 2 耐压机理

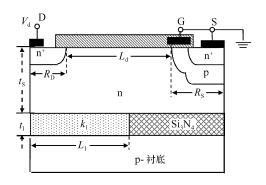

VkD SOI LDMOS 器件结构如图 1 所示.该结构源端采用  $Si_3N_4$  埋层,漏端采用低 k 介质埋层.图中  $t_s$ ,  $t_1$  分别代表 Si 层和埋层厚度,  $k_1$  代表低 k 介质的介电常数,  $Si_3N_4$  的介电常数  $k_2$  = 7.5,  $L_d$ ,  $L_1$  分别表示漂移区长度、低 k 介质层长度, $R_D$ ,  $R_S$  分别为漏区、源区宽度. 假定器件的横向设计应用了场板和 RESURF 等技术,耐压由纵向决定,则击穿发生在电场最强的漏端下方的 Si 层/埋层界面 Si 侧.在漏端 Si/埋层界面,电位移连续性为:

$$k_1 E_1 = k_S E_S$$

$k_1 \frac{V_1}{t_1} = k_S \frac{V_S}{t_S}$  (1)

其中  $k_s$ ,  $E_s$  分别是 Si 层的介电常数和电场;  $E_1$ ,  $V_1$  是埋层的电场和耐压. 从(1)式可见,降低  $k_1$  可以增强埋层电场,提高器件纵向耐压,从而可在相同埋层厚度下增加耐压或在相同击穿电压下降低埋层的厚度.

另一方面,该结构可以优化表面电场.变 k 埋层界面处的附加场对表面电场的调制作用使器件表面出现新的电场峰,同时,新的电场峰又降低源结和漏结的电场峰,使表面电场优化,避免表面提前击穿,从而提高器件横向耐压.根据 SOI 结构的 RE-

<sup>\*</sup> 国家自然科学基金(批准号:60436030)和模拟 IC 国家重点实验室基金(批准号:9140C0903050605)资助项目

<sup>†</sup>通信作者.Email:xrluo@uestc.edu.cn

图 1 VkD SOI LDMOS 结构剖面图 Fig. 1 Cross section of VkD SOI LDMOS

SURF 原理[7,13],均匀掺杂的 VkD SOI 结构相当于常规 SOI 结构的漂移区阶梯掺杂,VkD SOI 结构的低 k 端类似于普通 SOI 结构高掺杂的漏端、高 k 端类似于普通 SOI 结构低掺杂的源端. 该结构在不同 k 的埋层界面相应处产生新的表面电场峰.

#### 3 结果与讨论

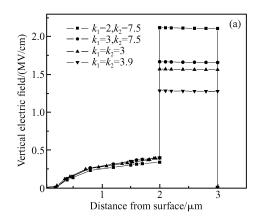

为了验证上述耐压机理的正确性,首先讨论漏 端下纵向电场和电势分布. 图 2 为  $VkD(k_1 = 2,3,$  $k_2 = 7.5$ ) SOI, Lk(low  $k, k_1 = k_2 = 3$ ) SOI 和常规  $SOI(k_1 = k_2 = 3.9)$ LDMOS 在各自击穿电压(分别 为 255,217,206 和 178V)下漏端纵向电场和电势分 布图. 由图可见,漏端下埋层纵向电场  $E_1$  取决于  $k_1, k_1$  越小,  $E_1$  愈大, 但对同样的  $k_1$ , VkD SOI( $k_1$ =3, $k_2$ =7.5)的  $E_1$  高于 Lk SOI( $k_1$ = $k_2$ =3).这 是由于 VkD 结构变 k 介质埋层产生的附加场对漂 移区电场的调制使表面电场出现新的电场峰(图3 中 A,B 峰),表面电场更均匀;横向电场同时又对纵 向电场进行调制,故其击穿电压更高.对  $k_1 = 2, k_2$ = 7.5,  $t_1$  = 1 $\mu$ m 的 VkD LDMOS, 埋层电场和器件 耐压分别为  $212V/\mu m$  和 255V, 比常规 SOI 结构分 别提高了66%和43%.几种结构的纵向电势分布如 图 2(b) 所示. 该图表明, 几种结构的顶层 Si 耐压  $(V_s = V(0) - V(t_s))$ 几乎相同, VkD 和 Lk SOI 埋 层承受的电压( $V(t_s)$ )比常规 SOI 的更高.

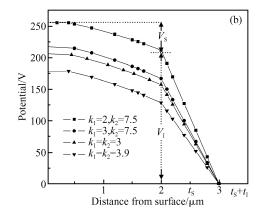

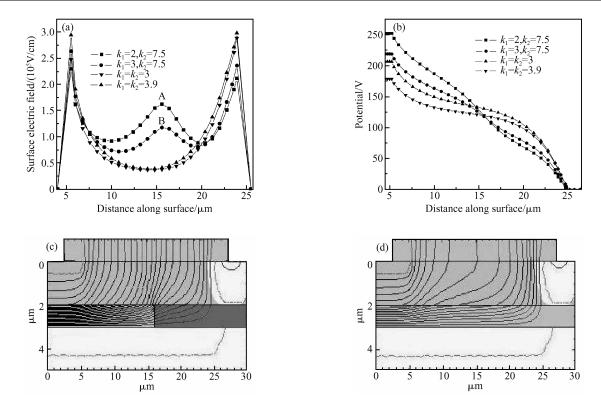

图 3 给出了以上几种结构的表面电场和电势分布.图 3(a)表明,VkD 结构在两种介质埋层的交界处引入了新的表面电场峰 A 和 B, $k_1$ , $k_2$  相差越大,新的电场峰愈高,这样对源结和漏结电场峰的削弱也越明显,从而避免表面提前击穿,提高了器件的耐压.当 $k_1 = k_2$  时,无新电场峰,源结和漏结电场峰较高,器件耐压降低.图 3(b)显示,Lk SOI 和常规 SOI 的表面电势分布呈现明显台阶分布,即源结和漏结的分压较高,该处等势线分布密集;漂移区等

图 2 纵向电场(a)和纵向电势(b)分布 Fig.2 Vertical electric field (a) and potential (b) distributions  $t_{\rm S}=2\mu{\rm m}$ ,  $t_{\rm I}=1\mu{\rm m}$ ,  $L_{\rm d}=20\mu{\rm m}$ ,  $L_{\rm I}=L/2+R_{\rm D}$

势线分布稀疏,其承受电压较低.而 VkD 结构的漂移区等势线分布均匀,表面电势近似为线性分布,因而耐压更高. VkD SOI 和常规 SOI 结构的二维电势分布如图 3(c),(d)所示. 图中相邻两条等势线间电压降约为 10V.

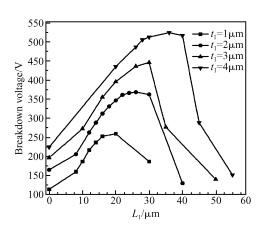

图 4 为击穿电压 BV 与  $L_1$  的关系. 该图表明,对相同的  $t_1$ ,击穿电压随  $L_1$  的增加先增加后减小,当  $L_1$  为  $R_D$  +  $L_d/2 < L_1 < L_d$  +  $R_D$  时,击穿电压最高. 这是由于低 k 介质埋层的电场更强,能够分担更高的电压,因而降低了 Si 有源层的电场,避免 Si 层提前击穿,故  $L_1$  越长,器件耐压越高. 但当  $L_1$  太长时,新的表面电场峰距离漏结过远、距离源结过近,这样对漏结、源结电场的调制作用不相当,导致表面电场不均匀,特别是当  $L_1 \approx L_d + R_D$  时,新的电场峰与源结峰值叠加,致使源结表面提前击穿,耐压降低. 仿真结果表明,当  $L_1 = L_d + R_D$  时,器件耐压比 Lk SOI( $L_1 = L_d + R_D + R_s$ )甚至更低. 图 4显示,VkD SOI 结构的击穿电压较 Lk 和 Hk SOI (high k,  $L_1$  = 0)结构击穿电压提高,且均随  $t_1$  的增加而增大.

表 3 表面电场和电势分布 (a)表面电场分布;(b)表面电势分布;(c) Vk 结构二维等势线分布;(d)常规 SOI 结构二维等势线分布

Fig. 3 Surface electric field distribution, surface potential distribution and equi-potential contours under breakdown voltage (a) Surface electric field distribution; (b) Surface potential distribution; (c) Equi-potential contours of Vk structure; (d) Equi-potential contours of conventional SOI structure

图 4 击穿电压与  $L_1$  的关系

Fig. 4 Dependence of breakdown voltage on  $L_1$

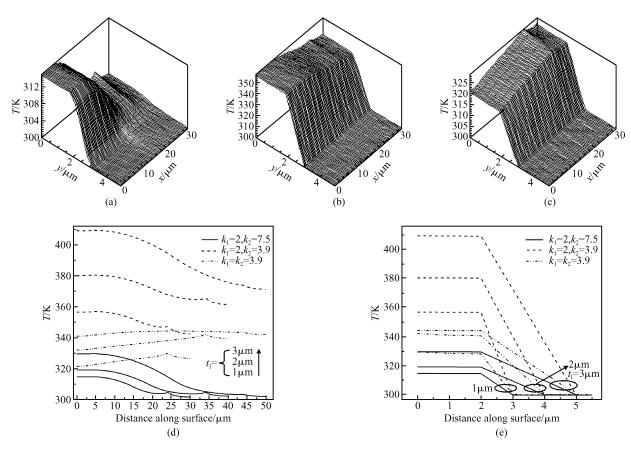

VkD SOI 结构中 Si<sub>3</sub>N<sub>4</sub> 埋层的热导率(30W/(m・K))约为 SiO<sub>2</sub>(1.4W/(m・K))的 20 余倍,更远高于低 k 介质(0.11~0.19W/(m・K)). 因而将 Si<sub>3</sub>N<sub>4</sub> 引入 SOI 埋层大大缓解了自热效应. 图 5 是在源极和衬底接地、衬底温度固定为室温(300K),  $V_g = 10V$ ,功耗为  $1mW/\mu m$  情况下,VkD SOI 结构  $(k_1 = 2, k_2 = 7.5, L_1 \approx L_d/2 + R_D)$ ,VLkD SOI( $k_1$

= 2,  $k_2$  = 3. 9,  $L_1 \approx L_d/2 + R_D)^{[7]}$  和常规 SOI LD-MOS 的温度分布. 仿真中采用各结构优化的漂移区浓度. 其中图 5(a),(b)和(c)是三种结构在  $t_1$  =  $1\mu$ m 时的三维温度分布,图 5(d),(e)是三种结构的表面温度分布和最高表面温度处的纵向温度分布.由图 5 可知,当介质埋层厚度相同时,VkD 结构的有源区温度最低,VLkD SOI 结构温度最高,二者最高温度均在低 k 介质端,前者为 314K,后者为 358K.

常规 SOI 结构的最高温度在电流密度最大的沟道处,其最高温度为 329K. 三种结构的有源区温度均随  $t_1$  的增加而增加,VkD SOI 结构增加最慢,VLkD SOI 结构增加最快.

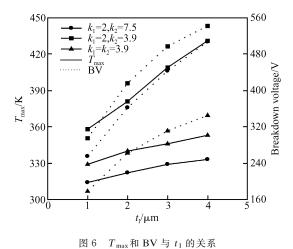

图 6 给出了以上三种结构的最高温度  $T_{\text{max}}$ 和击穿电压 BV 与埋层厚度  $t_1$  的关系. 由图 6 可知,对相同的  $t_1$ , VkD SOI 的  $T_{\text{max}}$ 最低,其随  $t_1$  的增加缓慢增加; VLkD SOI 结构的  $T_{\text{max}}$ 最高且随  $t_1$  的增加迅速升高. 图 6 表明, VLkD SOI 结构的击穿电压最高, VkD SOI 结构的击穿电压略低,常规 SOI 结构的击穿电压最低. 在本文讨论的埋层厚度范围内  $(1\sim 4\mu\text{m})$ , VkD SOI 结构的击穿电压较常规结构提高  $38\%\sim 47\%$ ,最高温度降低  $37\%\sim 52\%$  (文中

最高温度的比较均以高于衬底的温度作为计算标准);与 VLkD SOI 结构比较, VkD SOI 结构的最高温度降低 73%~77%, 击穿电压仅降低 10.7%~

11.6%.由此说明, VkD SOI 器件结构在提高耐压的同时能大大缓解自热效应.

图 5 三种结构的温度分布 (a) VkD  $SOI_{*}(b)$  VLkD  $SOI_{*}(c)$  常规  $SOI_{*}(d)$  表面温度 $_{*}(e)$  表面温度最高点处的纵向温度分布

Fig. 5 Temperature distributions of the devices (a) VkD SOI; (b) VLkD SOI; (c) Conventional SOI; (d) Surface temperature; (e) Vertical temperature distribution at the maximum surface

Fig. 6 Dependence of  $T_{\text{max}}$  and BV on  $t_1$

$\begin{array}{c} 650 \\ 600 \\ \hline -k_1 = 2, k_2 = 7.5 \\ \hline -k_1 = 2, k_2 = 3.9 \end{array} \begin{array}{c} 450 \\ 400 \\ \hline -350 \\ \hline -300 \\ \hline -300 \\ \hline -300 \\ \hline -250 \\ \hline -200 \\ \hline -300 \\ \hline -200 \\ \hline -300 \\ \hline -200 \\ \hline -150 \\ \hline -100 \\ -100 \\ \hline -100 \\ -100 \\ \hline -100 \\ \hline -100 \\ -100 \\ \hline -100 \\ \hline -100 \\ \hline -100 \\ -100 \\ \hline -100 \\ -100 \\ \hline -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100 \\ -100$

图 7  $T_{max}$ 和 BV 与  $L_1$  的关系 Fig.7 Dependence of  $T_{max}$  and BV on  $L_1$

图 7 给出了器件最高温度和击穿电压 BV 与  $L_1$  的关系. 由图 7 可以看出,随着  $L_1$  的增加,即低

热导率的低 k 介质的长度增加,器件最高温度不断上升.特别是当  $L_1 = 0$  时,埋层全为  $Si_3N_4$ ,其温度

最低; 当  $L_1 = L_d + R_D + R_S$ , VkD SOI 结构器件变为 Lk SOI 结构,器件最高温度急剧上升. 与热特性不同的是,击穿电压随  $L_1$  的增加先增加后减小,当  $L_1 = 0$  时,其击穿电压最低. 因而,综合考虑热特性和击穿特性,仅当  $L_1 \approx L_d/2 + R_D$  时,能够获得二者的良好折中,这是 VkD SOI 器件结构的优化设计原则.

部分低 k 介质具备低泄漏电流、高附着力、高 硬度、高稳定等性能,可望作为 SOI 材料的埋层.如 SiOF 保留了较多 SiO<sub>2</sub> 的性质,与已有的 SiO<sub>2</sub> 工艺 很好地兼容, k 在 2.8~3.7 之间, 临界击穿电场  $9.2\sim10.1 MV/cm^{[14\sim16]}$ . 氟的加入使其抗湿性能变 差,可以采用对 SiOF 薄膜掺碳的方法加以改进.制 备掺碳的 SiOF 薄膜有两种方法:其一是用 CF₄ 直 接注人已制备好的 SiO<sub>2</sub> 薄膜而得到;其二是直接以 SiH<sub>4</sub>/O<sub>2</sub>/CF<sub>4</sub>/CH<sub>4</sub> 或 CH<sub>4</sub>/FTES/O<sub>2</sub> 混合气体产 生等离子体淀积形成掺碳的 SiOF 薄膜, k 在 2.5~ 2.8之间,同时也表现出较好的热稳定性[16~18].当 采用原料中 C<sub>4</sub>F<sub>8</sub> 对四乙基原硅酸盐(TEOS)的比 例为 1.8 时,介电常数在 1MHz 频率下的值能降到 2. 35<sup>[19]</sup>. 掺碳的 SiOF 薄膜已被用于 ULSI 的金属 化工艺中,成为比较成熟的技术.第二代(超)低 k材料 SiCOH 薄膜 k 值可由先前的 2.4 降至 2.1,且 可进一步降低 k 值至 1.95<sup>[20~22]</sup>. IBM, Sony 以及 Toshiba 等公司联合研发,获得了性能优良的 90nm SOI/Cu/SiCOH 集成电路<sup>[23]</sup>. 2005 年 11 月 IEDM 报道的富士通采用相对介电常数为 2.25 的低 k 介 质获得 45nm 低功耗 CMOS,其功耗比 65nm 产品 降低一半.目前,因低 k 材料技术难度和成本问题 等因素,尚未大规模应用于实际集成电路生产工艺 中.

对于本文的 VkD 结构,低 k 介质可用掺碳的 SiOF 薄膜.采用 Smart-cut 的方法制备变 k 介质埋层 SOI 材料,工艺流程如下: Si 衬底氧化→淀积 Si<sub>3</sub> N<sub>4</sub>→局部干法刻蚀 Si<sub>3</sub> N<sub>4</sub>→注入 CF<sub>4</sub> 形成局部 掺碳 SiOF→Si<sub>3</sub> N<sub>4</sub> 剥离→双面光刻(将埋层的介质分布标记于衬底背面)→平坦化→与另一注氢 Si 片键合→剥离→双面光刻(将衬底背面的标记转移到有源层).为了保证键合质量,版图设计时,可使常规 SOI 结构与 VkD 结构交错排列,同时,VkD 结构的低 k 区可以较短.

#### 4 结论

本文提出了变 k 介质埋层 SOI 功率器件新结构. 该结构将热导率高的 Si<sub>3</sub> N<sub>4</sub> 引入源端以降低自热效应,利用漏端低 k 介质提高器件纵向耐压;同时,变 k 埋层对表面电场的调制作用使器件横向耐

压提高.结果表明,在埋层厚度为  $1\sim 4\mu m$ ,当  $L_1 \approx L_d/2 + R_D$  时,VkD SOI 结构的击穿电压较常规结构提高  $38\%\sim47\%$ ,最高温度降低  $37\%\sim52\%$ ;与VLkD SOI 结构比较,VkD SOI 结构的击穿电压降低  $10.7\%\sim11.6\%$  左右,但 VLkD 的最高温度为VkD 的  $3.64\sim4.36$  倍.可见,VkD SOI 器件结构在提高耐压的同时还能大大缓解自热效应,特别适合于制作高压功率器件.

#### 参考文献

- [1] Udrea F, Garner D, Sheng K, et al. SOI power devices. Electronics & Communication Engineering Journal, 2000, 12(1):

- [2] Nakagawa A, Yasuhara N, Baba Y. Breakdown voltage enhancement for devices on thin silicon layer/silicon dioxide film. IEEE Trans Electron Devices, 1991, 38(7):1650

- [3] Funaki H, Yamaguchi Y, Hirayama K, et al. New 1200V MOSFET structure on SOI with SIPOS shielding layer. Proc IEEE ISPSD, 1998;25

- [4] Kapels H, Plikat R, Silber D. Dielectric charge traps: a new structure element for power devices. Proceeding of ISPSD, 2000.205

- [5] Luo Xiaorong, Li Zhaoji, Zhang Bo, et al. A novel structure and its breakdown mechanism of SOI high voltage device with shielding trench. Chinese Journal of Semiconductors, 2005,26(11);2154(in Chinese)[罗小蓉,李肇基,张波,等.屏蔽槽 SOI 高压器件新结构和耐压机理.半导体学报,2005,26(11);2154]

- [6] Luo Xiaorong, Li Zhaoji, Zhang Bo. A novel E-SIMOX SOI high voltage device structure with shielding trench. IC-CCAS, 2005:1403

- [7] Luo Xiaorong, Li Zhaoji, Zhang Bo. Breakdown characteristics for SOI LDMOS high voltage device with variable low *k* dielectric layer. Chinese Journal of Semiconductors, 2006, 27 (5):881(in Chinese)[罗小蓉,李肇基,张波,可变低 *k* 介质层 SOI LDMOS 高压器件耐压特性. 半导体学报, 2006, 27 (5):881]

- [8] Merchant S, Arnold E, Baumgart H, et al. Realization of high breakdown voltage (>700V) in thin SOI device. Proc 3rd Int Symp Power Semiconductor Devices and ICs, 1991;31

- [9] Tadikonda R, Hardikar S, Narayanan E M S. Realizing high breakdown voltages (>600V) in partial SOI technology. Solid-State Electron, 2004, 48:1655

- [10] Luo Xiaorong, Zhang Bo, Li Zhaoji, et al. A novel SOI high voltage device structure with partial locating charge trench. Chinese Journal of Semiconductors, 2006, 27(1):193(in Chinese) [罗小蓉,张波,李肇基,等.部分局域电荷槽 SOI 高压器件新结构.半导体学报, 2006, 27(1):193]

- [11] Liu Qibin, Lin Qing, Liu Weili, et al. Fabrication and simulation of silicon-on insulator structure with  $Si_3N_4$  as buried insulator. Chinese Journal of Semiconductors, 2005, 26 (9): 1722

- [12] Tadikonda R, Hardikar S, Narayanan E M S, et al. Potential of high-k dielectric for lateral power and high voltage device. Proceeding of MIEL, 2004:129

- [13] Guo Yufeng, Fang Jian, Zhang Bo, et al. A 2D analytical model of SOI double RESURF effect. Chinese Journal of

- Semiconductors,2005,26(4):33(in Chinese)[郭宇锋,方健, 张波,等.SOI 基双级 RESURF 二维解析模型. 半导体学报, 2005,26(4):33]

- [14] Grill A, Patel V. Low dielectric constant films prepared by plasma-enhanced chemical vapor deposition from tetramethylsilane. J Appl Phys, 1999, 85(6):3314

- [15] Lee S, Park J W. Effect of postplasma treatment on characteristics of electron cyclotron resonance chemical vapor deposition SiOF films. J Vac Sci Technol A, 1999, 17(2):458

- [16] Wang Pengfei, Ding Shijin, Zhang Wei, et al. CVD technologies used in preparation of low dielectric constant materials for ULSI. Microfabrication Technology, 2001, 1:30 (in Chinese) [王鹏飞,丁士进,张卫,等. ULSI 低介电常数材料制备中的 CVD 技术. 微细加工技术, 2001, 1:30]

- [17] Yun S M, Chang H Y, Kang M S, et al. Low dielectric constant films CF/SiOF composite film deposition in a helicon plasma reactor. Thin Solid Films, 1999, 341, 109

- [18] Lubguban J Jr, Saitoh A, Kurata Y, et al. Stability of the dielectric properties of PECVD deposited carbon-doped SiOF films. Thin Solid Films, 1999, 337:67

- [19] Ding S J. Chen L, Wan X G, et al. Structure characterization of carbon and fluorine—doped silicon oxide films with low dielectric constant. Mater Chem Phys, 2001, 71(2):125

- [20] Kinoshita K, Takahashi H, Fvijii N. Recovery of plasma process induced damage in porous silica low-k films by organosiloxane vapor post annealing. ICICDT, 2005:107

- [21] Huang Rao, Liu Zhijing. Recent research and development of low dielectric constant materials. Micro-nanoelectronic Technology, 2003, 9:11 (in Chinese) [黄娆,刘之景. 新型低介电常数材料研究进展. 微纳电子技术, 2003, 9:11]

- [22] Wang Tingting, Ye Chao, Ning Zhaoyuan, et al. Characterization and bonding configuration of SiCOH low-k films. Acta Physica Sinica, 2005, 54(2):892(in Chinese)[王婷婷, 叶超,宁兆元,等. SiCOH 低介电常数薄膜的性质和键结构分析. 物理学报, 2005, 54(2):892]

- [23] Edelstein D, Davis C, Clevenger L. Reliability, yield, and performance of a 90nm SOI/Cu/SiCOH technology. Proceedings of International Interconnect technology Conference, 2004; 214

# A Highly Heat-Dissipating SOI High Voltage Power Device with a Variable k Dielectric Buried Layer\*

Luo Xiaorong<sup>†</sup>, Li Zhaoji, and Zhang Bo

(IC Design Center, University of Electronic Science and Technology of China, Chengdu 610054, China)

Absract: Aiming at two main problems of SOI device—the low vertical breakdown voltage and self-heating effect—a novel SOI high-voltage power device with a variable-k dielectric layer (VkD) is proposed. A low-k dielectric is used to enhance the electric field of the buried layer on the drain side with a high electric field, and a high-thermal conductivity dielectric is used near the source side where the current density is large. The device thus can sustain a high voltage while simultaneously reducing the self-heating effect simultaneously. The results show that an electric field in the buried layer of  $212V/\mu m$  and a breakdown voltage of 255V can be obtained for a VkD structure with a  $2\mu m$ -thick Si layer and a  $1\mu m$  buried layer with low  $k_1 = 2$ . Compared with conventional SOI, the electric field of the buried layer and breakdown voltage of the VkD SOI are enhanced by 66% and 43%, respectively. The maximum temperature of the device is lowered by 52%.

**Key words:** SOI; low *k* dielectric layer; vertical electric field; breakdown voltage; self-heating effect **EEACC:** 2560B; 2560P **Article ID:** 0253-4177(2006)10-1832-06

<sup>\*</sup> Project supported by the National Natural Science Foundation of China(No. 60436030) and the National Key Laboratory of Analog IC(No. 9140C0903050605)

<sup>†</sup> Corresponding author. Email: xrluo@uestc. edu. cn Received 3 March 2006, revised manuscript received 26 April 2006