# A Passive Low Pass Filter on Low Loss Substrate \*

Fang Jie<sup>1</sup>, Liu Zewen<sup>1,†</sup>, Zhao Jiahao<sup>2</sup>, Chen Zhongmin<sup>1</sup>, Wei Jia<sup>1</sup>, Liu Litian<sup>1</sup>, and Li Zhijian<sup>1</sup>

(1 Institute of Microelectronics, Tsinghua University, Beijing 100084, China)

(2 Department of Material Science and Engineering, Tsinghua University, Beijing 100084, China)

**Abstract :** The loss mechanisms of different passive devices (on-chip inductors and capacitors) on different substrates are analyzed and compared. OPS (oxidized porous silicon) and HR (high-resistivity) substrates are used as low-loss substrates for on-chip planar LPF (low pass filter) fabrication. For the study of substrate loss, a planar coil inductor is also designed. Simulation results show that Q (the quality factor) of the inductor on both substrates is over 20. Measurements of the LPF on OPS substrate gives a - 3dB bandwidth of 2. 9GHz and a midband insertion loss of 0. 87dB at 500M Hz. The LPF on HR substrate gives a - 3dB bandwidth of 2. 3GHz and a midband insertion loss of 0. 42dB at 500M Hz.

Key words: L C low-pass filter; low-loss substrate; on-chip inductor; RFEEACC: 2100CLC number: TN713Document code: AArticle ID: 0253-4177(2006)09-1572-06

## 1 Introduction

To meet the needs of modern wireless communication systems, a variety of filters have been developed, such as CMOS active, lumped LC, mechanical, ceramic, surface acoustic wave (SAW), and bulk acoustic wave (BAW) filters. SAW and ceramic filters are mostly used for intermediate-frequency (IF) and radio-frequency (RF) modules, respectively<sup>[11]</sup>. However, they are all discrete components and consume a considerable area of the system chip and require a specific interface with integrated electronics. That is to say, off-chip components pose an important obstacle to the ultimate miniaturization and portability of wireless transceivers. Therefore, much effort has been focused on miniaturizing and integrating off-chip devices with IC circuits<sup>[2]</sup>.

On-chip LC filters are a candidate for solving the problem<sup>[3,4]</sup>. However, it is quite difficult to fabricate high-performance on-chip inductors and capacitors with conventional IC processes. Very high substrate loss is one of the main obstacles to realize high Q (quality factor) passive devices<sup>[5]</sup>. Therefore, low-loss substrate should be developed to achieve high-performance passive filters.

In this paper, planar-integrated LC low-pass filters (LPF) are fabricated on OPS (oxidized porous silicon)<sup>[6,7]</sup> and high-resistivity (HR) substrates<sup>[8]</sup>, respectively. The filter consists of two inductors and one MIM (metal-insulator-metal) capacitor. The loss mechanisms of passive devices (inductor/capacitor) on different substrates (low/ middle/ high resistivity substrate) are analyzed ,and two kinds of low-loss substrate (OPS/ HR substrate) are presented. To evaluate the effect of lowloss substrate ,on-chip planar inductors on OPS and HR substrates are used as device examples. Based on the analysis, we present the design and fabrication of the LPF. The measurements show that the Q of RF passive components is improved on both OPS and HR substrates and that the performance of the LPF is promising for RF front-end applications.

## 2 Substrate loss analysis and comparison

For on-chip RF passive devices, including inductors and capacitors, the main loss mechanisms related to substrate are substrate-eddy-current-induced resistance ( $R_{eddy}$ ) and coupled capacitive loss

<sup>\*</sup> Project supported by the 211 Project of the Ministry of Education of China

<sup>†</sup>Corresponding author. Email :liuzw @tsinghua.edu.cn

Received 16 March 2006, revised manuscript received 19 April 2006

$(C_{\text{couple}})$  through the insulating dielectric between the device and the underlying substrate<sup>[9]</sup>.

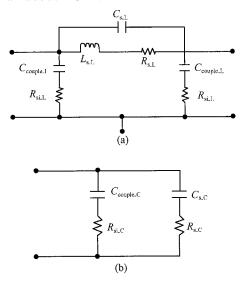

However, these two factors exert different effects on inductors and capacitors. Figures 1 (a) and (b) give the simplified equivalent lumped circuit models of on-chip inductors<sup>[10]</sup> and MIM capacitors<sup>[11]</sup>, respectively. In Fig. 1 (a),  $L_{sL}$  is the designed inductance,  $C_{\rm s L}$  models the parasitic capacitance between two metal layers due to the overlapping winding,  $R_{\rm s L}$  is the series resistance of the inductor, including the contribution of Reddy and ohm resistance,  $R_{si L}$  is the substrate resistance, and  $C_{\text{couple L}}$  represents the oxide layer capacitance.  $R_{\text{eddy}}$ is quite important to the performance of on-chip inductors because it is proportional to the square of frequency  $(f^2)$  and is the main part of  $R_{sL}$ , which is critical to the Q of the inductor at the frequencies higher than about 1 GHz.

Fig. 1 (a) Simplified two-port equivalent lumped model of on-chip inductors; (b) Simplified one-port equivalent lumped model of MIM capacitors

In Fig. 1 (b),  $C_{s\_C}$  is the designed capacitance,  $R_{s\_C}$  is the parasitic series resistance, and  $R_{s\_C}$  and  $C_{couple\_C}$  have the same meanings as  $R_{s\_L}$  and  $C_{couple\_L}$ in Fig. 1 (a), respectively.  $C_{couple\_C}$  and  $R_{s\_C}$  can be regarded as the substrate charging branch, compared with the main branch, consisting of  $R_{s\_C}$  and  $C_{s\_C}$ . The main branch has a better Q and less charging time than the substrate branch, for  $R_{s\_C}$  is always larger than  $R_{s\_C}$ . At low frequencies (below 1 GHz), both branches can be charged and discharged. Therefore, the Q of the capacitor is mainly determined by that of the substrate branch, which consumes more losses than the main branch. At high frequencies, only the main branch is involved in the charging, and the Q of the device is mainly determined by that of the main branch.

From the analysis of the loss mechanisms of on-chip inductors and MIM capacitors, it is clear that the substrate plays an important role in improving device quality. The possible methods are to partly remove the substrate with wet or dry etching ,to enhance the thickness of the isolation layer, or simply to use HR (more than 100 ·cm) substrate<sup>[12]</sup>. To remove the substrate underneath the structure can evidently improve the device performance, but additional complex and expensive processes must be used. Using a thick insulating layer (oxide layer) is also promising for effectively improving the device performance. Nevertheless, it is difficult to get enough thick oxide by common CVD deposition due to the low deposition rate. In contrast, substrate modification with OPS can easily obtain a very thick oxide layer on the order of ten micrometers<sup>[7]</sup>, which decreases the couple capacitance C<sub>couple</sub>. Using HRS (high resistivity substrate)<sup>[8]</sup>, we can easily obtain good device performance by reducing the substrate-eddy-currentinduced resistance and increasing the RC charging time of the substrate branch of the capacitor ,which make the influence of substrate branch negligible. Therefore, both substrates used in our study have their own merits.

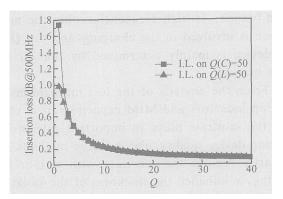

The Q of inductors and capacitors are directly related to the performance of the LPF. Figure 2 shows simulated curves of the LPF IL (insertion loss) at 500M Hz as it varies with the Q of the inductor and capacitor. Q(C) = 50 indicates that Q of the capacitor is fixed at 50 and Q of the inductor is varied from 1 to 40. Q(L) = 50 indicates that Q of the inductor is fixed at 50 and Q of the capacitor is varied from 1 to 40. From the two curves, it can be seen that the inductor and capacitor have almost the same effect on the IL of LPF. However, Q of MIM capacitors is always higher than that of onchip inductors. Therefore, the performance of the inductors is usually the main concern in LC filter design.

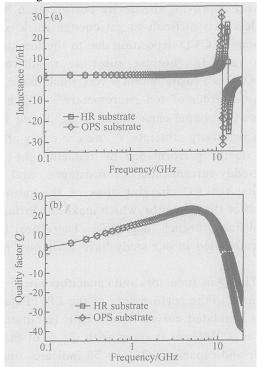

To verify the effects of OPS and HR substrate, the same planar spiral inductor is designed and simulated on both of the substrates. Figure 3

Fig. 2 IL of LPF changes with the quality factor Q of passive devices

shows the 2.5D simulated results of the device. The structure and substrate parameters of the inductor are given in Table 1.

Fig. 3 Simulated (2.5D) results of the planar inductor (a) Inductance of the inductor; (b) Q of the inductor

| Table 1 | Structure and | substrate parameters of inductor |

|---------|---------------|----------------------------------|

|         |               |                                  |

| Туре                 | Parameters                          | Value |  |

|----------------------|-------------------------------------|-------|--|

|                      | Strip width/µm                      | 36    |  |

| Structure parameters | Turn-to-turn spacing/µm             | 12    |  |

|                      | Strip thickness/µm                  | 4     |  |

|                      | Insulating layer thickness/µm       | 1.5   |  |

|                      | Coil turns                          | 2.5   |  |

|                      | OPS thickness/µm                    | 30    |  |

| Substrate parameters | OPS substrate resistivity/ ( · cm)  | 0.01  |  |

|                      | HR substrate resistivity/ ( · cm)   | 900   |  |

|                      | HR substrate resistivity/ ( · · cm) | 90    |  |

The measured L and Q of the inductor on HR substrate are 1. 8nH at 2. 4GHz and 20. 0 at 2. 4GHz, respectively. These results are similar with the simulated data (L of 2. 0nH at 2. 4GHz and Q of 18. 6 at 2. 4GHz), and show that the quality of passive devices is promising on these two kinds of low-loss substrates.

## **3** Filter design and fabrication

#### 3.1 Design

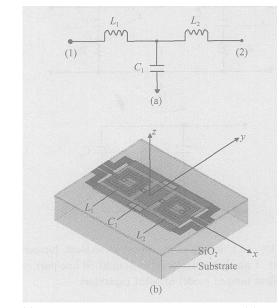

The design of the LPF is based on a basic minimum capacitor Butterworth prototype structure, which consists of two series inductors and one shunt capacitor, as shown in Fig.  $4^{[13]}$ . Figure 4 (a) is the filter circuit and Figure 4 (b) gives a 3D schematic view of the LPF. The design parameters are shown in Table 2.

Fig. 4 (a) LC low-pass filter prototype structure; (b) Schematic view of LPF (also for 3D simulation)

| Table 2 | Decian | parameters | of  | I DE |

|---------|--------|------------|-----|------|

| Table 2 | Design | parameters | OI. | LPF  |

| Tuble 2 Design parameters of ETT |                         |       |

|----------------------------------|-------------------------|-------|

|                                  | Parameters              | Value |

|                                  | 3dB bandwidth/ GHz      | 2.4   |

| Circuit design                   | IL (dB @1 GHz)          | < 2   |

|                                  | Input resistance/       | 50    |

|                                  | Output resistance/      | 50    |

|                                  | L/ nH                   | 4.2   |

|                                  | Coil turns              | 3     |

| L design                         | Strip width/µm          | 36    |

|                                  | Turn-to-turn spacing/µm | 12    |

|                                  | Strip thickness/µm      | 4     |

|          | Parameters                    | Value |

|----------|-------------------------------|-------|

| C design | C/ p F                        | 1.8   |

|          | Top-plate thickness/µm        | 4     |

|          | Bottom-plate thickness/µm     | 1     |

|          | Insulating layer thickness/µm | 1.5   |

|          | Width/µm                      | 240   |

|          | Length/µm                     | 420   |

#### 3.2 Fabrication

The fabrication process of the LPF on OPS substrate is given as follows. On the 400 $\mu$ m silicon substrate ,a 30 $\mu$ m OPS layer is selectively formed. To protect the OPS layer ,SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> layers are deposited with LPCVD. Ti (50nm) and Cu (200nm) are then sputtered as a stick layer and a seed layer. After that ,Cu with the thickness of 1 $\mu$ m is electroplated and patterned to form the underpass of the inductors and the bottom plate of the MIM capacitor. Polyimide is spun on as a dielectric layer. After the polyimide etching ,another layer of Ti (50nm) and Cu (200nm) is sputtered. Finally ,Cu with a thickness of 4 $\mu$ m is electroplated and patterned to serve as the spiral coil of the inductor and the top plate of the MIM capacitor.

The fabrication processes of the LPF on OPS and HR substrate are similar except for the preparation of the substrate. For HR substrate,  $SiO_2$  and  $Si_3 N_4$  layers are directly deposited on the substrate without modifying the substrate.

### 4 **Results and discussion**

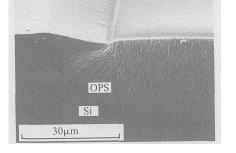

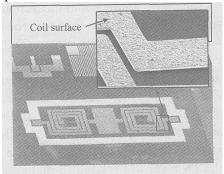

The filter was realized in a standard  $1\mu m$  1-poly ,2-metal ,CMOS process. Figure 5 shows the profile of the modified substrate with OPS. The surface of the OPS is smooth enough for further processes of RF devices with an average coarseness of less than 2nm. Figure 6 is a SEM photograph of the LPF die. The entire area of the filter is 1350 $\mu m$ ×550 $\mu m$ , which can be further reduced by applying

Fig. 5 Profile of modified substrate with OPS

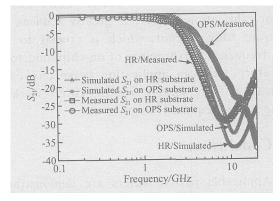

a minimum inductor rather than a minimum capacitor prototype<sup>[13]</sup>. Figure 7 shows the simulated and measured results of the designed LPF. The data are also compared in Table 3.

Fig. 6 SEM photograph of the LPF die

Fig. 7 Simulated and measured results of the designed LPF

|                                         | OPS Results |      | HR Results |      |

|-----------------------------------------|-------------|------|------------|------|

| Parameters                              | Simu        | Meas | Simu       | Meas |

| 3dB BW/ GHz                             | 2.6         | 2.9  | 3.0        | 2.3  |

| IL/ dB @0.5GHz                          | 0.21        | 0.87 | 0.22       | 0.42 |

| IL/ dB @1 GHz                           | 0.49        | 1.18 | 0.32       | 0.61 |

| 30dB BW/ GHz                            | 9.2         | 17.0 | 7.8        | 8.0  |

| Self-resonance frequency $f_{SR}$ / GHz | 12.6        | > 20 | 11.0       | 11.4 |

Table 3 Simulated and measured data comparison

Measurements of the LPF on OPS substrate give a - 3dB bandwidth (BW) of 2.9 GHz and a midband insertion loss of 0.87dB at 500M Hz, and the LPF on HR substrate gives a - 3dB bandwidth of 2.3 GHz and a midband insertion loss of 0.42dB at 500M Hz. The simulated  $S_{21}$  curves are also presented in Fig. 7. The insertion loss of the LPF on OPS and HRS is better than that in Refs. [3] (on 14 ·cm p-type Si substrate, IL > 2dB at the passband) and [14] (on HRS, IL > 6dB at the passband). The results are also comparable to Ref. [15] (in MCM-Si Process, IL < 1dB at the pass-band). The simulated and measured data show that both OPS and HR substrates are promising for RF passive devices, such as inductors, capacitors, and LC filters.

From the above analysis and measurements, it can be seen that OPS is a better choice for capacitors than HRS (high resistivity substrate), because it reduces C<sub>couple</sub>, which is critical to the coupled capacitive loss of the capacitors. Nevertheless, from the discrepancy between the simulated and measured results, it is also clear that the surface quality of an OPS layer is hard to control because the growth of PS (porous silicon) and the oxidation of the PS layer are related to many environmental parameters<sup>[7,16,17]</sup>, including current, area, and temperature. HRS is a better choice for inductor fabrication because it greatly reduces the substrate eddy current ,which is crucial to the high-frequency performance of on-chip inductors. Therefore, from an application perspective, HR substrate is more suitable for LC filters working in the radio-frequency range.

### 5 Conclusion

Applicable passive filters are demonstrated and fabricated. Both HR and modified substrates with oxidized porous silicon (OPS) technology can reduce the insertion loss of passive RF devices, making LC filters suitable for high frequency applications. HR substrate is more suitable for LC filters in RF applications.

Acknowledgment The authors would like to thank IMECAS for microwave measurement and EM Laboratory for SEM.

#### References

Aigner R, Ella J, Timme H J, et al. Advancement of MEMS into RF-filter applications. International Electron Devices Meeting ,San Francisco ,2002:897

- [2] Nguyen C T C, Katehi L P B, Rebeiz G M. Micromachined devices for wireless communication. Proceeding of the IEEE, 1998,86(8):1756

- [3] Nguyen N M, Meyer R G. Si IC-compatible inductors and LC passive filters. IEEE J Solid-State Circuits, 1990, 25 (4):1028

- [4] Kuhn W B, Yanduru N K, Wyszynski A S. Q-enhanced LC bandpass filters for integrated wireless applications. IEEE Trans Microw Theory Tech, 1998, 46(12):2577

- [5] Lopez-Villegas J M, Samitier J, Cane C, et al. Improvement of the quality factor of RF integrated inductors by layout optimization. IEEE Trans Microw Theory Tech ,2000 ,48(1) :76

- [6] Lin TL, Wang KL. New silicon on insulator technology using a two step oxidation technique. Appl Phys Lett, 1986, 49 (17):1104

- [7] Peterson R L ,Drayton R F. Dielectric properties of oxidized porous silicon in a low resistivity substrate. IEEE MTT-S Int Microwave Symp Dig ,2001:767

- [8] Spirito M, De Paola F M, Nanver L K, et al. Surface-passivated high-resistivity silicon as a true microwave substrate. IEEE Trans Microw Theory Tech, 2005, 53 (7):2340

- [9] Soorapanth T. CMOS RF filtering at GHz frequency. PhD Dissertation ,Stanford University ,CA ,USA ,2002:27

- [10] Yue C P, Wong S S. Physical modeling of spiral inductors on silicon. IEEE Trans Electron Devices ,2000 ,47 (3) :560

- [11] Xiong X Z, Fusco V F. A comparison study of EM and physical equivalent circuit modeling for MIM CMOS capacitors. Microwave and Optical Technology Letters ,2002 ,34(3) :177

- [12] Kamogawa K, Nishikawa K, Toyoda I, et al. A novel high-Q and wide-frequency-range inductor using Si 3-D MMIC technology. IEEE Microw Guided Wave Lett, 1999, 9(1):16

- [13] Rhea R W. HF filter design and computer simulation. Atlanta: Mc Graw- Hill, 1995

- [14] Liu Y, Wang Y, Shir YL, et al. Optimization of on-chip inductor and its application in low-pass filter. Proceedings 7th International Conference on Solid-State and Integrated Circuits Technology ,2004:221

- [15] Hartung J. Integrated passive components in MCM-Si technology and their applications in RF-systems. International Conference on Multichip Modules and High Density Packaging,1998:256

- [16] Molinero D, Valera E, Lazaro A, et al. Properties of oxidized porous silicon as insulator material for RF applications. A Spanish Conference on Electron Devices ,2005:131

- [17] Chen Z M. Research of high Q RF-MEMS planar inductor. MS Thesis, Institute of Microelectronics, Tsinghua University, Beijing, 2004 (in Chinese) [陈忠民. 高 Q 值 RF-MEMS 平 面电感研究.清华大学微电子所硕士学位论文,北京,2004]

## 低损耗衬底上实现无源低通滤波器\*

方杰'刘泽文<sup>1,†</sup>赵嘉昊'陈忠民'韦嘉'刘理天'李志坚'

(1 清华大学微电子研究所,北京 100084) (2 清华大学材料科学与工程系,北京 100084)

摘要:分析比较了不同种类衬底上无源器件(片上电感和电容)的损耗机理,在OPS(氧化多孔硅)和HR(高阻硅)低损耗衬底上分别实现了片上低通滤波器.为了研究衬底损耗,设计了平面螺旋电感,其 Q值在两种衬底上的仿真结果都超过了20.在OPS衬底上的低通滤波器实测-3dB带宽为2.9GHz,通带插入损耗在500MHz为0.87dB;在HR衬底上的低通滤波器实测-3dB带宽为2.3GHz,通带插入损耗在500MHz为0.42dB.

关键词:LC低通滤波器;低损耗衬底;片上电感;RF EEACC:2100 中图分类号:TN713 文献标识码:A 文章编号:0253-4177(2006)09-1572-06

†通信作者. Email :liuzw @tsinghua.edu.cn

<sup>\*</sup>教育部 211 工程资助项目