# Mo/4H-SiC 肖特基势垒二极管的研制\*

张发生1,2,\* 李欣然1

(1 湖南大学电气与信息工程学院,长沙 410082) (2 中南林业科技大学电子与信息工程学院,长沙 410004)

摘要:采用微电子平面工艺,射频溅射 Mo 作肖特基接触,电子束热蒸发金属 Ni 作欧姆接触,三级场限环终端表面保护.并通过对 Mo 接触进行合理的高温退火,不降低理想因子和反向耐压特性情况下,有效控制肖特基势垒高度在  $1.2\sim1.3$ eV 范围内,成功研制出高耐压低损耗 Mo/4H-SiC 肖特基势垒二极管.其特性测试结果为:击穿电压  $V_b$  为 3000V, 串联导通电阻  $R_{on}$  为 9.2m $\Omega \cdot \text{cm}^2$ ,  $V_b^2/R_{on}$  为 978MW/cm $^2$ .

关键词: SiC; Mo; 肖特基二极管

**EEACC:** 2520M

中图分类号: TM31 文献标识码: A 文章编号: 0253-4177(2007)03-0435-04

### 1 引言

SiC 以其杰出的物理和电学特性——宽禁带、高热导率、大的饱和漂移速度和高临界击穿电场等,成为制作高功率、高频、耐高温、抗辐射器件的理想半导体材料,在航天、航空、石油勘探、核能和通信等领域有广泛的应用前景.目前 SiC 半导体材料生长和外延技术的研究取得了突破性进展,基本解决了器件制作中的材料问题.对 SiC 的研究重点已转移到器件制作的基本工艺技术上,如掺杂、氧化、刻蚀、金属半导体接触和封装等,以发挥 SiC 半导体材料的潜在优势,制作出高性能器件和电路<sup>[1]</sup>. SiC 器件已成为目前半导体研究的热点和前沿领域之一.

目前额定耐压(0.3~1.2kV)和额定正向导通电流(1~20A)的 4H-SiC 肖特基势垒二极管(SBD)已经商品化[ $^{22}$ ].由于 4H-SiC 具有优良的材料特性,即便反向耐压高达 3~5kV 等级的 4H-SiC SBD 从理论上讲仍然可以达到串联导通电阻  $R_{on}$  低于  $10m\Omega \cdot cm^{2[3]}$ .

肖特基势垒高度  $\Phi$ 。对减小功率损耗具有十分重要的作用.如在 50% 占空比情况下,SBD 损耗密度可用  $\frac{1}{2}(V_{\rm f}J_{\rm f}+V_{\rm r}J_{\rm r})$ 表示[3],其中  $V_{\rm r},V_{\rm f},J_{\rm r}$ 和  $J_{\rm f}$ 分别表示反向耐压、正向导通压降、反向漏电流密度和正向导通电流密度. 当肖特基势垒二极管的额定  $V_{\rm r}$ 和  $J_{\rm f}$ 一定时,要使 SBD 功率损耗低就必须严格控制  $V_{\rm f}$ 和  $J_{\rm r}$ ,而  $V_{\rm f}$ 和  $J_{\rm r}$  恰好是由  $\Phi$ b. 决定.

为此在  $25\sim200$   $\mathbb{C}$  温度范围内为了获得高耐压( $3\sim5$  kV)最小功率损耗,肖特基势垒高度  $\Phi$ 。应控制在  $1.18\sim1.31$  eV 之间<sup>[4]</sup>.

目前国内外研制生产的肖特基势垒二极管都是采用金属 Ti, Ni 等与 n 型 4H-SiC 形成肖特基接触,此时肖特基势垒高度  $\Phi_b$  分别为 0.95 和 1.65eV<sup>[5]</sup>.按照  $\Phi_b$  决定最小功率损耗原理,要想研制生产出高耐压低损耗的 4H-SiC SBDS 产品,沿用目前已使用的金属和 SiC 形成肖特基接触,其  $\Phi_b$  很难控制在  $1.2\sim1.3$ eV 范围内.为此当前迫切需要寻找一种新的金属材料和 4H-SiC 形成良好肖特基接触,保证其  $\Phi_b$  控制在  $1.2\sim1.3$ eV 范围内,实现高耐压低损耗的目的.

本文针对上述存在的问题和不足,提出用金属 Mo 与 n 型 4H-SiC 形成良好的肖特基接触.通过对 Mo 接触进行合理的高温退火,在不降低理想因子和反向耐压特性的情况下,有效控制肖特基势垒高度在  $1.2\sim1.3$ eV 范围内,成功研制出高耐压低损耗 Mo/4H-SiC 肖特基势垒二极管.实验测量该器件击穿电压  $V_b$  为 3000V,串联导通电阻  $R_{on}$  为 9.2m $\Omega \cdot cm^2$ ,  $V_b^2/R_{on}$  为 978MW/cm<sup>2</sup>.

## 2 肖特基接触制作工艺

实验中使用的材料是从美国 CREE 公司购买的  $n^+$  n 型总厚度为  $350\mu$ m 的 4H-SiC 半导体材料,其中  $n^+$  衬底层电阻率为  $0.010\Omega$  • cm,n 型外延层厚度为  $10\mu$ m,掺杂浓度为  $1.0\times10^{16}$  cm<sup>-3</sup>.

<sup>\*</sup> 高校青年教师科研基金资助项目

<sup>†</sup>通信作者.Email:zhangfs65@126.com 2006-10-12 收到,2006-11-18 定稿

依据现有的条件,结合 Mo 肖特基接触结构特点,本文采用的平面试制工艺主要包括如下几道主要程序:(1)清洗 4H-SiC 材料样片;(2)有源区掺氯氧化(SiO<sub>2</sub> 厚度为 400nm);(3)去掉样片衬底面(背面)氧化层;(4)在高真空(5×10<sup>-5</sup> Pa)炉中,将衬底加热电子束热蒸发 1.  $2\mu$ m 的 Ni 金属,再在高真空高温(920°C)下退火,形成良好欧姆接触;(5)光刻有源区掺氯氧化层,射频溅射 110nm 厚的金属 Mo;(6)金属 Mo 层在氮气中进行 10min 不同温度退火实验.实验结果如图 1 和 2 所示.

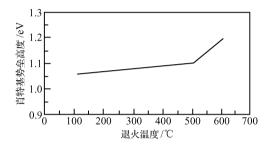

图 1 退火温度与 ゆ 之间的关系

Fig. 1 Annealing temperature dependence of  $\Phi_b$

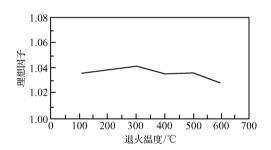

图 2 退火温度与理想因子 n 之间的关系

Fig. 2 Annealing temperature dependence of n factor

图 1 是退火温度与肖特基势垒高度  $\Phi$ 。之间的关系;图 2 是退火温度与理想因子 n 之间的关系.肖特基势垒高度  $\Phi$ 。和理想因子 n 可通过室温正向 I-V 特性曲线得到,具体原理见如下公式.

因 ln *I-V* 曲线呈线性关系,说明二极管特性遵循理想二极管方程:

$$J_f = J_s \left[ \exp(qV_f/nkT) - 1 \right]$$

(1) 式中  $k$  为玻尔兹曼常数;  $T$  为绝对温度;  $q$  为电子电荷;  $n$  为理想因子. 对理想接触  $n=1$ , 理想因子  $n$  值反映肖特基结的正向  $I_f$ - $V_f$  特性. 当正偏电压大于  $3kT/q$  时, 若忽略串联电阻上的压降,  $n$  值为:

$$n = \frac{qV_{\rm f}}{kT\ln(J_{\rm f}/J_{\rm s})} \tag{2}$$

式中  $J_s$  为  $\ln J_f$ - $V_f$  曲线在线性区外推到  $V_f$  = 0 所得到的饱和电流密度;  $V_f$  为外加电压,此时等于

肖特基势垒二极管结压降.

(1)式中 *J*。为肖特基势垒二极管的反向电流密度,它与肖特基势垒高度有关,为

$$J_{\rm s} = A^* T^2 \exp(-q\phi_{\rm bs}/nkT) \tag{3}$$

$$\phi_{\rm bs} = (nkT/q)\ln(A^* T^2/J_s) \tag{4}$$

式中  $A^*$  为有效理查逊常数,其值为120A·cm $^{-2}$ ·K $^2$ ;  $\phi_{bs}$  为金半接触势垒高度.将已求得的 n 和  $J_s$  代入 (4) 式就可以求得  $\phi_{bs}$ .

从图 1 中的曲线可知,在室温下,Mo 肖特基势垒高度  $\Phi_b$  约为 1. 12eV,随着退火温度上升, $\Phi_b$  略有增大. 当退火温度上升到 600°C 后, $\Phi_b$  增大到约为 1. 23eV. 通过退火,之所以会出现  $\Phi_b$  略有增大现象,是因为在 Mo-4H-SiC 之间存在明显的大约 3nm厚 Mo<sub>2</sub> C/Mo<sub>5</sub> Si<sub>3</sub>/SiC 界面复合层,此复合层是影响  $\Phi_b$  略有增大的主要原因<sup>[6]</sup>. 之所以会出现此界面复合层是由于在退火过程中,SiC 材料中的碳元素比硅元素迁移得快,结果在 SiC 表面堆积了很多碳元素,同时向金属钼薄层扩散形成 Mo<sub>2</sub> C; 另外,由于SiC 材料表面薄层中的碳元素减少,金属钼元素向SiC 材料里面扩散从而形成 Mo<sub>5</sub> Si<sub>3</sub>. 图 3 为 Mo<sub>5</sub> Si<sub>3</sub>/4H-SiC 界面电子衍射图,其中 Mo<sub>5</sub> Si<sub>3</sub> 结晶粒度大约 90nm.

图 3  $Mo_5Si_3/4H$ -SiC 界面电子衍射图 Fig. 3 TEM micrograph of  $Mo_5Si_3/4H$ -SiC interface

region

从图 2 可知,通过高温退火,其理想因子 n 比较稳定,基本上控制在  $1.00\sim1.05$  之间,且经过高温退火,Mo-4H-SiC 之间接触对反向耐压漏电流没有负面影响<sup>[4]</sup>.为此,为了能达到既耐高压,导通损耗又低的目的,下面所述的研制的 Mo-4H-SiC SBDS 退火温度就定在 600  $\mathbb{C}$  .

## 3 Mo/4H-SiC SBD 的制作

实验中使用的材料是从美国 CREE 公司购买

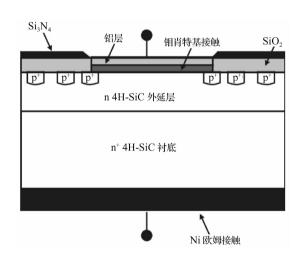

的  $n^+ n$  型总厚度为  $380\mu m$  的 4H-SiC 半导体材料, 其中 n<sup>+</sup> 衬底层电阻率为 0.010Ω · cm, n 型外延层 厚度为  $30\mu m$ ,掺杂浓度为  $2.0 \times 10^{15} cm^{-3}$ . 因器件 要承受较高耐压,所以器件的耐压还要受结弯曲及 表面电荷的影响而严重下降,因而为了提高器件承 受耐压能力,必须采用终端技术,在各种平面终端技 术中,场限保护环工艺制作简单,并能有效克服结弯 曲对器件的耐压能力,场限保护环在器件承受反压 时起分压作用,一个多环系统即可被简单地视为多 级分压器[7]. 为此采用三级 p<sup>+</sup> 场限保护环和 SiO<sub>2</sub>-Si<sub>3</sub>N<sub>4</sub>复合绝缘环隔离减小高压电场集边效应等技 术,形成 Mo/4H-SiC 肖特基势垒二极管,其结构剖 面图如图 4 所示,其中环宽为 10 μm,环间距由内往 外分别是 5 和 8μm. 之所以选此场限尺寸,是据 Zhang 等人[8]提出采用3级场限终端保护,成功试 制出耐压 2.8kV 的 GaN SBD, 而 SiC 和 GaN 的主 要结构参数又很相近,如两种材料禁带宽度  $(E_{g,4H-SiC} = 3.26eV, E_{g,GaN} = 3.45eV)$ 及击穿电场  $(V_{4\text{H-SiC}} = 2 \times 10^6 \,\text{V/cm}, V_{\text{GaN}} = 3.3 \times 10^6 \,\text{V/cm})$ 都 很相近.

图 4 Mo/4H-SiC 肖特基势垒二极管结构示意图 Fig. 4 Schematic of the Mo/4H-SiC SBDS

依据现有的条件,结合 Mo-4H-SiC SBDS 结构特点,本文采用的平面试制工艺主要包括如下几道主要程序:(1)清洗 4H-SiC 材料;(2)有源区掺氯氧化(二氧化硅厚度 400nm);(3)去除样片衬底面(背面)氧化层;(4)在高真空(5×10<sup>-5</sup> Pa)炉中,将衬底加热电子束热蒸发  $1.2\mu m$  厚的金属 Ni,再在高真空高温(920℃)下退火形成良好欧姆接触;(5)光刻有源区掺氯氧化层,离子注入三价金属硼形成 p型掺杂区,并在 850℃氮气保护下,退火 30min;(6)有源区掺氯氧化(二氧化硅厚度 55nm)及用硅烷LPCVD 生长 Si<sub>3</sub> N<sub>4</sub> (厚度 125nm);(7)光刻有源区,

有源区射频溅射淀积 110nm 厚的金属 Mo 层,并在炉温为 600 C, 氮气保护下退火 10min;最后在金属 Mo 上面蒸发一层  $1.2\mu$ m 的 Al 并退火.

### 4 实验结果

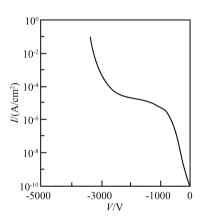

在室温下,通过对试制的样品进行测试,其Mo/4H-SiC SBD 正反向 I-V 特性分别如图 5 和 6 所示.其肖特基势垒高度  $\Phi_b$  和理想因子 n 通过计算分别为 1.25 和 1.02eV. 串联导通电阻  $R_{\rm on}$  为 9.2m $\Omega$ •cm²接近理论值. 在正向导通电流密度  $100 {\rm A/cm}^2$ 下,测得  $V_{\rm f}=1.94 {\rm V.}$  反向雪崩击穿电压  $V_{\rm b}$  为  $3000 {\rm V.}$  在  $2800 {\rm V}$  时,该器件的漏电流密度 0.12m ${\rm A/cm}^2$ ,此漏电流密度仅是已报道的  $5 {\rm kV}$  Ni-4H-SiC SBD 漏电流密度的 1% 以下[9]. 此外,Mo/4H-SiC SBD 的  $V_{\rm b}^2/R_{\rm on}$  为  $978 {\rm MW/cm}^2$ ,接近于已报道的  $10.8 {\rm kV}$  4H-SiC SBD 的最好值  $1196 {\rm MW/cm}^2$

图 5 Mo/4H-SiC 肖特基二极管反向 *I-V* 特性曲线 Fig. 5 Reverse *I-V* characteristic of Mo/4H-SiC SBD

图 6 Mo/4H-SiC 肖特基二极管正向 *I-V* 特性曲线 Fig. 6 Forward *I-V* characteristic of Mo/4H-SiC SBD

## 5 结论

通过对 Mo 接触进行合理的高温退火,实现了不降低理想因子和反向耐压特性情况下,有效控制肖特基势垒高度在  $1.2 \sim 1.3 \,\mathrm{eV}$  范围内,非常适合研制开发  $3 \sim 5 \,\mathrm{kV}$  高压等级低功率损耗的 Mo/4H-SiC SBD,且有利于减小漏电流.另外,采用 3 级场限 FLR 技术,有效地提高了器件的终端耐压水平,成功研制出高耐压低功率损耗 Mo/4H-SiC 肖特基势垒二极管,其特性测试结果是: $V_b$  为  $3000\,\mathrm{V}$ , 串联导通电阻  $R_{\mathrm{on}}$  为  $9.2\,\mathrm{m}\Omega$  •  $\mathrm{cm}^2$ ,  $V_b^2/R_{\mathrm{on}}$  为  $978\,\mathrm{MW/cm}^2$ . 当然,实测到的反向击穿电压值和理论值之间还有一些差距,漏电流也偏大,材料可能有微管道缺陷及不均性,另外版图、终端保护和工艺等还有待进一步优化完善.

#### 参考文献

[1] Zhang Yuming, Zhang Yimen, Luo Jinsheng. Pt Schottky barrier diodes on n-type 6H-silicon carbide. Chinese Journal of Semiconductors, 1999, 20(11): 1040(in Chinese)[张玉明,张义门,罗晋生. SiC 肖特基势垒二极管研制. 半导体学

报,1999,20(11):1040]

- [2] Millan J, Godignon P, Tournier D. Recent developments in SiC power devices and related technology. Proc Int Con Microelectron, 2004, 1, 23

- [3] Bhatnagar M, Baliga B J. Comparison of 6H-SiC, 3C-SiC, and Si for power devices. IEEE Trans Electron Devices, 1993, 40 (3):645

- [4] Nakamura T, Miyanagi T, Kamata I. A 4.15kV 9.07-mΩ·cm² 4H-SiC Schottky-barrier diode using Mo contact. IEEE Electron Device Lett, 2005, 26(2),99

- [5] Itoh A, Matsunami H. Analysis of Schottky-barrier heights of metal/SiC contacts and its possible application to high-voltage rectifying devices. Phys Status Solidi A, 1997, 162:

- [6] Hara S, Suzuki K, Furuya A, et al. Solid state rection of Mo on cubic and hexagonal SiC. Jpn J Appl Phys, 1990, 29; L394

- [7] Goud C B, Bhat K N. Breakdown voltage of field plate and field-limiting ring techniques; numerical comparison. IEEE Trans Electron Devices, 1992, 39(7):1768

- [8] Zhang A P, Dang G T, Cao X A, et al. Processing and device performance of GaN power rectifier. Internet Journal of Nitride of Semiconductor Research, 2000, 5S1; W11.67

- [9] Singh R, Cooper J A Jr, Melloch M R, et al. SiC power Schottky and PiN diodes. IEEE Trans Electron Devices, 2002,49(4):665

- [10] Zhao J H, Alexandrov P, Li X. Demonstration of the first 10kV 4H-SiC Schottky-barrier diodes. IEEE Electron Device Lett, 2003, 24(6):402

## Mo /Schottky Barrier Diodes on 4H-Silicon Carbide\*

Zhang Fasheng<sup>1,2,†</sup> and Li Xinran<sup>1</sup>

(1 College of Electrical and Information Engineering, Hunan University, Changsha 410082, China)

(2 School of Electronic Information Engineering, Central South University of Forestry and Technology, Changsha 410004, China)

**Abstract:** With microelectronics plane technology, RF sputtering was used to deposit Mo to form a Schottky contact and electron beam evaporation was used to deposit Ni to form an ohmic contact in high vacuum ambient, and Mo/4H-SiC Schottky-barrier diodes were made in structures containing three-FLR. High-temperature annealing for the Mo contact is found to be effective in controlling the Schottky-barrier height at  $1.2 \sim 1.3 \, \text{eV}$  without degradation of the n-factor and reverse characteristics. A breakdown voltage of  $3 \, \text{kV}$ , a specific on resistance of  $9.2 \, \text{m}\Omega \cdot \text{cm}^2$ , and a good  $V_b^2/R_{on}$  value of  $978 \, \text{MW/cm}^2$  for Mo/4H-SiC Schottky-barrier diodes are obtained experimentally.

Key words: SiC; Mo; Schottky barrier diode

**PACC:** 7340N **EEACC:** 2520M **Article ID:** 0253-4177(2007)03-0435-04

<sup>\*</sup> Project supported by the Science Research Foundation for Young Teachers of the Institute of Higher Education of China

<sup>†</sup> Corresponding author. Email: zhangfs65@126.com