### Total Dose Radiation Hardened PDSOI CMOS 64k SRAMs

Guo Tianlei<sup>†</sup>, Zhao Fazhan, Liu Gang, Li Duoli, Li Jing, Zhao Lixin, Zhou Xiaoyin, Hai Chaohe, and Han Zhengsheng

(Institute of Microelectronics, Chinese Academy of Sciences, Beijing 100029, China)

Abstract: The first domestic  $1 \times 10^6 \, \text{rad}(\text{Si})$  total dose hardened 1.  $2\mu \text{m}$  partially depleted silicon-on-insulator (PD-SOI) 64k SRAM fabricated in SIMOX is demonstrated. The address access time is independent of temperature from -55 to  $125^{\circ}\text{C}$  and independent of radiation up to  $1 \times 10^6 \, \text{rad}(\text{Si})$  for the supply voltage  $V_{\text{DD}}$ . The standby current is  $0.65\mu \text{A}$  before the total dose of radiation and is only 0.  $80\,\text{mA}$  after radiation exposure, which is much better than the specified  $10\,\text{mA}$ . The operating power supply current is  $33.0\,\text{mA}$  before and only  $38.1\,\text{mA}$  afterward, which is much better than the specified  $100\,\text{mA}$ .

Key words: PDSOI; SRAM; total dose; radiation

EEACC: 1265; 1265D

**CLC number:** TN47 **Document code:** A **Article ID:** 0253-4177(2007)08-1184-03

#### 1 Introduction

Previous investigations have been reported on radiation hardened 1. 2 m partially depleted silicon-on-insulator (PDSOI) H-gate nMOSFETs[1,2] and 4k SRAM fabricated in SIMOX material [3,4]. This work reports the first domestically produced radiation hardened 1. 2 µm PDSOI 64k SRAM fabricated in SIMOX material. The SOI radiation hardening process was developed by the use of partially depleted front and back channel 1.2 µm transistors with body-ties and demonstrated by the fabrication of a radiation hardened 64kb SRAM. Four key elements were specially treated to achieve the hardening: the gate oxide, the gate edge, the field oxide, and the buried oxide [5]. In this work, induced standby currents of 1. 2 µm PD-SOI 64k SRAMs as a function of total dose from  $1 \times 10^5$  to  $1 \times 10^6$  rad(Si) are reported. The operating power supply current of the SRAM as a function of total dose from  $1 \times 10^5$  to  $1 \times 10^6$  rad (Si) is also reported.

## 2 Experiment

The SIMOX wafers used in this study were standard O<sup>+</sup> implanted wafers acquired from SIMGUI. The post oxygen implant anneal resulted

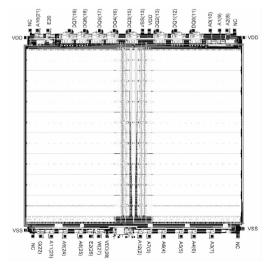

in approximately 375nm of buried oxide and approximately 190nm of top silicon. The HF decorated defect density is less than 0.  $5 \text{cm}^{-2[6]}$ . The processing steps for 1.  $2 \mu \text{m}$  PDSOI 64k SRAM essentially include LOCOS isolation, twin well definition, gate oxidation, LDD,  $n^+/p^+$  source and drain implant, contact, first metal, via, second metal. Note that the gate oxide is 18nm, and the source/drain and the polysilicon gate are titanium silicide. Figure 1 shows the layout of the 1.  $2 \mu \text{m}$  PDSOI 64k SRAM. The chip size for the SRAM is 9.  $26 \text{mm} \times 7$ . 68 mm and a cell size of the SRAM is  $27 \mu \text{m} \times 23$ .  $6 \mu \text{m}$ .

Fig. 1 Layout of 1. 2μm PDSOI 64k SRAM

<sup>†</sup> Corresponding author. Email: guotianlei@sina.com Received 8 February 2007, revised manuscript received 21 March 2007

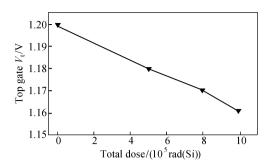

Fig. 2 Top gate  $V_t$  as a function of total dose

The Co-60 irradiation facility at the Northwest Institute of Nuclear Technology was used for total dose radiation testing, providing a dose rate of 50 rad(Si)/s as measured from the Unidos dose tester. The ambient temperature and humidity of the testing environment were 27. 5°C and 45%, respectively. The experiments were done at  $V_{\text{DD}} = 5\text{V}$  and were tested in real time. The SRAM and ROM radiation effect testing system developed by the Northwest Institute of Nuclear Technology could provide the real time DC and AC electrical parameters of the SRAM.

#### 3 Results and discussion

First, we assessed the total dose hardness of the gate oxide and the buried oxide by measuring the respective threshold voltage shifts of the individual transistor using a Co-60 irradiation source. Very small radiation induced threshold voltage shifts ( $<50 \,\mathrm{mV}$ ) at  $1 \times 10^6 \,\mathrm{rad}(\mathrm{Si})$  were observed for 10/1. 2 top gate nMOSFETs under turn-on irradiation bias ( $V_{\mathrm{G}} = 0$ ,  $V_{\mathrm{D}} = V_{\mathrm{DD}}$ ,  $V_{\mathrm{S}} = 0$ ,  $V_{\mathrm{body}} = 0$ ) as shown in Fig. 2. The gate oxide was thus hardened to  $1 \times 10^6 \,\mathrm{rad}(\mathrm{Si})$ .

Since back gate pMOSFETs do not show unfavorable radiation induced threshold voltage shifts (negative shift only for pMOSFETs), we report here only the results of the back gate nMOS-

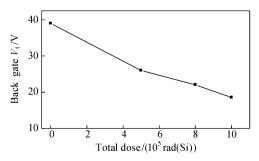

Fig. 3 Back gate  $V_t$  as a function of total dose

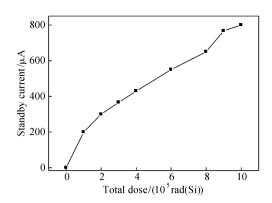

Fig. 4 Pre-radiation and post-radiation standby current as a function of total dose

FETs under the turn-on irradiation bias condition. The total dose hardness of the buried oxide is assessed by the back gate threshold voltage as a function of total dose shown in Fig. 3. The back gate threshold voltage at  $1 \times 10^6 \, \text{rad}(\text{Si})$  is about  $1 \times 10^6 \, \text{rad}(\text{Si})$ .

Second, we assessed the total dose hardness of the gate edge and the field oxide by measuring standby current in packaged 64k SRAMs. The results of the pre-radiation and post radiation standby currents of 64k SRAM are shown in Fig. 4.

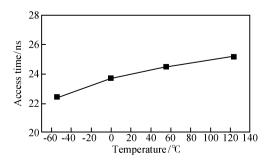

The access time as a function of temperature from -55 to  $125^{\circ}$ C is shown in Fig. 5 for a 1.  $2\mu$ m PDSOI 64k SRAM. The address access time of the SRAMs varied from 22. 4 to 25. 2ns at  $V_{DD} = 5V$  in the temperature range of -55 to  $125^{\circ}$ C before irradiation. The degradation was less than 0. 5ns after irradiation to  $1 \times 10^6$  rad(Si).

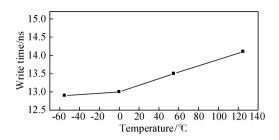

The write time (write pulse) as a function of the temperature from -55 to  $125^{\circ}$ C is shown in Fig. 6 for  $1.2\mu$ m PDSOI 64k SRAM. The write time of the SRAM varied from 12.9 to 14.1ns at  $V_{\rm DD} = 5$ V in the temperature range of -55 to  $125^{\circ}$ C before irradiation. The degradation was less than 0.5ns after irradiation to  $1 \times 10^6$  rad(Si).

Fig. 5 Access time as a function of temperature

Fig. 6 Write time as a function of temperature

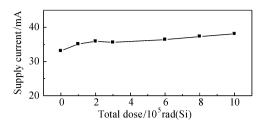

SRAM operating power supply currents were measured as a function of total dose through  $1 \times 10^6 \, \text{rad}(\text{Si})$  at  $V_{\text{DD}} = 5 \, \text{V}$ . The results are shown in Fig. 7.

#### 4 Conclusions

$1\times10^6\,\mathrm{rad}\,\mathrm{(Si)}$  total dose hardened partially depleted top and back gate individual 1.  $2\mu\mathrm{m}$  transistors have been fabricated in SIMOX. The first total dose hardened 1.  $2\mu\mathrm{m}$  PDSOI 64k SRAM has been demonstrated. The address access time of the SRAM varied from 22. 4 to 25.  $2\mathrm{ns}$  at  $V_\mathrm{DD}=5\mathrm{V}$  in the temperature range of -55 to  $125^\circ\mathrm{C}$ . Typical access time degradation was less than 0.  $5\mathrm{ns}$  after irradiation to  $1\times10^6\,\mathrm{rad}(\mathrm{Si})$ . The standby current of the 64k SRAM was only 0.  $8\mathrm{mA}$  at  $1\times10^6\,\mathrm{rad}(\mathrm{Si})$  which is less than the specified  $10\mathrm{mA}$ . The operating supply current of the SRAM was  $38.1\mathrm{mA}$ , which is less than the specified  $100\mathrm{mA}$ .

Fig. 7 Power supply current as a function of temperature

#### References

- [1] Zhao Hongchen, Hai Chaohe, Han Zhengsheng, et al. Radiation hardened H-type PDSOI nMOSFETs. Journal of Functional Materials and Devices, 2005, 1(2):71

- [2] Liu Xinyu, Liu Yunlong, Sun Haifeng, et al. Radiation characteristics of N<sub>2</sub>O-annealed H<sub>2</sub>-O<sub>2</sub> grown oxide. Chinese Journal of Semiconductors, 2001, 22(12):1597 (in Chinese) [刘新宇,刘运龙,孙海锋,等. 氮化 H<sub>2</sub>-O<sub>2</sub> 合成薄栅氧抗辐照特性.半导体学报, 2001, 22(12):1597]

- [3] Liu Xinyu, Liu Yunlong, Sun Haifeng, et al. Characteristics on total-dose of radiation hardness for CMOS/SOI 4kb SRAM. Chinese Journal of Semiconductors, 2002, 23(2):213 (in Chinese) [刘新宇,刘运龙,孙海锋,等. COMS/SOI 4kb SRAM 总剂量辐照实验.半导体学报, 2002, 23(2):213]

- [4] Liu Xinyu, Sun Haifeng, Liu Hongmin, et al. CMOS/SOI 4kb SRAM. Chinese Journal of Semiconductors, 2002, 8(2): 165 (in Chinese) [刘新宇,孙海峰,刘洪民,等. CMOS/SOI 4kb 静态随机存储器.半导体学报, 2002, 8(2):165]

- [5] Schwank J R. Ferlet-Cavrois V. Shaneyfelt M R. et al. Radiation effects in SOI technologies. IEEE Trans Nucl Sci, 2003, 50(3):522

- [6] Simgui BONDED wafer specifications-SIMGUI @ HD. Shanghai Simgui Technology Co.Ltd

# 总剂量辐照加固的 PDSOI CMOS 64k 静态随机存储器

郭天雷<sup>†</sup> 赵发展 刘 刚 李多力 李 晶 赵立新 周小茵 海潮和 韩郑生 (中国科学院徽电子研究所,北京 100029)

摘要:在国内首次使得  $1.2\mu m$  部分耗尽 SOI 64k 静态随机存储器的抗总剂量能力达到了  $1\times10^6$  rad(Si),其使用了 SIMOX 晶圆.在  $-55\sim125$  C 范围内,该存储器的数据读取时间几乎不变.在经过剂量为  $1\times10^6$  rad(Si)的总剂量辐照后,该存储器的数据读取时间也几乎不变,静态功耗仅从辐照前的  $0.65\mu A$  变化为辐照后的 0.8m A,远远低于规定的 10m A 指标;动态功耗仅从辐照前的 33m A 变化为辐照后的 38.1m A,远远低于规定的 100m A 指标.

关键词:部分耗尽 SOI;静态随机存储器;总剂量;辐照

EEACC: 1265; 1265D

中图分类号: TN47 文献标识码: A 文章编号: 0253-4177(2007)08-1184-03