## Multiplexer Design Applied to High-Speed Signal Transmission\*

Cao Hanmei<sup>1,†</sup>, Yang Yintang<sup>1</sup>, Cai Wei<sup>2</sup>, Lu Tiejun<sup>2</sup>, and Wang Zongmin<sup>2</sup>

(1 Key Laboratory of Ministry of Education for Wide Band-Gap Semiconductor Materials and Devices,

Microelectronics Institute, Xidian University, Xi'an 710071, China)

(2 Beijing Microelectronics Institute of Technology, Beijing 100076, China)

Abstract: A multiplexer with a low-distortion high-bandwidth analog switch is presented. The gate-to-source voltage of the switch is set by the combined on-voltage of a pMOS and an nMOS, and the difference between its gate-source voltage and the threshold voltage ( $V_{\rm GST}$ ) is guaranteed to be constant with input variation. Thus, the body effect is nearly canceled. Implemented in a TSMC 0.  $18\mu \rm m$  CMOS process, results from HSPICE simulation show that the  $V_{\rm GST}$  is nearly constant with an input range from 0. 3 to 1.7V, and the  $-3\rm dB$  bandwidth is larger than 10GHz; the SFDR (spurious free dynamic range) of the output is 67. 11dB with 1GHz input frequency; the turn-on time is 2. 98ns, and the turn-off time is 1. 35ns, which indicates a break-before-make action of the multiplexer. The proposed structure can be applied to high speed signal transmission.

Key words: low-distortion; high speed; multiplexer; analog switch

**EEACC:** 2570

CLC number: TN432.1

Document code: A

Article ID: 0253-4177(2008)06-1040-04

### 1 Introduction

In high speed signal transmission and multi-channel analog-to-digital converter (ADC) systems, the design of high-linearity low-distortion input switches and multiplexers is critical because variation in the on-resistance ( $R_{\rm on}$ ) can introduce distortion. This variation can be easily demonstrated by the on-resistance of a simple MOS-only switch which can be written as:

$$R_{\rm on} = \frac{1}{\mu_{\rm n} C_{\rm ox} \frac{W}{L} (V_{\rm G} - V_{\rm in} - V_{\rm th})}$$

(1)

where  $V_{\rm G}$  is the gate-voltage of the switch,  $V_{\rm in}$  is the input voltage, and  $V_{\rm th}$  is the threshold-voltage and is given as  $V_{\rm th} = V_{\rm t0} + \gamma (\sqrt{2|\phi_{\rm F}|} + V_{\rm SB} - \sqrt{2|\phi_{\rm F}|})$ . Equation (1) shows that the on-resistance is dependent on the input. On the other hand, the  $-3{\rm dB}$  bandwidth is also limited by  $R_{\rm on}$  with load capacitance  $C_{\rm hold}$  constant, and is:

$$f_{-3dB} = \frac{1}{2\pi R_{\text{on}} C_{\text{hold}}} \tag{2}$$

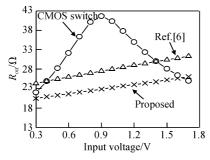

From the above analysis, the main limitation of the MOS-only switch is the non-linearity of  $R_{\rm on}$  and its limitation on the input bandwidth. In order to solve these problems, a CMOS switch and a boostrap switch are used. However, despite improvements in the linearization of  $R_{\rm on}$  in a CMOS switch, the corresponding nonlinearities in n- and p-transistors are not matched and substantial variation in  $R_{\rm on}$  still occurs.

Boostrap switches can make the gate-source voltage constant, but have body effects. References  $[1 \sim 3]$  presented some solutions. The main idea of Ref. [1] is to make the well connect to the source when the switch is on, but there is parasitic capacitance with the well. Other solutions may limit the input bandwidth or increase the complexity of the design.

In this paper, a low-distortion high-bandwidth analog switch is presented and is applied to a 2:1 multiplexer, not only making the difference of gate-source voltage and the threshold voltage ( $V_{\rm GST}$ ) constant and achieving a significantly higher linearity, but also achieving feasibility for high-speed signal transmission and meeting the requirement of break-before-make action of the multiplexer.

## 2 Proposed constant $V_{GST}$ switch

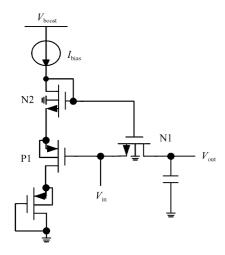

The proposed constant  $V_{\rm GST}$  switch is shown in Fig. 1. The *I-V* relation of MOSFET operating in saturation is:

$$I = \frac{1}{2}\mu C_{\text{ox}} \frac{W}{L} (V_{\text{gs}} - V_{\text{TH}})^2$$

(3)

Therefore,

$$V_{\rm gs} = \sqrt{\frac{2I}{\mu C_{\rm ox}(W/L)}} + V_{\rm TH} \tag{4}$$

From Fig. 1, the following relation can be obtained:

$$V_{\rm gs, N2} + V_{\rm sg, P1} = V_{\rm gs, N1}$$

(5)

Substituting Eq. (4) into Eq. (5), then:

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (Nos. 60476046,60676009)

<sup>†</sup> Corresponding author. Email: flysnow1978@163.com

Fig. 1 Proposed constant  $V_{GST}$  switch

$$V_{\rm gs,N1} = \sqrt{\frac{2I_{\rm bias}}{\mu_{\rm n}C_{\rm ox}(W/L)_{\rm N2}}} + V_{\rm TH,N2} + \sqrt{\frac{2I_{\rm bias}}{\mu_{\rm p}C_{\rm ox}(W/L)_{\rm P1}}} + V_{\rm TH,P1}$$

(6)

Therefore, the  $V_{\rm GST}$  of switch N1 is:

$$V_{\text{GST,N1}} = \sqrt{\frac{2I_{\text{bias}}}{\mu_{\text{n}} C_{\text{ox}} (W/L)_{\text{N2}}}} + V_{\text{TH,N2}} - V_{\text{TH,N1}} + \sqrt{\frac{2I_{\text{bias}}}{\mu_{\text{p}} C_{\text{ox}} (W/L)_{\text{Pl}}}} + V_{\text{TH,Pl}}$$

(7)

The threshold voltage of N1 and N2 has the same variation with input, so the body effect of N1 and N2 can compensate each other, and P1 has no body effect because its well is tied to its source. Therefore, the proposed switch has a constant on-resistance and very low distortion.

# 3 Proposed multiplexer using proposed constant $V_{GST}$ switch

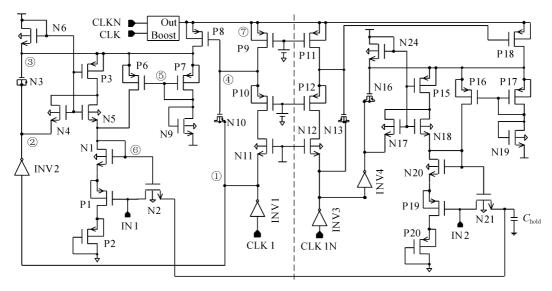

Figure 2 is the proposed 2:1 multiplexer. N1,

N2, P1, P2, P6, P7, N9 and N20, N21, P19, P20, P16, P17, N19 form the circuit realization of a constant  $V_{\rm GST}$  switch, respectively. The other part is used to determine which channel is selected; the Boost block is a boostrap circuit which makes the voltage of node ?  $2V_{\rm dd}$ , and has the same structure as Ref. [4]. The operation of the multiplexer is as follows: when clock CLK1 is low and CLK1N is high, the voltage of node 4 is boosted to be  $2V_{dd}$  by MOS capacitor N10. Because the voltage of node  $\bigcirc$  is also  $2\,V_{\rm dd}$  , transistor P8 is off. At the same time, the voltage of node ② is low, and transistor N4 is on, making the voltage of node 6 low, the nMOS switch N2 off, and the input signal IN2 transmit to the output. On the contrary, when clock CLK1 is high and CLK1N is low, the voltage of node 4 is  $V_{\rm dd}$  and transistor P8 is on, which makes the voltage of node  $\ensuremath{\text{@}}\xspace 2\,V_{\mathrm{dd}}$ . Then, P7 and N9 is on to provide bias current to transistor N1 and P1, turning switch N2 on and transmitting input signal IN1 to the output.

#### 4 Simulation results

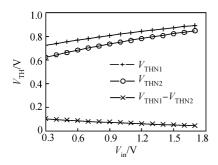

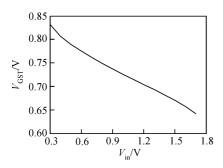

Based on a TSMC 0.  $18\mu m$  CMOS process, the circuit is simulated with HSPICE tools. Figure 3 shows the threshold voltage variation of transistor N1 and N2 with respect to the input signal level. The threshold voltage of transistor N1 changes in substantial unison with the threshold voltage of transistor N2, so the body effect of the two transistors remains the same to compensate each other. Figure 4 is the  $V_{\rm GST}$  performance of the switch. With a 1.8V power supply, the  $V_{\rm GST}$  changes from 0.83 to 0.64V with the input ranging between 0.3  $\sim$  1.7V, an improvement over Ref. [5] which has a  $V_{\rm gs}$  variation of 200 mV.

Fig. 2 Proposed multiplexer

Fig. 3 Threshold voltage variation

Fig. 4  $V_{GST}$  variation with input signal

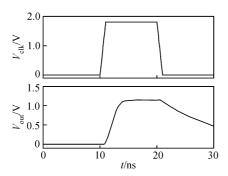

Figure 5 is  $R_{\rm on}$  versus input for three switches (a regular CMOS, a boostrap switch from Ref. [6], and the proposed), and the proposed switch has the most flatness. A good multiplexer has a break-before-make switch action that guarantees only one channel is selected at a time. Using the test method given in Ref. [7], Figure 6 shows the turn-on and turn-off performance of the switch with input constant at 1.2V. The turn-on and turn-off time is 2.98 and 1.35ns, respectively, which indicates a break-before-make action.

Fig. 5 On-resistance variation with input

Fig. 6 Turn-on and turn-off performance

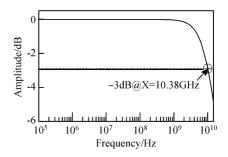

Fig. 7 - 3dB bandwidth of the switch

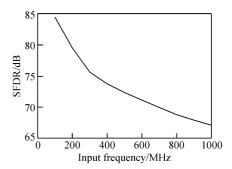

Fig. 8 SFDR versus input frequency

Figure 7 shows the frequency response of the switch. Its -3dB bandwidth can be larger than 10GHz, which allows the multiplexer to transmit signals with GHz frequency. Figure 8 is the SFDR of the output versus input frequency with a 0.8V peak-peak input. As input frequency increases, the SFDR decreases, and the SFDR is 67.11dB with 1GHz input frequency.

#### 5 Conclusion

A multiplexer is proposed with a low-distortion high-bandwidth analog switch. The gate-source voltage of the switch is set by the on-voltage of an nMOS and a pMOS, not only making the difference of gate-source voltage and the threshold voltage constant, achieving a significantly higher linearity, but also making high-speed signal transmission feasible. The -3dB bandwidth of the switch is larger than 10GHz, and the turn-on and turn-off time is 2.98 and 1.35ns, respectively, which guarantees the break-before-make action of the multiplexer. Spectral analysis shows that the SFDR is 67.11dB with an input frequency of 1GHz. The proposed structure is suitable for high speed signal transmission.

#### References

[1] Fayomi CJB.Roberts GW.Sawan M. Low-voltage CMOS analog bootstrapped switch for sample-and-hold circuit: design and chip characterization. IEEE Proc Int Symp Circuits Systems, Kobe. Japan, 2005, 5:2200

- [2] Yang C Y, Hung C C. A low-voltage low-distortion MOS sampling switch. IEEE Proc Int Symp Circuits Systems, Kobe, Japan, 2005, 5;3131

- [3] Wang L, Yin W J, Xu J, et al. Dual-channel bootstrapped switch for high-speed high-resolution sampling. Electron Lett, 2006, 42 (22):1275

- [4] Shantanu A B, Abhishek V C, Rajendra M P. A CMOS low voltage charge pump. 20th International Conference on VLSI Design,

- Bangalore, India, 2007:941

- [5] Devrim A, Mohammad A, Franco M. Switch bootstrapping for precise sampling beyond supply voltage. IEEE J Solid-State Circuits, 2006, 41(8):1938

- [6] Zheng Xiaoyan, Guo Shubao, Wang Jiang, et al. A low-voltage low-power CMOS sample-and-hold circuit.6th International Conference on ASIC, 2005, 2:552

- $\left[\ 7\ \right]\ MAX4514\text{-}MAX4515$  data sheet, http://www.maxim-ic.com.cn

## 应用于高速信号传输系统的多路选择器\*

曹寒梅1, 前 杨银堂1 蔡 伟2 陆铁军2 王宗民2

(1 西安电子科技大学微电子学院,宽禁带半导体材料与器件教育部重点实验室,西安 710071) (2 北京微电子技术研究所,北京 100076)

摘要:提出了一种能够传输高速信号的多路选择器,并为其设计了一种低失真、宽带模拟开关.所提出开关的栅源过驱动电压由 nMOS 和 pMOS 的开启电压之和决定,并能够确保输入变化时,开关的栅源电压与阈值电压之差( $V_{GST}$ )保持恒定,从而基本消除了体效应的影响.采用 TSMC  $0.18\mu m$  CMOS 工艺,HSPICE 仿真结果表明,输入信号在  $0.3\sim1.7V$  之间变化时,开关的  $V_{GST}$ 基本保持恒定,其 -3dB 带宽大于 10GHz,当输入频率为 1GHz 时,其无杂散动态范围为 67.11dB;开关的开启时间为 2.98ns,关断时间为 1.35ns,确保了多路选择器的 break-before-make 特性.该结构可应用于高速信号传输系统中.

关键词: 低失真; 高速; 多路选择器; 模拟开关

**EEACC**: 2570

中图分类号: TN432.1 文献标识码: A 文章编号: 0253-4177(2008)06-1040-04

<sup>\*</sup> 国家自然科学基金资助项目(批准号:60476046,60676009)

<sup>†</sup>通信作者.Email:flysnow1978@163.com 2007-12-11 收到,2008-01-23 定稿