# A two-dimensional analytical model of fully depleted asymmetrical dual material gate double-gate strained-Si MOSFETs\*

Li Jin(李劲)<sup>1,2,†</sup>, Liu Hongxia(刘红侠)<sup>1</sup>, Yuan Bo(袁博)<sup>1</sup>, Cao Lei(曹磊)<sup>1</sup>, and Li Bin(李斌)<sup>1</sup>

<sup>1</sup>Key Laboratory of Ministry of Education for Wide Bandgap Semiconductor Devices, School of Microelectronics, Xidian University, Xi'an 710071, China

<sup>2</sup>School of Information and Electrical Engineering, Hunan University of Science and Technology, Xiangtan 411201, China

**Abstract:** On the basis of the exact resultant solution of two dimensional Poisson's equations, a new accurate twodimensional analytical model comprising surface channel potentials, a surface channel electric field and a threshold voltage for fully depleted asymmetrical dual material gate double-gate strained-Si MOSFETs is successfully developed. The model shows its validity by good agreement with the simulated results from a two-dimensional numerical simulator. Besides offering a physical insight into device physics, the model provides basic design guidance for fully depleted asymmetrical dual material gate double-gate strained-Si MOSFETs.

Key words: dual material gate; double-gate MOSFET; strained-Si; short-channel effect; the drain-induced barrierlowering

DOI: 10.1088/1674-4926/32/4/044005

PACC: 7330; 7340R; 7215N

# 1. Introduction

Double-gate MOSFETs seem to be a very promising option for ultimate scaling of CMOS technology<sup>[1]</sup>. Excellent short-channel effect (SCE) immunity, high transconductance, and ideal subthreshold performance<sup>[2,3]</sup> have been reported from theoretical and experimental work on this device. In particular, asymmetrical DG SOI MOSFETs are becoming popular since these structures provide a desirable threshold voltage unlike symmetrical DG SOI MOSFETs. To enhance the immunity against SCEs, a new structure called a dual-material (DMG) gate MOSFET has been proposed. A dual-material gate structure induces the peak of the electric field at the interface between the different materials, which enhances the carrier's speed and improves the device's performance [4-6]. In addition, strained-Si devices can enhance mobility, high-field velocity and velocity overshoot of carriers are promising candidates for future high-performance MOSFETs<sup>[7]</sup>. To incorporate the advantage of asymmetrical DG MOSFETs and dual-material gate structure and strained-Si devices, the asymmetrical dual material gate double-gate strained-Si MOSFET has been proposed. In this paper, a novel, fully depleted asymmetrical dual material gate double-gate strained-Si MOSFETs is investigated. The analytical models for surface potential distribution and threshold voltage are derived based on the two dimensional Poisson's equations. The models are verified by the simulation results that agree well with those of the two-dimensional numerical simulator. With appropriate modification, the model can also be extended to asymmetrical and symmetrical DG MOSFETs.

# 2. Strained-Si MOSFET

### 2.1. Effect of strain on bandgap

In the presence of strain, the silicon thin film experiences biaxial tension and changes its band structure<sup>[8–11]</sup>. The strain can increase the electron affinity of silicon. It can also cause the bandgap and the effective mass of carriers to decrease. The above strain-related effects on the silicon band structure are modeled as follows<sup>[12, 13]</sup>,

$$(\Delta E_{\rm C})_{\rm s-Si} = 0.57X,\tag{1}$$

$$(\Delta E_{\rm g})_{\rm s-Si} = 0.4X,\tag{2}$$

$$V_{\rm T} \ln \frac{N_{\rm V, Si}}{N_{\rm V, s-Si}} = V_{\rm T} \ln \left(\frac{m_{\rm h, Si}^*}{m_{\rm h, s-Si}^*}\right)^{3/2} = 0.075X, \quad (3)$$

where X is the strain in the equivalent Ge mole fraction in the relaxed SiGe butter layer,  $(\Delta E_C)_{s-Si}$  is the increase in electron affinity of silicon due to strain,  $(\Delta E_g)_{s-Si}$  is the decrease in the bandgap of silicon due to strain, and  $V_T$  is the thermal voltage.  $N_{V,Si}$  and  $N_{V,s-Si}$  are the density of states (DOS) in the valence band in normal and strained-Si, respectively,  $m_{h,Si}^*$  and  $m_{h,s-Si}^*$  are the effective masses of hole DOS in normal and strained-Si, respectively.

#### 2.2. Effect of strain on flatband voltage

Since the structure is symmetrical, the effect of strain on the front-channel flatband and back-channel flatband voltage of this structure MOSFET can be modeled as follows<sup>[12, 13]</sup>,

† Corresponding author. Email: lijinpower@126.com Received 26 September 2010, revised manuscript received 5 November 2010

<sup>\*</sup> Project supported by the National Natural Science Foundation of China (Nos. 60976068, 60936005), the Cultivation Fund of the Key Scientific and Technical Innovation Project, Ministry of Education of China (No. 708083), and the Specialized Research Fund for the Doctoral Program of Higher Education (No. 200807010010).

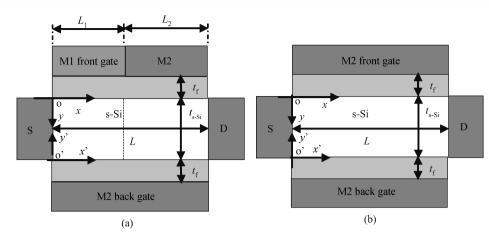

Fig. 1. Schematic structure of (a) a asymmetrical DMG DG strained-Si MOSFET and (b) a symmetrical DG strained-Si MOSFET.

$$(V_{\rm FB, f})_{\rm s-Si} = (V_{\rm FB, f})_{\rm Si} + \Delta V_{\rm FB, f}, \qquad (4)$$

where

$$(V_{\text{FB}, f})_{\text{Si}} = \varphi_{\text{M}} - \varphi_{\text{Si}},$$

$$\Delta V_{\text{FB}, f} = \frac{-(\Delta E_{\text{C}})_{\text{s-Si}}}{q} + \frac{(\Delta E_{\text{g}})_{\text{s-Si}}}{q} - V_{\text{T}} \ln \frac{N_{\text{V}, \text{Si}}}{N_{\text{V}, \text{s-Si}}},$$

$$\phi_{\text{Si}} = \chi_{\text{Si}}/q + E_{\text{g}, \text{Si}}/2q + \phi_{\text{f-Si}},$$

$$\phi_{\text{f-Si}} = V_{\text{T}} \ln(N_{\text{A}}/n_{\text{i}, \text{Si}}).$$

In the above relations,  $\phi_{\rm M}$  is the work function of the gate,  $\phi_{\rm Si}$  is the work function of unstrained-Si,  $\phi_{\rm f-Si}$  is the Fermi potential of unstrained-Si,  $E_{\rm g,Si}$  is the bandgap of unstrained-Si, q is the electronic charge,  $N_{\rm A}$  is the body doping concentration, and  $n_{\rm i,Si}$  is the intrinsic carrier concentration in unstrained-Si.

It is also important to consider the effect of strain on the built-in voltage across the source-body and drain-body junctions in strained-Si thin film, which can be written as

$$V_{\text{bi},\text{s-Si}} = V_{\text{bi},\text{Si}} + (\Delta V_{\text{bi}})_{\text{s-Si}},\tag{5}$$

where

$$V_{\text{bi, Si}} = \frac{E_{\text{g, Si}}}{2q} + \phi_{\text{F, Si}},$$

$$(\Delta V_{\text{bi}})_{\text{s-Si}} = \frac{-(\Delta E_{\text{g}})_{\text{s-Si}}}{q} - V_{\text{T}} \ln \frac{N_{\text{V, Si}}}{N_{\text{V, s-Si}}}.$$

## 3. Model formulation

#### 3.1. Two-dimensional model for surface potential

The schematic cross-section view of an FD asymmetrical DMG DG strained-Si MOSFET is shown in Fig. 1(a), and that of symmetrical DG strained-Si MOSFET is shown in Fig. 1(b). In Fig. 1(a), the lengths of the gate metals M1 and M2 are  $L_1$  and  $L_2$ , respectively. Assuming the channel doping to be uniform, the channel region is divided into two different zones since two kinds of gate materials are used. Neglecting the effect of the fixed oxide charges on the electrostatics of the channel, the Poisson's equation of the potential distribution in the two strained-Si zones before the onset of strong inversion can be written as<sup>[14-16]</sup>

$$\frac{\partial^2 \phi_1(x, y)}{\partial x^2} + \frac{\partial^2 \phi_1(x, y)}{\partial y^2} = \frac{qN_A}{\varepsilon_{Si}},$$

$$0 \le x \le L_1, 0 \le y \le t_{s-Si}, \quad (6)$$

$$\frac{\partial^2 \phi_2(x, y)}{\partial x^2} + \frac{\partial^2 \phi_2(x, y)}{\partial y^2} = \frac{q N_{\rm A}}{\varepsilon_{\rm Si}},$$

$$L_1 \le x \le L, 0 \le y \le t_{\rm s-Si}, \quad (7)$$

$$\frac{\partial^2 \phi_3(x', y')}{\partial x'^2} + \frac{\partial^2 \phi_3(x', y')}{\partial y'^2} = \frac{qN_A}{\varepsilon_{Si}},$$

$$0 \le x' \le L_1, 0 \le y' \le t_{s-Si}, \quad (8)$$

$$\frac{\partial^2 \phi_4(x', y')}{\partial x'^2} + \frac{\partial^2 \phi_4(x', y')}{\partial y'^2} = \frac{qN_A}{\varepsilon_{Si}},$$

$$L_1 \le x' \le L, 0 \le y' \le t_{s-Si}, \quad (9)$$

where  $N_A$  is the doping density of the strained-Si layer,  $\varepsilon_{Si}$  is the dielectric constant of the strained-Si layer,  $t_{s-Si}$  is the thickness of the strained-Si layer, L is the gate length, and  $L = L_1 + L_2$ , with the *x*-axis parallel to the channel and the *y*-axis perpendicular to the channel. The potential profile in the vertical direction in the strained-Si layer can be approximated by a parabolic function,

$$\phi_1(x, y) = \phi_{s1}(x) + c_{11}(x)y + c_{12}(x)y^2,$$

$$0 \le x \le L_1, 0 \le y \le t_{s-Si}, \quad (10)$$

$$\phi_2(x, y) = \phi_{s2}(x) + c_{21}(x)y + c_{22}(x)y^2,$$

$$L_1 \le x \le L, \ 0 \le y \le t_{s-Si}, \quad (11)$$

$$\phi_{3}(x', y') = \phi_{b1}(x') + c_{31}(x')y' + c_{32}(x')y'^{2},$$

$$0 \le x' \le L_{1}, 0 \le y' \le t_{\text{s-Si}}, \quad (12)$$

$$\phi_4(x', y') = \phi_{b2}(x') + c_{41}(x')y' + c_{42}(x')y'^2,$$

$$L_1 \leq x' \leq L, \ 0 \leq y' \leq t_{\text{s-Si}}, \quad (13)$$

where  $\phi_{s1}(x)$  and  $\phi_{s2}(x)$  are the front channel surface potential under M1, M2, respectively, and  $\phi_{b1}(x')$  and  $\phi_{b2}(x')$  is the back channel surface potential. The coefficients  $c_{11}(x)$ ,  $c_{12}(x)$ ,  $c_{21}(x)$  and  $c_{22}(x)$  are only functions of x, and  $c_{31}(x')$ ,  $c_{32}(x')$ ,  $c_{41}(x')$  and  $c_{42}(x')$  are only functions of x'. The Poisson's equations can be solved using the following boundary conditions.

(1) At the top side, the electric flux (displacement) at the gate-oxide/strained-Si layer interface is continuous, i.e.,

$$\left. \frac{\mathrm{d}\phi_1(x,y)}{\mathrm{d}y} \right|_{y=0} = \frac{\varepsilon_{\mathrm{ox}}}{\varepsilon_{\mathrm{Si}}} \frac{\phi_{\mathrm{s1}}(x) - V'_{\mathrm{GS1}}}{t_{\mathrm{f}}},\tag{14}$$

$$\left. \frac{\mathrm{d}\phi_2(x,y)}{\mathrm{d}y} \right|_{y=0} = \frac{\varepsilon_{\mathrm{ox}}}{\varepsilon_{\mathrm{Si}}} \frac{\phi_{\mathrm{s2}}(x) - V'_{\mathrm{GS2}}}{t_{\mathrm{f}}},\tag{15}$$

$$\frac{\mathrm{d}\phi_3(x',y')}{\mathrm{d}y'}\Big|_{y'=t_{\mathrm{s}}\mathrm{s}\mathrm{i}} = \frac{\varepsilon_{\mathrm{ox}}}{\varepsilon_{\mathrm{S}\mathrm{i}}} \frac{V'_{\mathrm{GS1}} - \phi_3(x',t_{\mathrm{s}})}{t_{\mathrm{f}}},\qquad(16)$$

$$\left. \frac{\mathrm{d}\phi_4(x',y')}{\mathrm{d}y'} \right|_{y'=t_{\mathrm{sSi}}} = \frac{\varepsilon_{\mathrm{ox}}}{\varepsilon_{\mathrm{Si}}} \frac{V'_{\mathrm{GS2}} - \phi_4(x',t_{\mathrm{sSi}})}{t_{\mathrm{f}}},\qquad(17)$$

where  $\varepsilon_{ox}$  is the dielectric constant of the gate oxide,  $t_f$  is the gate oxide thickness and  $V_{GS}$  is the gate-to-source bias voltage,  $V'_{GS1} = V_{GS} - (V_{FB1,f})_{s-Si}, \quad V'_{GS2} = V_{GS} - (V_{FB2,f})_{s-Si},$   $(V_{FB2,f})_{Si} = \phi_{M2} - \phi_{Si}, (V_{FB1,f})_{Si} = \phi_{M1} - \phi_{Si}.$

(2) At the bottom side, the electric flux (displacement) of the gate-oxide/strained-Si layer interface is continuous, i.e.,

$$\left. \frac{\mathrm{d}\phi_1(x,y)}{\mathrm{d}y} \right|_{y=t_{\mathrm{s}\cdot\mathrm{Si}}} = \frac{\varepsilon_{\mathrm{ox}}}{\varepsilon_{\mathrm{Si}}} \frac{V_{\mathrm{GS2}}' - \phi_1(x,t_{\mathrm{s}\cdot\mathrm{Si}})}{t_{\mathrm{f}}},\qquad(18)$$

$$\left. \frac{\mathrm{d}\phi_2(x, y)}{\mathrm{d}y} \right|_{y=t_{\mathrm{sSi}}} = \frac{\varepsilon_{\mathrm{ox}}}{\varepsilon_{\mathrm{Si}}} \frac{V_{\mathrm{GS2}}' - \phi_2(x, t_{\mathrm{s-Si}})}{t_{\mathrm{f}}}, \qquad (19)$$

$$\left. \frac{\mathrm{d}\phi_3(x',y')}{\mathrm{d}y'} \right|_{y'=0} = \frac{\varepsilon_{\mathrm{ox}}}{\varepsilon_{\mathrm{Si}}} \frac{\phi_{\mathrm{bl}}(x') - V'_{\mathrm{GS2}}}{t_{\mathrm{f}}}, \qquad (20)$$

$$\left. \frac{\mathrm{d}\phi_4(x',y')}{\mathrm{d}y'} \right|_{y'=0} = \frac{\varepsilon_{\mathrm{ox}}}{\varepsilon_{\mathrm{Si}}} \frac{\phi_{\mathrm{b2}}(x') - V'_{\mathrm{GS2}}}{t_{\mathrm{f}}}.$$

(21)

(3) At the source side, the channel potential must be equal to the built-in potential for the junction of the source and body,

$$\phi_1(0,0) = \phi_S(0) = V_{\text{bi, s-Si}} = \phi_b(0) = \phi_3(0,0).$$

(22)

(4) At the drain side, the channel potential must be equal to the built-in potential for the junction of the source and body plus the drain-to-source bias voltage,

$$\phi_2(L, t_{\text{s-Si}}) = V_{\text{bi, s-Si}} + V_{\text{DS}} = \phi_4(L, t_{\text{s-Si}}),$$

(23)

where  $V_{\rm DS}$  is the drain-to-source bias voltage.

(5) The potential and the electric flux at the interface of M1and M2 are equal,

$$\phi_1(L_1, 0) = \phi_2(L_1, 0), \tag{24}$$

$$\phi_3(L_1, 0) = \phi_4(L_1, 0), \tag{25}$$

$$\frac{\mathrm{d}\phi_1(x,y)}{\mathrm{d}x}|_{x=L_1} = \frac{\mathrm{d}\phi_2(x,y)}{\mathrm{d}x}|_{x=L_1},\tag{26}$$

$$\frac{\mathrm{d}\phi_3(x',y')}{\mathrm{d}x'}|_{x'=L_1} = \frac{\mathrm{d}\phi_4(x',y')}{\mathrm{d}x'}|_{x'=L_1}.$$

(27)

Using the boundary condition equations. (10)–(13), one can obtain the coefficients  $c_{11}(x)$ ,  $c_{12}(x)$ ,  $c_{21}(x)$ ,  $c_{22}(x)$ ,  $c_{31}(x')$ ,  $c_{32}(x')$ ,  $c_{41}(x')$  and  $c_{42}(x')$ , and then obtain the expressions for  $\phi_1(x, y)$ ,  $\phi_2(x, y)$ ,  $\phi_3(x', y')$  and  $\phi_4(x', y')$ . Substituting  $\phi_1(x, y)$ ,  $\phi_2(x, y)$ ,  $\phi_1(x, y)$  and  $\phi_2(x, y)$  into Eqs. (6)–(9), respectively, and substituting y = 0 or y' = 0, one obtains

$$\frac{d^2\phi_{s1}(x)}{dx^2} - \alpha^2\phi_{s1}(x) = \beta_1,$$

(28)

$$\frac{d^2\phi_{s2}(x)}{dx^2} - \alpha^2\phi_{s2}(x) = \beta_2,$$

(29)

$$\frac{d^2\phi_{b1}(x')}{dx'^2} - \alpha^2\phi_{b1}(x') = \beta_3,$$

(30)

$$\frac{d^2\phi_{b2}(x')}{dx'^2} - \alpha^2\phi_{b2}(x') = \beta_4,$$

(31)

where

$$\alpha^{2} = \frac{2\varepsilon_{\text{ox}}}{\varepsilon_{\text{si}}t_{\text{f}}t_{\text{si}}},$$

$$\beta_{1} = \frac{qNA}{\varepsilon_{\text{si}}} - \frac{\varepsilon_{\text{ox}}}{\varepsilon_{\text{si}}} \frac{V_{\text{GS2}}' + (1+a_{1})V_{\text{GS1}}'}{t_{\text{f}}t_{\text{si}}\left(1+\frac{1}{2}a_{1}\right)},$$

$$\beta_{2} = \frac{qNA}{\varepsilon_{\text{si}}} - \frac{\varepsilon_{\text{ox}}}{\varepsilon_{\text{si}}} \frac{2V_{\text{GS2}}'}{t_{\text{f}}t_{\text{si}}} = \beta_{4},$$

$$\beta_{3} = \frac{qNA}{\varepsilon_{\text{si}}} - \frac{\varepsilon_{\text{ox}}}{\varepsilon_{\text{si}}} \frac{V_{\text{GS1}}' + (1+a_{1})V_{\text{GS2}}'}{t_{\text{f}}t_{\text{si}}\left(1+\frac{1}{2}a_{1}\right)}.$$

20

Here,  $a_1 = \frac{\varepsilon_{\text{ox}} t_{\text{si}}}{\varepsilon_{\text{Si}} t_{\text{f}}}$ .

The solutions for Eqs. (28)–(31) are simple second-order non-homogenous differential equations with constant coefficients, which can be written as

$$\phi_{s1}(x) = A \exp(\alpha x) + B \exp(-\alpha x) - \frac{\beta_1}{\alpha^2}, \qquad (32)$$

$$\phi_{s2}(x) = C \exp[\alpha(x - L_1)] + D \exp[-\alpha(x - L_1)] - \frac{\beta_2}{\alpha^2},$$

(33)

$$\phi_{b1}(x') = E \exp(\alpha x') + E \exp(-\alpha x') - \frac{\beta_3}{\alpha^3}$$

(34)

$$\phi_{b1}(x') = E \exp(\alpha x') + F \exp(-\alpha x') - \frac{\mu_3}{\alpha^2},$$

(34)

$$\phi_{b2}(x') = G \exp\left[\alpha(x' - L_1)\right] + H \exp\left[-\alpha(x' - L_1)\right] - \frac{\beta_4}{\alpha^2}.$$

(35)

Now, using boundary conditions (3), (4) and (5) to solve for A, B, C, D, E, F, G and H, one obtains

$$A = \left[\frac{\beta_2 - \beta_1}{2\alpha^2} \exp(\alpha L_2) + \frac{\beta_2 - \beta_1}{2\alpha^2} \exp(-\alpha L_2) - \frac{\beta_2}{\alpha^2} + \left(V_{\text{bi, s-Si}} + \frac{\beta_1}{\alpha^2}\right) \exp(-\alpha L) - V_{\text{bi, s-Si}} - V_{\text{DS}}\right] \times \left[\exp(-\alpha L) - \exp(\alpha L)\right]^{-1},$$

(36)

$$B = \left[\frac{\beta_2 - \beta_1}{2\alpha^2} \exp(\alpha L_2) + \frac{\beta_2 - \beta_1}{2\alpha^2} \exp(-\alpha L_2) - \frac{\beta_2}{\alpha^2} + \left(V_{\text{bi, s-Si}} + \frac{\beta_1}{\alpha^2}\right) \exp(\alpha L) - V_{\text{bi, s-Si}} - V_{\text{DS}}\right] \times \left[\exp(\alpha L) - \exp(-\alpha L)\right]^{-1},$$

(37)

$$C = A \exp(\alpha L_1) + \frac{\beta_2 - \beta_1}{2\alpha^2}, \qquad (38)$$

$$D = B \exp(-\alpha L_1) + \frac{\beta_2 - \beta_1}{2\alpha^2}, \qquad (39)$$

$$E = \left[\frac{\beta_4 - \beta_3}{2\alpha^2} \exp(\alpha L_2) + \frac{\beta_4 - \beta_3}{2\alpha^2} \exp(-\alpha L_2) - \frac{\beta_4}{\alpha^2} + \left(V_{\text{bi,s-Si}} + \frac{\beta_3}{\alpha^2}\right) \exp(-\alpha L) - V_{\text{bi,s-Si}} - V_{\text{DS}}\right] \times \left[\exp(-\alpha L) - \exp(\alpha L)\right]^{-1},$$

(40)

$$F = \left[\frac{\beta_4 - \beta_3}{2\alpha^2} \exp(\alpha L_2) + \frac{\beta_4 - \beta_3}{2\alpha^2} \exp(-\alpha L_2) - \frac{\beta_4}{\alpha^2} + \left(V_{\text{bi,s-Si}} + \frac{\beta_3}{\alpha^2}\right) \exp(\alpha L) - V_{\text{bi,s-Si}} - V_{\text{DS}}\right] \times \left[\exp(\alpha L) - \exp(-\alpha L)\right]^{-1},$$

(41)

$$G = E \exp(\alpha L_1) + \frac{\beta_4 - \beta_3}{2\alpha^2}, \qquad (42)$$

$$H = F \exp(-\alpha L_1) + \frac{\beta_4 - \beta_3}{2\alpha^2}.$$

(43)

The minimum potential of the front-channel and backchannel can be calculated from Eqs. (32)–(35) as

$$\phi_{\rm s1,\,min} = 2\sqrt{AB} - \frac{\beta_1}{\alpha^2},\tag{44}$$

$$\phi_{\rm s2,\,min} = 2\sqrt{CD} - \frac{\beta_2}{\alpha^2},\tag{45}$$

$$\phi_{b1,\min} = 2\sqrt{EF} - \frac{\beta_1}{\alpha^2},\tag{46}$$

$$\phi_{\rm b2,\,min} = 2\sqrt{GH} - \frac{\beta_4}{\alpha^2}.\tag{47}$$

The minimum occurs at

$$x_{\min, fl} = \frac{1}{2\alpha} \ln \frac{B}{A},$$

(48)

$$x_{\min, f2} = \frac{1}{2\alpha} \ln \frac{D}{C}, \qquad (49)$$

$$x_{\min, b1} = \frac{1}{2\alpha} \ln \frac{E}{F},$$

(50)

$$x_{\min, b2} = \frac{1}{2\alpha} \ln \frac{G}{H}.$$

(51)

The electric field pattern along the channel determines the electron transport velocity through the channel. The electric field horizontal components under the front gates and back gate are given as

$$E_{1,f}(x) = A\alpha \exp(\alpha x) - B\alpha \exp(-\alpha x), \qquad (52)$$

$$E_{2,f}(x) = C\alpha \exp \left[\alpha(x - L_1)\right] - D\alpha \exp \left[-\alpha(x - L_1)\right],$$

(53)

$$E_{1,b}(x) = E\alpha \exp(\alpha x) - F\alpha \exp(-\alpha x),$$

(54)

$$E_{2,b}(x) = G\alpha \exp \left[\alpha(x - L_1)\right] - H\alpha \exp \left[-\alpha(x - L_1)\right].$$

(55)

#### Li Jin *et al*.

#### 3.2. Two-dimensional model for threshold voltage

The threshold voltage  $V_{\text{TH}}$  is the value of the gate voltage  $V_{\text{GS}}$  at which a conducting channel of an SOI MOSFET is induced. In a fully depleted thin film SOI, it is desirable that the front channel turns on before the back channel. Therefore, the threshold voltage is taken to be that value of gate source voltage for which  $\phi_{\text{s1,min}} = 2\phi_{\text{F,Si}}$ , where  $\phi_{\text{F,Si}}$  is the difference between the extrinsic Fermi level in the bulk region and the intrinsic Fermi level. For the strained-Si SOI MOSFET, the threshold condition under the front gate is modified as<sup>[9,10]</sup>

$$\phi_{\rm s,\,min} = 2\phi_{\rm F,\,Si} + \Delta\phi_{\rm s-Si} = \phi_{\rm th},\tag{56}$$

where

$$\Delta \phi_{\text{s-Si}} = -\frac{(\Delta E_{\text{g}})_{\text{s-Si}}}{q} + V_{\text{T}} \ln \frac{N_{\text{V, Si}}}{N_{\text{V, s-Si}}}$$

$\phi_{\text{th}}$  is the value of surface potential at which the volumetric inversion electron charge density in the strained-Si device is the same as that in the unstrained-Si at threshold, i.e., equal to the body doping.

For an FD asymmetrical DMG DG structure, because of the different metal material M1 and M2, the threshold voltage is defined as the value of  $V_{\rm GS}$  in which the minimum between of the maximum of the front channel surface potential  $\phi_{\rm s1, min}$ and  $\phi_{\rm s2, min}$  equals  $\phi_{\rm th}$ , and the maximum of the back channel surface potential  $\phi_{\rm b1, min}$  and  $\phi_{\rm b1, min}$  equals  $\phi_{\rm th}$ . Hence, one can determine the value of the threshold voltage as the value of  $V_{\rm GS}$ by solving Eqs. (44)–(47).

The front gate threshold voltages can be expressed as

$$V_{\text{TH, f1}} = \frac{qNA}{\varepsilon_{\text{si}}\alpha^2} - \frac{-b_{\text{f1}} + \sqrt{b_{\text{f1}}^2 - 4a_{\text{f1}}c_{\text{f1}}}}{2a_{\text{f1}}} + (V_{\text{FB1, f}})_{\text{s-Si}}, (57)$$

$$V_{\text{TH, f2}} = \frac{qNA}{\varepsilon_{\text{si}}\alpha^2} - \frac{-b_{\text{f2}} + \sqrt{b_{\text{f2}}^2 - 4a_{\text{f2}}c_{\text{f2}}}}{2a_{\text{f2}}} + \frac{(V_{\text{FB1, f}})_{\text{s-Si}} + (1 + a_1)(V_{\text{FB2, f}})_{\text{s-Si}}}{2 + a_1}, \quad (58)$$

where

$$a_{f1} = 2 - \eta - \frac{h}{4},$$

$$b_{f1} = -Z - Y + m + \frac{V_1}{\alpha^2}(2 - \eta) - \frac{h}{2}\phi_{th},$$

$$c_{f1} = W_1 - \frac{h}{4}\phi_{th}^2h = 2 - \exp(2\alpha L) - \exp(-2\alpha L),$$

$$W_1 = ZY - (Z + Y)\frac{V_1}{\alpha^2} + \frac{V_1^2}{\alpha^4},$$

$$Z = \frac{V_1}{2\alpha^2} [\exp(\alpha L_2) + \exp(-\alpha L_2)] + V_{bi, s-Si}$$

$$\exp(-\alpha L) - V_{bi, s-Si} - V_{DS},$$

$$Y = \frac{V_1}{2\alpha^2} [\exp(\alpha L_2) + \exp(-\alpha L_2)] + V_{bi, s-Si}$$

$$\exp(\alpha L) - V_{bi, s-Si} - V_{DS},$$

$$\eta = [\exp(\alpha L) + \exp(-\alpha L)]m = Z \exp(\alpha L) + Y \exp(-\alpha L),$$

$$a_{\rm f2} = 2 - \eta - \frac{h}{4}$$

$$\begin{split} b_{f2} &= -Z - Y + m + \frac{V_1}{\alpha^2} \eta - \frac{2V_1}{\alpha^2} + h \frac{V_1}{2\alpha^2} - \frac{h}{2} \phi_{th}, \\ c_{f2} &= W_2 - \frac{h}{4} \phi_{th}^2, \\ W_2 &= ZY - \frac{V_1}{\alpha^2} m + \frac{V_1^2}{\alpha^4} + K \frac{V_1}{2\alpha^2} n \\ &+ \frac{V_1^2}{2\alpha^4} \left[ \exp(\alpha L_2) - \exp(-\alpha L^2) \right] + h \frac{V_1^2}{4\alpha^4} \\ V_1 &= \frac{\varepsilon_{ox}}{\varepsilon_{si}} \frac{1 + a_1}{t_f t_{si} \left( 1 + \frac{1}{2} a_1 \right)} \Delta \phi_{M}, \\ n &= Z \exp(\alpha L_1) - Y \exp(-\alpha L_1), \\ \Delta \phi_{M} &= \phi_{M2} - \phi_{M1}, \\ K &= \exp(\alpha L) - \exp(-\alpha L). \end{split}$$

So the front gate threshold voltage is the maximum of the front channel threshold voltage,

$$V_{\text{TH, f}} = \max[V_{\text{TH, f1}}, V_{\text{TH, f2}}].$$

(59)

The back gate threshold voltage can be expressed as

$$V_{\rm TH, b1} = \frac{qNA}{\varepsilon_{\rm si}\alpha^2} - \frac{-b_{\rm b1} + \sqrt{b_{\rm b1}^2 - 4a_{\rm b1}c_{\rm b1}}}{2a_{\rm b1}} + (V_{\rm FB1, f})_{\rm s-Si},$$

(60)

$$V_{\text{TH, b2}} = \frac{qNA}{\varepsilon_{\text{si}}\alpha^2} - \frac{-b_{\text{b2}} + \sqrt{b_{\text{b2}}^2 - 4a_{\text{b2}}c_{\text{b2}}}}{2a_{\text{b2}}} + \frac{(V_{\text{FB2, f}})_{\text{s-Si}} + (1+a_1)(V_{\text{FB1, f}})_{\text{s-Si}}}{2+a_1}, \quad (61)$$

where

$b_{\rm b}$

$$a_{b1} = 2 - \eta - \frac{h}{4},$$

$$b_{b1} = -Z - Y + m + \frac{V_2}{\alpha^2}(2 - \eta) - \frac{h}{2}\phi_{th},$$

$$c_{b1} = W_3 - \frac{h}{4}\phi_{th}^2,$$

$$V_2 = \frac{\varepsilon_{ox}}{\varepsilon_{si}} \frac{\Delta\phi M}{t_f t_{si} \left(1 + \frac{1}{2}a_1\right)},$$

$$W_3 = ZY - (Z + Y)\frac{V_2}{\alpha^2} + \frac{V_2^2}{\alpha^4},$$

$$a_{b2} = \left(2 - \eta - \frac{h}{4}\right)b_{b2}$$

$$= -Z - Y + m + \frac{V_2}{\alpha^2}\eta - \frac{2V_2}{\alpha^2} + h\frac{V_2}{2\alpha^2} - \frac{h}{2}\phi_{th},$$

$$b_{b2} = -Z - Y + m + \frac{2V_2}{\alpha^2} + \frac{V_2}{\alpha^2}\eta + \frac{V_2}{2\alpha^2}h - \frac{h}{2}\phi_{th},$$

$$c_{b2} = W_4 - \frac{h}{4}\phi_{th}^2,$$

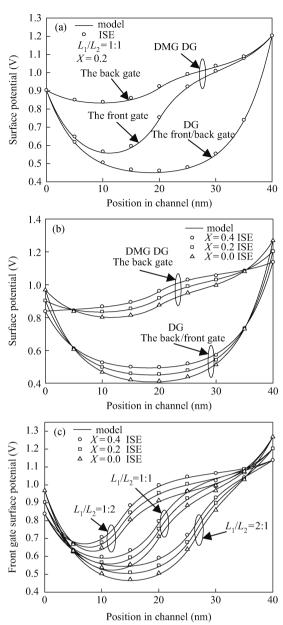

Fig. 2. Variation in the surface potential along the channel for the 40 nm DMG DG and DG strained-Si MOSFET. (a) Potential distribution of the front gate and back gate surface of the DMG DG and DG MOSFETs. (b) Potential distribution of the back gate surface of the DMG DG and DG MOSFETs. (c) Potential distribution of the front gate surface of the DMG DG MOSFETs.

$$W_{4} = ZY - \frac{V_{2}}{\alpha^{2}}m + \frac{V_{2}^{2}}{\alpha^{4}} + K\frac{V_{2}}{2\alpha^{2}}n + \frac{V_{2}^{2}}{2\alpha^{4}} \left[\exp(\alpha L_{2}) - \exp(-\alpha L_{2})\right] + h\frac{V_{2}^{2}}{4\alpha^{4}}.$$

So the back gate threshold voltage is the maximum of the back channel threshold voltage,

$$V_{\text{TH,b}} = \max[V_{\text{TH,b1}}, V_{\text{TH,b2}}].$$

(62)

So the threshold voltage is the minimum of the front channel threshold voltage and the back channel threshold voltage,

$$V_{\rm TH} = \min[V_{\rm TH,f}, V_{\rm TH,b}]. \tag{63}$$

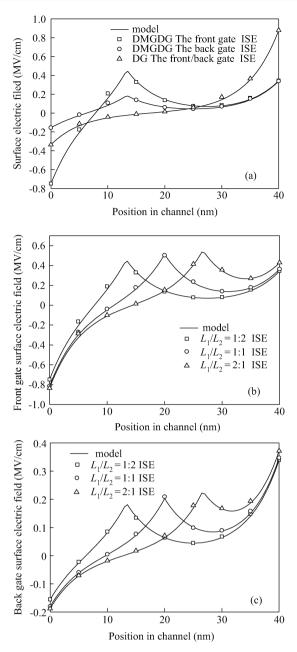

Fig. 3. Variation in the surface electric field within the channel for the 40 nm DMG DG and DG MOSFETs. (a) Surface electric field distribution of the front gate and the back gate surface of the DMG DG and DG MOSFETs. (b) Surface electric field distribution of the front gate of the DMG DG and DG MOSFETs. (c) Surface electric field distribution of the back gate of the DMG DG and DG MOSFETs.

# 4. Results and discussion

To verify the proposed analytical model, an FD n-channel asymmetry DMG DG structure, as shown in Fig. 1(a), was used. Typical values of the work function for gate metals M1 and M2 are chosen as 4.70 eV and 4.35 eV, respectively.  $t_f = 2 \text{ nm}$ ,  $t_{\text{s-Si}} = 10 \text{ nm}$ ,  $N_A = 1 \times 10^{17} \text{ cm}^{-3}$ .

In the following figures, the lines represent the results from the derived analytical models, and the symbols represent those from ISE.

Figure 2(a) shows the curve of the front gate surface potential and the back gate surface potential of the DMG DG

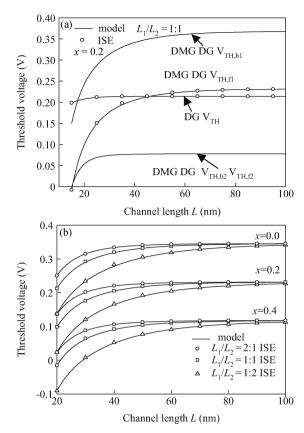

Fig. 4. Variation in threshold voltage along the channel for 100 nm DMG DG and DG MOSFETs. (a) Threshold voltage of DMG DG and DG MOSFETs. (b) Threshold voltage of DMG DG MOSFET changes with the gate length ratio and strain *X*.

strained-Si MOSFET and the front/back surface potential of the DG strained-Si MOSFET against the horizontal distance in the channel for L = 40 nm. It is clearly seen that the DMG DG structure exhibits a step function in the surface potential along the channel. Due to this unique feature, the area under M1 ploy front gate of the DMG structure is essentially screened from the drain-potential variations. This means that the drain-potential has very little effect on the drain current after saturation reducing the DIBL. Figure 2(b) shows the variation in the back gate surface potential of the DMG DG strained-Si MOSFET and the variation in the surface potential of the DG strained-Si MOSFET with the values of the effective Ge mole fraction in the relaxed  $Si_{1-x}Ge_x$  buffer. At the source and drain end, the surface potential decreases with an increase in the values of the effective Ge mole fraction in the relaxed  $Si_{1-x}Ge_x$  buffer. However, in the middle of the channel there is an increase in the potential barrier with increasing values of the effective Ge mole fraction in the relaxed  $Si_{1-x}Ge_x$  buffer. Figure 2(c) shows the variation in the front gate surface potential of the DMG DG strained-Si MOSFET with the values of the effective Ge mole fraction in the relaxed  $Si_{1-x}Ge_x$  buffer and the gate length ratio  $(L_1/L_2)$ . As the gate length ratio decreases, the step change of the potential moves toward the source end. We can see that at the source and drain end the surface potential decreases with increasing values of the effective Ge mole fraction in the relaxed  $Si_{1-x}Ge_x$  buffer. However, in the middle of the channel, the potential barrier increases with increasing values of the ef-

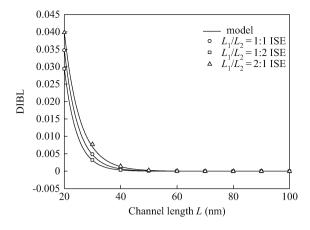

Fig. 5. Drain induced barrier lowing (DIBL) versus channel length L.

fective Ge mole fraction in the relaxed  $Si_{1-x}Ge_x$  buffer.

Figure 3(a) shows the variation in the front gate and back gate electric field of the DMG DG and DG strained-Si MOS-FET along the normalized channel portion with the gate length L = 40 nm. There is a peak electric field at the interface of M1 and M2 within the channel of the DMG DG MOSFET, and it accelerates the carrier transit speed. Figures 3(b) and 3(c) show the variation in the front gate and back gate electric field of the DMG DG strained-Si MOSFET with the gate length ratio. It can be seen that the peak electric field moves toward the source side as the gate length ratio decreases.

Figure 4(a) shows the variation in threshold voltage of the DMG DG and the DG strained-Si MOSFET with the gate length. It is observed that SCE become serious with decreasing channel length. Figure 4(b) shows the variation in threshold voltage with the gate length for different Ge mole fractions. It is observed that the threshold voltage is lower for higher strain in the silicon film and small gate length ratio  $(L_1/L_2)$  for a given channel length. The change with increasing Ge content x is due to the decrease in the flatband voltage, the decrease in the built-in potential barrier, and an earlier onset of inversion due to a decrease in  $\phi_{\text{th}}$ .

Figure 5 shows the variation in DIBL with channel length ratio for x = 0.2 Ge mole fraction for the DMG DG strained-Si MOSFET. The DIBL is obtained from the difference between the threshold voltage at high drain–drain source voltage ( $V_{ds} = 0.5$  V) and the threshold voltage value at low drain–drain source voltage ( $V_{ds} = 0.05$  V). It is observed that DIBL is significant for small channel lengths (40–50 nm), while it is negligible for longer channel lengths.

## 5. Conclusion

Based on the two-dimensional solution of Poisson's equation, the analytical model for asymmetrical DMG DG strained-Si MOSFET comprising surface potential, surface electric field and threshold voltage has been developed. It has been shown that the FD asymmetrical DMG DG strained-Si MOSFET reduces SCE and DIBL. The obtained results are in good agreement with the simulation results.

#### References

- Frank D J, Dennard R H, Nowak E, et al. Device scaling limits of Si MOSFET's and their application dependencies. Proc IEEE, 2001, 89(3): 259

- [2] Venkatesan S, Neudeck G W, Pierret R F. Dual-gate operation and volume inversion in n-channel SOI MOSFET's. IEEE Electron Device Lett, 1992, 13(1): 44

- [3] Djeffal F, Meguellati M, Benhaya A. A two-dimensional analytical analysis of subthreshold behavior to study the scaling capability of nanoscale graded channel gate stack DG MOSFETs. Physica E, 2009, 41(8): 1872

- [4] Kumar M J, Chaudhry A. Two-dimensional analytical modeling of fully depleted DMG SOI MOSFET and evidence for diminished SCEs. IEEE Trans Electron Devices, 2004, 51(4): 569

- [5] Chiage T K, Chen M L. A new analytical threshold voltage model for symmetrical double-gate MOSFETs with high-k gate dielectrics. Solid State Electron, 2007, 51(3): 387

- [6] Goel K, Saxena M, Gupta M, et al. Two-dimensional analytical threshold voltage model for DMG epi-MOSFET. IEEE Trans Electron Devices, 2005, 52(1): 23

- [7] Li J, Liu H X, Li B, et al. Two-dimensional threshold voltage analytical model of DMG strained-silicon-on-insulator MOSFETs. Journal of Semiconductors, 2010, 31(8): 084008

- [8] Yin H Z, Hobart K D, Peterson R L. Ultrathin strained-SOI by stress balance on compliant substrates and FET performance. IEEE Trans Electron Devices, 2005, 52(10): 2207

- [9] Mizuno T, Sugiyama N, Kurobe A, et al. Advance SOI p-MOSFETs with strained-Si channel on SiGe-on-insulator substrate fabricated by SIMOX technology. IEEE Trans Electron Devices, 2001, 48(10): 1612

- [10] Zhou X. Exploring the novel characteristics of hetero-material gate field-effect transistors (HMGFETs) with gate material engineering. IEEE Trans Electron Devices, 2000, 47(1): 113

- [11] Venkataraman V, Nawal S, Kumar M J. Compact analytical threshold-voltage model of nanoscale fully depleted strained-Si on silicon-germanium-on-insulator (SGOI) MOSFETs. IEEE Trans Electron Devices, 2007, 54(3): 554

- [12] Kumar M J, Venkataraman V, Nawal S. A simple analytical threshold voltage model of nanoscale single-layer fully depleted strained-silicon-on-insulator MOSFETs. IEEE Trans Electron Devices, 2006, 53(3): 2500

- [13] Yong K K. Short-channel effect in fully depleted SOI MOSFETS. IEEE Trans Electron Devices, 1989, 36(2): 399

- [14] Sharma R K, Gupta M, Gupta R S. Two-dimensional analytical subthreshold model of graded channel DG FD SOI n-MOSFET with gate misalignment effect. Superlattices and Microstructures, 2009, 45(1): 91

- [15] Rim K, Anderson R, Boyd D. Strained Si CMOS (SS CMOS) technology: opptunities and challenges. Solid State Electron, 2003, 47(7): 1133

- [16] Yang L F, Watling J R. Si/SiGe heterostructure parameters for device simulations. Semicond Sci Technol, 2004, 19(8): 1174