# A two-dimensional analytical-model-based comparative threshold performance ana-**Ivsis of SOI-SON MOSFETs**

Sanjoy Deb<sup>1</sup>, Saptarsi Ghosh<sup>1</sup>, N Basanta Singh<sup>2</sup>, A K De<sup>3</sup>, and Subir Kumar Sarkar<sup>1,†</sup>

<sup>1</sup>Department of Electronics & Telecommunication Engineering, Jadavpur University, Kolkata-700032, India <sup>2</sup>Department of Electronics & Communication Engineering, Manipur Institute of Technology, Imphal-795004, India <sup>3</sup>Department of Electronics & Communication Engineering, National Institute of Technology, Durgapur-713209, India

Abstract: A generalized threshold voltage model based on two-dimensional Poisson analysis has been developed for SOI/SON MOSFETs. Different short channel field effects, such as fringing fields, junction-induced lateral fields and substrate fields, are carefully investigated, and the related drain-induced barrier-lowering effects are incorporated in the analytical threshold voltage model. Through analytical model-based simulation, the threshold voltage roll-off and subthreshold slope for both structures are compared for different operational and structural parameter variations. Results of analytical simulation are compared with the results of the ATLAS 2D physicsbased simulator for verification of the analytical model. The performance of an SON MOSFET is found to be significantly different from a conventional SOI MOSFET. The short channel effects are found to be reduced in an SON, thereby resulting in a lower threshold voltage roll-off and a smaller subthreshold slope. This type of analysis is quite useful to figure out the performance improvement of SON over SOI structures for next generation short channel MOS devices.

Key words: silicon-on-insulator; silicon-on-nothing; Poisson's equation; short channel effects; threshold voltage roll-off; subthreshold slope **EEACC: 2570**

DOI: 10.1088/1674-4926/32/10/104001

## 1. Introduction

With the emergence of mobile computing and communication, low power device design and implementation have a significant role to play in VLSI circuit design<sup>[1]</sup>. Continuous device performance improvements are possible only through a combination of device scaling, new device structures and material property improvement<sup>[1]</sup>. Conventional silicon (bulk CMOS) technology has suffered from fundamental physical limitations in the sub-micron or nanometer region, which has led to alternative device technologies such as silicon-on-insulator (SOI) technology<sup>[2]</sup>. Short-channeleffects (SCEs) reduction, transistor scalability and circuit performance are improved by using SOI technology, especially ultrathin, fully depleted (FD) SOI MOSFETs<sup>[3]</sup>. SOI MOSFETs enable high speed applications because of their low parasitic capacitance<sup>[4]</sup>. The development of SOI MOSFET technology has been limited so far by the difficulty in controlling the silicon film thickness, adjusting the buried oxide layer thickness, shallow source drain series resistances and fringing fields [5-7]. Although different SCEs are highly suppressed in an SOI structure, it is not fully immune to some SCEs<sup>[8]</sup>. Among the different forms of SCE-related device performance degradation, higher threshold voltage roll-off and subthreshold slope are very important issues<sup>[9]</sup>. In an effort to overcome these drawbacks, improved SOI structures have been suggested in recent times<sup>[10]</sup>. Silicon-on-nothing (SON), an innovative SOI structure proposed and developed very recently, enables fabrication of extremely thin silicon (5 to 20 nm) and buried dielectric (10 to 30 nm) super SOI devices, which are capable of quasitotal suppression of SCEs and have excellent electrical performances<sup>[11]</sup>. In an SON MOSFET, the buried layer of an SOI MOSFET is replaced with an air layer. Among the advantages of fully depleted (FD) SON architecture over FDSOI structures the most significant one is the reduced electrostatic coupling of the channel with the source/drain and the substrate through the buried layer (BL)<sup>[12]</sup>. Reduced electrostatic coupling through the BL allows for the reduction of the transistor minimal channel length or a relaxation of the requirements regarding Si film thickness<sup>[13]</sup>. Moreover, since the so-called "nothing" (or air) layer embedded below the Si active film has a lower dielectric permittivity than an oxide, the parasitic capacitances between the source/drain and the substrate are reduced and therefore a higher circuit speed can be expected with SON devices<sup>[14]</sup>. The thick buried layer can be a drawback of SOI MOSFETs due to a large positive charge accumulating in the thick BL. However, in SON MOSFETs no charge will accumulate in the air  $gap^{[15]}$ .

To develop a generalized SOI/SON MOSFET analytical model, accurate modeling of different SCEs like drain induced barrier lowering (DIBL) or 2D charge sharing (2DCS) are essential, as these effects need to be incorporated in the analytical model. Also the effects are different for the two structures. Using a 2D Poisson's equation solution, some threshold voltage models of SOI MOSFETs have been  $proposed^{[16-20]}$ . The theoretical approach<sup>[21]</sup> adopted can be extended to develop a generalized threshold voltage model of an SOI/SON MOSFET that incorporates different SCEs, such as DIBL and 2DCS, for comparison of their performances. To incorporate SCE modification in an SON structure, fringing field and substrate bias effects should be carefully modeled as these are the main rea-

<sup>†</sup> Corresponding author. Email: su\_sircir@yahoo.co.in Received 17 January 2011, revised manuscript received 13 June 2011

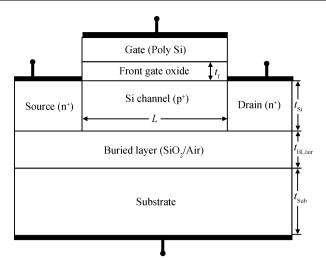

Fig. 1. Generalized SOI/SON MOSFET layered structure.

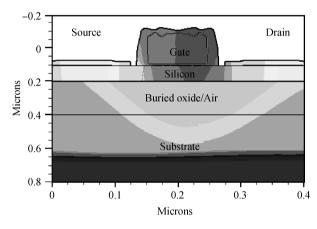

Fig. 2. Generalized SOI/SON MOSFET structure simulated with AT-LAS.

sons for SCE modification.

In this work, a generalized 2D analytical threshold voltage model based on the Poisson's equation solution has been developed for a uniformly doped SOI/SON MOSFET. The effects of the fringing field, substrate bias and junction induced 2D field effects are incorporated in the model. The performance of the two devices is investigated and compared in terms of threshold voltage roll-off and subthreshold slope under different operational and structural parameter variations. The results of the analytical simulation are compared with the results from an ATLAS 2D physics based simulator and they are found to be in good agreement, thereby establishing the validity of our analytical model.

### 2. Analytical modeling

In a short-channel device, potential profiles in and beneath the channel (in the BL) are two-dimensional in nature<sup>[22]</sup>. Threshold voltage can be calculated by solving the 2-D Poisson's equation in the channel<sup>[22–24]</sup>. A generalized layered structure of an SOI/SON MOSFET for analytical model formulation is shown in Fig. 1 and the corresponding SILVACO simulated structure is shown in Fig. 2. Let  $t_f$ ,  $t_{Si}$ ,  $t_{BL/air}$ ,  $t_{sub}$ and L be the thicknesses of gate oxide, silicon channel layer, buried layer/air layer, substrate layer and metallurgical channel length of the device, respectively.

The 2-D Poisson's equation in the two-dimensional channel region of the depleted silicon film body ( $0 \le x \le L, 0 \le y \le t_{Si}$ ) can be written as<sup>[23]</sup>

$$\frac{\partial^2 \phi(x, y)}{\partial x^2} + \frac{\partial^2 \phi(x, y)}{\partial y^2} = \frac{q N_{\rm A}}{\varepsilon_{\rm Si}},\tag{1}$$

where  $\phi(x, y)$  is the 2-D potential profile in the silicon channel,  $N_A$  is the doping concentration of the p-type channel and the substrate and  $\varepsilon_{Si}$  is the permittivity of silicon. By considering a second-order potential approximation, the 2D potential profile in the channel is written as<sup>[16]</sup>

$$\phi(x, y) = A_1(x) + A_2(x)y + A_3(x)y^2.$$

(2)

At the front and back channel interfaces, uniform electric fields are considered and the surface potentials are abbreviated as  $\phi_{sf}(x)$  and  $\phi_{sb}(x)$ , respectively. The four boundary conditions according to the continuity of electrostatic potential and one-dimensional Gauss's law are given as<sup>[22–24]</sup>

$$\phi(x, y) = \phi_{\rm sf}(x)|_{y=0},$$

(3)

$$\phi(x, y) = \phi_{\rm sb}(x)|_{y = t_{\rm Si}}.\tag{4}$$

At y = 0,

$$\frac{\partial \phi(x, y)}{\partial y} = -E_{\rm sf}(x) = -\frac{\varepsilon_{\rm ox}}{\varepsilon_{\rm Si}} \frac{V_{\rm gs}' - \phi_{\rm sf}(x)}{t_{\rm f}}.$$

(5)

At  $y = t_{\rm Si}$ ,

$$\frac{\partial \phi(x, y)}{\partial y} = -E_{\rm sb}(x) = -\frac{\varepsilon_{\rm BL/air}}{\varepsilon_{\rm Si}} \frac{V_{\rm ss}' - \phi_{\rm sb}(x)}{t_{\rm BL/air}},\qquad(6)$$

where  $\varepsilon_{\rm BL/air}$  is the dielectric permittivity of silicon dioxide/air,  $V'_{\rm gs}$  and  $V'_{\rm ss}$  are the effective applied front and back channel voltages. The front and back channel voltages are expressed as  $V'_{\rm gs} = V_{\rm gs} - V_{\rm ffb}$  and  $V'_{\rm ss} = V_{\rm ss} - V_{\rm bfb}$ , where  $V_{\rm ffb}$  and  $V_{\rm bfb}$  are the front and back channel flat band voltages, respectively. The values of the coefficients  $A_1(x)$ ,  $A_2(x)$  and  $A_3(x)$  derived by solving Eqs. (2) and (3)–(6) are given as

$$A_1(x) = \phi_{\rm sf}(x),\tag{7}$$

$$A_2(x) = -\frac{\varepsilon_{\text{ox}}}{\varepsilon_{\text{Si}}} \frac{V'_{\text{gs}} - \phi_{\text{sf}}(x)}{t_{\text{f}}} = -\frac{c_{\text{f}}}{\varepsilon_{\text{Si}}} [V'_{\text{gs}} - \phi_{\text{sf}}(x)], \quad (8)$$

$$A_{3}(x) = \left[ V_{ss}' + V_{gs}' \left( \frac{c_{\rm f}}{c_{\rm BL/air}} + \frac{c_{\rm f}}{c_{\rm BL/air}} \right) -\phi_{\rm sf}(x) \left( 1 + \frac{c_{\rm f}}{c_{\rm BL/air}} + \frac{c_{\rm f}}{c_{\rm BL/air}} \right) \right] \times \left[ t_{\rm Si}^{2} \left( 1 + 2\frac{c_{\rm f}}{c_{\rm BL/air}} \right) \right]^{-1}, \qquad (9)$$

where  $C_{\rm f}$  and  $C_{\rm BL/air}$  are the front and back oxide/air capacitances, respectively. Substituting the values of the coefficients in Eq. (2), we get a second-order differential equation of  $\phi_{\rm sf}(x)$ ,

$$\frac{t_{\rm Si}^2 \left(1 + 2\frac{C_{\rm Si}}{C_{\rm BL/air}}\right)}{1 + \frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}} \frac{d^2 \phi_{\rm sf}(x)}{dx^2} - \phi_{\rm sf}(x) + \frac{\frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}}{1 + \frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}} (V_{\rm gs} - V_{\rm th}) + 2\phi_{\rm F} = 0.$$

(10)

Solving Eq. (10), the long-channel threshold voltage is obtained as

$$V_{\rm th}^{\rm long} = V_{\rm ffb} + \frac{\left(1 + \frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}\right) \times 2\phi_{\rm F}}{\frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}} + \frac{qN_{\rm A}t_{\rm Si}\left(1 + 2\frac{C_{\rm Si}}{C_{\rm BL/air}}\right)}{2C_{\rm Si}\left(\frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}\right)} - \frac{V_{\rm ss}'}{\frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}}, (11)$$

where  $2\phi_{\rm F} = \frac{K_{\rm B}T}{q} \ln \frac{N_{\rm A}}{N_{\rm i}}$  is the Fermi potential in the silicon film. Setting  $\left(\frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}\right) \left(1 + \frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}\right)^{-1} (V_{\rm gs} - V_{\rm th}) + 2\phi_{\rm F} = v'$ and  $t_{\rm Si}^2 \left(1 + 2\frac{C_{\rm Si}}{C_{\rm BL/air}}\right) \left(1 + \frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}\right)^{-1} = \lambda^2$ , Equation (10) becomes:

$$\lambda^2 \frac{d^2 \phi_{\rm sf}(x)}{dx^2} - \phi_{\rm sf}(x) + v' = 0, \tag{12}$$

where  $\lambda$  is the characteristic length associated with the surface potential. Introducing a variable,  $\zeta(x) = \phi_{sf}(x) - v'$ , Equation (12) can be written as

$$\frac{d^2\zeta(x)}{d^2x^2} - \frac{\zeta(x)}{\lambda^2} = 0.$$

(13)

Equations (5) and (6) are valid in the front oxide with the assumption of a strict vertical field. Since a lateral field (from the source and drain, which is generally known as the fringing field) as well as a vertical field due to substrate bias<sup>[22–24]</sup> are present, Eqs. (5) and (6) are not valid in the buried oxide layer. Due to the combined effect of the lateral and vertical fields,  $V_{\rm ss}$  will be modified and the modified field is denoted by  $V_{\rm ss}^{\rm eff}$ . Since the charge in the buried layer is negligible, the 2-D Laplace's equation in the buried layer charge reduces to

$$\frac{\partial^2 \phi(x, y)}{\partial x^2} + \frac{\partial^2 \phi(x, y)}{\partial y^2} = \frac{q N_{\rm B}}{\varepsilon_{\rm BL/air}},$$

$$0 \le x \le L, t_{\rm Si} \le y \le t_{\rm Si} + t_{\rm ox2}.$$

(14)

The relevant boundary conditions are given below:

- 0

$$\phi(0, t_{\rm Si}) = V_{\rm bi},$$

$$\phi(L, t_{\rm Si}) = V_{\rm bi} + V_{\rm ds},$$

$$\phi(x, t_{\rm Si}) = \phi_{\rm sb}(x),$$

$$\phi(x, t_{\rm Si} + t_{\rm box}) = V_{\rm ss} - V_{\rm bfb},$$

where  $V_{\text{bi}} = V_{\text{T}} \ln \frac{N_{\text{sd}} N_{\text{A}}}{n_i^2}$  is the built in potential. Assuming that the two partial derivatives are weakly coupled, we can write

$$\frac{\partial^2 \phi(x, y)}{\partial x^2} \approx -\frac{\partial \phi(x, y)}{\partial y^2} \approx \chi, \tag{15}$$

where  $\chi$  is an empirical parameter that approaches zero as the channel length increases. By integrating Eq. (15) from x = 0 to x = L,  $\chi$  can be expressed as

$$\chi = \frac{2}{L^2} \{ \phi(L, y) - \phi(0, L) - \left[ \frac{d\phi(x, y)}{dx} |_{x=0} \right] L \}$$

=  $\frac{2}{L^2} [k V_{ds} + r E_0 L].$  (16)

where *r* and *k* are analytical fitting constants depending only upon the thickness of the BL/air layer. From the boundary conditions it is evident that both of them are  $\leq 1$  and  $E_0 = -\frac{d\phi(x,y)}{dx}|_{x=0, y=t_{\rm N}}$  is the source of the fringing field.

$\frac{d\phi(x,y)}{dx}|_{x=0,y=t_{Si}}$  is the source of the fringing field. Integrating Eq. (15) from  $y = t_{Si}$  to  $y = t_{Si} + t_{o2}$  and putting in the value of  $\chi$ , we get:

$$\frac{d\phi(x, y)}{dx}|_{x=0, y=t_{\rm Si}} = \frac{1}{t_{\rm BL/air}} \left[ \frac{k V_{\rm ds} + r E_0 L}{L^2} t_{\rm BL/air}^2 + V_{\rm ss} - V_{\rm bfb} - \phi_{\rm sb}(x) \right].$$

(17)

From Eqs. (6) and (17), we get:

$$V_{\rm ss}^{\rm eff} = V_{\rm ss} + \frac{t_{\rm BL/air}^2}{L^2} (k V_{\rm ds} + r E_0 L).$$

(18)

Inserting Eqs. (5) and (6) into Eq. (2), we get the desired relationship between  $\phi_{sf}(x)$  and  $\phi_{sb}(x)$  which is given as

$$\phi_{\rm sb}(x) = \frac{2C_{\rm Si} + C_{\rm f}}{2C_{\rm Si} + C_{\rm BL/air}} \phi_{\rm sf}(x) - \frac{C_{\rm f}}{2C_{\rm Si} + C_{\rm BL/air}} V_{\rm gs}' + \frac{C_{\rm BL/air}}{2C_{\rm Si} + C_{\rm BL/air}} V_{\rm ss}'.$$

(19)

The expression of  $E_0$  can be written as

$$E_{0} = -\frac{d\phi_{sb}(x)}{dx}|_{x=0}$$

$$= -\frac{2C_{Si} + C_{f}}{2C_{Si} + C_{BL/air}} \frac{d\phi_{sf}(x)}{dx}|_{x=0}$$

$$= -\frac{2C_{Si} + C_{f}}{2C_{Si} + C_{BL/air}} \frac{(V_{bi} + V_{ds} - v') - (V_{bi} - v')\cosh\frac{L}{\lambda}}{\lambda\sinh\frac{L}{\lambda}}.$$

(20)

Substituting the value of  $E_0$  in Eq. (18), we get:

$$(V_{\rm ss}^{\rm eff})' = V_{\rm ss} + \frac{t_{\rm BL/air}^2}{L^2} \left\{ k V_{\rm ds} - rL \left[ -\frac{2C_{\rm Si} + C_{\rm f}}{2C_{\rm Si} + C_{\rm BL/air}} \right] \times \frac{(V_{\rm bi} + V_{\rm ds} - v') - (V_{\rm bi} - v')\cosh(L/\lambda)}{\lambda\sinh(L/\lambda)} \right] \right\}.$$

(21)

The effective back gate bias voltage reduces to  $V_{ss}$  for long L and/or thin BL thicknesses i.e.  $t_{BL/air}$ . Consideration of vertical and lateral field penetration through the BL will modify the threshold voltage expression given by Eq. (11) and it can be written as

$$V_{\rm th}^{\rm eff} = V_{\rm ffb} + \frac{1 + \frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm SI}}}{\frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}} \times 2\phi_{\rm F}$$

$$+ \frac{qN_{\rm A}t_{\rm Si}\left(1 + 2\frac{C_{\rm Si}}{C_{\rm BL/air}}\right)}{2C_{\rm Si}\left(\frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}\right)} - \frac{(V_{\rm ss}^{\rm eff})'}{\frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}}, \quad (22)$$

and

$$v' = \frac{1 + \frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}}{\frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}} (V_{\rm gs} - V_{\rm th}^{\rm eff}) + 2\phi_{\rm F}.$$

(23)

Similarly Equation (13) will be transformed into

$$\frac{\mathrm{d}^2\zeta_{\mathrm{eff}}(x)}{\mathrm{d}x^2} - \frac{\zeta_{\mathrm{eff}}(x)}{\lambda^2} = 0. \tag{24}$$

To encounter the lateral field in the channel, Eq. (24) has been solved with the boundary conditions at the source and drain end, which are given as

$$\zeta_{\rm eff}(x)|_{x\,=\,0} = V_{\rm bi} - V_{\rm eff}' = V_1',\tag{25}$$

$$\zeta_{\rm eff}(x)|_{x=L} = V_{\rm bi} + V_{\rm ds} - V_{\rm eff}' = V_1'.$$

(26)

The solution of Eq. (24) can be written as

$$\zeta_{\rm eff}(x) = \frac{V_1' \sinh \frac{L - x}{\lambda} + V_2' \sinh \frac{x}{\lambda}}{\sinh \frac{x}{\lambda}},$$

(27)

and

$$\phi_{\rm sf}(x) = \zeta_{\rm eff}(x) + v'$$

$$= \frac{V_1' \sinh \frac{L - x}{\lambda} + V_2' \sinh \frac{x}{\lambda}}{\sinh \frac{L}{\lambda}} + v'.$$

Using the condition for the minimum surface potential  $\frac{d\phi_{sf}(x)}{dx} = 0^{[23, 24]}$ , the minimum surface potential point is obtained as

$$x = 0.5 \left( L - \lambda \lg \frac{\tanh \frac{L}{2\lambda} - M}{\tanh \frac{L}{2\lambda} + M} \right),$$

where  $M = \frac{V'_2 - V'_1}{V'_2 + V'_1}$

The corresponding minimum front surface potential is obtained as

$$\phi_{\rm sf}(x_{\rm min}) = \frac{V_1' \sinh \frac{L - x_{\rm min}}{\lambda} + V_2' \sinh \frac{x_{\rm min}}{\lambda}}{\sinh \frac{L}{\lambda}} + \upsilon'. \quad (29)$$

The onset of strong inversion occurs when the channel has just enough inversion charges through the application of a specific gate voltage (namely the threshold voltage). This condition happens when the front surface potential is equal to twice the value of the Fermi potential. Putting  $\phi_{sf}(x_{min}) = 2\phi_F$  into Eq. (29), the short channel threshold voltage is obtained as

$$V_{\rm th}^{\rm short} = V_{\rm th}^{\rm eff} + \frac{1}{C_{\rm Si}} \left( \frac{2\phi_{\rm F}}{C_2} - \frac{C_1}{C_3} - 2\phi_{\rm F} \right),$$

(30)

where

$$C_{1} = \frac{V_{\text{bi}}\left(\sinh\frac{L-x_{\min}}{\lambda} + \sinh\frac{x_{\min}}{\lambda}\right) + V_{\text{ds}}\sinh\frac{x_{\min}}{\lambda}}{\sinh\frac{L}{\lambda}},$$

$$C_2 = \frac{\frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}}{1 + \frac{C_{\rm f}}{C_{\rm BL/air}} + \frac{C_{\rm f}}{C_{\rm Si}}}$$

and

$$C_3 = 1 - \frac{\sinh \frac{L - x_{\min}}{\lambda} + \sinh \frac{x_{\min}}{\lambda}}{\sinh \frac{L}{\lambda}},$$

The subthreshold slope, SS =  $[2.3V_T \frac{dV_{gs}}{d\phi_{sf}(x_{min})}]^{-1}$ , can be expressed as

104001-4

(28)

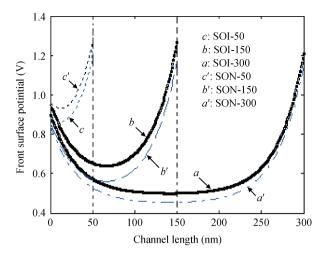

Fig. 3. Variation of the front surface potential along the channel for n-channel SOI/SON MOSFETs with  $V_{ds} = 0.5$  V,  $t_{gox} = 7$  nm,  $t_{Si} =$ 100 nm,  $t_{\text{BL/air}} = 200$  nm,  $N_{\text{A}} = 2 \times 10^{17}$  cm<sup>-3</sup>,  $V_{\text{ss}} = 1$  V.

$$SS = 2.3V_{T} \frac{d\phi_{sf}(x_{min})}{dV_{gs}}$$

$$= 2.3V_{T} \left\{ \frac{a_{2}-1}{a_{2}-a_{1}} \exp \sqrt{A_{1}}x_{min} - \frac{a_{2}-a_{1}-1}{a_{2}-a_{1}} \right.$$

$$\times \exp \sqrt{A_{2}}x_{min} + \left[ K_{1}\sqrt{A_{1}} \exp \sqrt{A_{1}}x_{min} - K_{2}\sqrt{A_{2}} \exp(-\sqrt{A_{2}}x_{min}) \right] \frac{1}{2\sqrt{A_{1}}} \frac{K_{1}}{K_{2}}$$

$$\times \frac{K_{1}\frac{a_{2}-a_{1}-1}{a_{2}-a_{1}} - K_{2}\frac{a_{1}-1}{a_{2}-a_{1}}}{K_{1}^{2}} \log \frac{K_{1}}{K_{2}} \right\}$$

$$\times \frac{\frac{C_{f}}{C_{BL/air}} + \frac{C_{f}}{C_{Si}}}{1 + \frac{C_{f}}{C_{BL/air}} + \frac{C_{f}}{C_{Si}}}, \qquad (31)$$

where

S

$$A_1 = 1/\lambda^2, \ A_2 = \frac{V'_{\text{eff}}}{\lambda^2},$$

$$a_1 = \exp(L\sqrt{A_1}), \ a_2 = \exp(-L\sqrt{A_2}),$$

$$K_1 = V_{\rm bi} + V_{\rm eff}' - \frac{V_{\rm bi} + V_{\rm ds} + V_{\rm eff}' - (V_{\rm bi} + V_{\rm eff}')a_1}{a_2 - a_1}$$

and

$$K_2 = V_{\rm bi} + V_{\rm ds} + V_{\rm eff}' - \frac{V_{\rm bi} - V_{\rm eff}' a_1}{a_2 - a_1}.$$

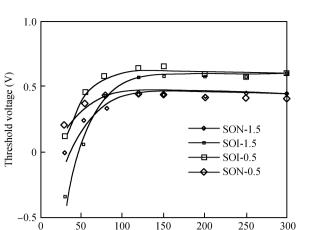

Fig. 4. Variation of threshold voltage with channel length for SOI/SON MOSFETs for  $V_{ds} = 0.5$  V and  $V_{ds} = 1.5$  V. Other parameters are the same as in Fig. 3 and symbols indicate the ATLAS simulated data.

150

Channel length (nm)

200

250

300

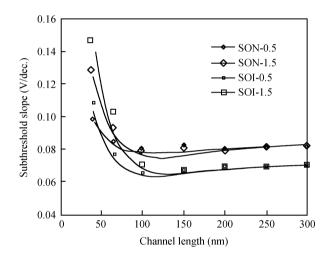

100

Fig. 5. Variation of subthreshold slope with channel length for SOI/SON MOSFETs for different Vds: 0.5 and 1.5 V. Other parameters are the same as in Fig. 3 and symbols indicate the ATLAS simulated data.

### 3. Results and discussion

0

In a bulk MOSFET, the threshold voltage is derived only from the front interface surface potential  $\phi_{sf}$ , neglecting the effect of  $\phi_{bf}$ . However, in a short channel SOI-SON structure,  $\phi_{\rm sf}$  will be strongly influenced by the back interface potential  $\phi_{\rm bf}$ . The lowest dielectric constant material (air) in the box region causes significant modification in  $\phi_{\rm bf}$ , which affects  $\phi_{\rm sf}$ . This modification in  $\phi_{bf}$  is responsible for the considerable performance improvement in the SON over an SOI structure. Neglecting quantum effect, bandgap narrowing and other secondand third- order effects, the threshold voltage performance of an SOI and an SON structure are simulated with a 2D analytical model and the results are verified with the results of the ATLAS physics based simulator.

The front interface surface potentials at different channel positions for three different channel lengths (50, 150 and 300 nm) of a uniformly doped SOI and SON MOSFET are shown

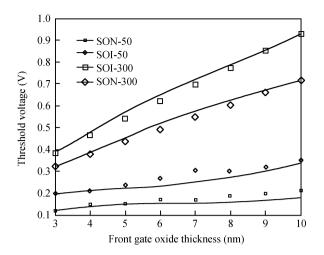

Fig. 6. Threshold voltage variation with  $t_{\rm f}$  channel lengths of 100 nm and 300 nm.  $V_{\rm ds} = 1$  V and other parameters and symbols are the same as in Fig. 3.

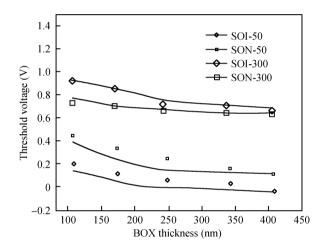

Fig. 7. Threshold voltage variation with  $t_{BL/air}$  for channel lengths of 100 nm and 300 nm.  $V_{ds} = 1$  V and the other parameters and symbols are the same as in Fig. 3.

in Fig. 3. As expected, the potential variation is almost symmetric about the midpoint of the channel for a long channel length (300 nm) for both the SOI and the SON. The minimum value of the surface potential is less for the SON at comparatively higher channel lengths, 300 and 150 nm, but for a lower channel length (50 nm), the SOI has a lower surface potential minima. The minimum value of the surface potential shifts upward as the channel length reduces because of the SCEs and this upward shift of the minimum surface potential is less for the SON structure as compared to the SOI structure. The decrease in channel length not only shifts the minimum surface potential upward but also causes a drift towards the source side because of DIBL or 2DCS effects.

Variation of threshold voltage and subthreshold slope with channel length for SOI and SON MOSFET are shown in Figs. 4 and 5, respectively. Threshold voltage roll-off and subthreshold slope are found to be less in the SON due to a reduced potential coupling ratio ( $P_{CR} = \phi_{sf}/\phi_{bf}$ ) in SON. The higher drain bias initiates higher SCEs, which cause higher threshold voltage roll-off and a higher subthreshold slope.

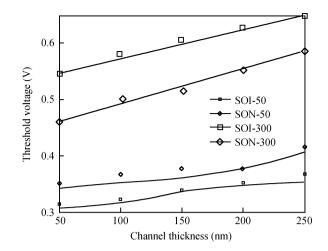

Fig. 8. Threshold voltage variation with  $t_{Si}$  for channel lengths of 100 nm and 300 nm, respectively.  $V_{ds} = 1$  V and the other parameters and symbols are the same as in Fig. 3.

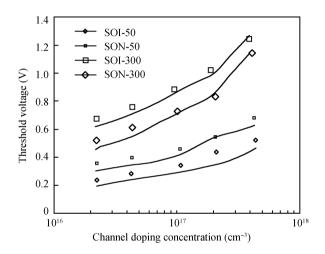

Fig. 9. Threshold voltage variation with  $N_A$  for channel lengths of 100 nm and 300 nm, respectively.  $V_{ds} = 1$  V and the other parameters and symbols are the same as in Fig. 3.

Variation of threshold voltage with front gate oxide and BL/air thicknesses are plotted in Figs. 6 and 7, respectively. The threshold voltage increases with an increase in  $t_f$  for both the short- and long-channel devices due to the reduced control of the front gate voltage over the channel. For the short-channel length device,  $\phi_{sf}$  is strongly influenced by  $\phi_{bf}$ , as a result the rate of increase of the threshold voltage with  $t_f$  is less as compared to the long-channel length device. With increasing buried layer thickness, the influence of  $\phi_{bf}$  reduces and as a result the threshold voltage also reduces.

Threshold voltage variation with silicon channel thickness and channel doping concentration are plotted in Figs. 8 and 9, respectively. The threshold voltage increases with channel thickness because the device approaches a bulk value and a higher gate voltage is required to create inversion. The nature of the threshold voltage slope can be explained with different  $P_{CR}$  values at 50 nm and 300 nm channel lengths, respectively. The results of the analytical simulation are compared with simulated data from ATLAS and they are found to be in good agreement.

### 4. Conclusion

A 2D Poisson's solution based generalized threshold voltage model for SOI/SON MOSFETs has been developed and analytical expressions for threshold voltage and sub-threshold slope have been derived. Different short-channel field effects like fringing field, junction induced lateral field and substrate field are incorporated in the analytical threshold voltage model. The performance of the two devices is studied and compared in terms of the threshold voltage roll-off and subthreshold slope, which are very important issues relating to the performance analysis of a short-channel MOSFET. Effects of the variation of different parameters, such as channel length, channel thickness, gate oxide thickness, buried layer thickness and channel doping concentration, on the threshold voltage are also investigated and analyzed to understand the comparative performance of the two structures. The short-channel SON structure shows less threshold voltage roll-off and less subthreshold slope compared to the short-channel SOI structure. The present analysis shows that SON MOSFET technology is able to offer devices with scalability and enhanced performance due to higher immunity against SCEs. SON structures provides scope for further miniaturization of devices for the next generation of CMOS structures.

## Acknowledgement

Sanjoy Deb thankfully acknowledges the financial support obtained from the School of Material Science and Nanotechnology, Jadavpur University, in the form of a UGC Fellowship.

#### References

- The International Technology Roadmap for Semiconductor, Emerging Research Devices, 2009

- [2] Colinge J P. Silicon on insulator technology: materials to VLSI. 2nd ed. Norwell, MA: Kluwer: Kluwer Academic Publishers, 1997

- [3] Current M I, Bedell S W, Malik I J, et al. What is the future of sub-100 nm CMOS: ultrashallow junctions or ultrathin SOI. Solid State Technol, 2000, 43: 23

- [4] Ernst T, Cristoloveanu S. Buried oxide fringing capacitance: a new physical model and its implication on SOI device scaling and architecture. Proc IEEE Int SOI Conf, 1999: 38

- [5] Ernst T, Tinella C, Raynaud C, et al. Fringing fields in sub-0.1 μm fully depleted SOI MOSFETs: optimization of the device architecture. Solid-State Electron, 2002, 46: 373

- [6] Koh R. Buried layer engineering to reduce the drain-induced barrier lowering of sub-0.05 μm SOI-MOSFET. Jpn J Appl Phys, 1999, 38: 2294

- [7] Cristoloveanu S, Li S S. Electrical characterization of SOI de-

vices. Norwell, MA: Kluwer, 1995

- [8] Colinge J P. Silicon-on-insulator technology: materials to VLSI. Amsterdam: Kluwer Academic Publishers, 1991

- [9] Shahidi G G. SOI technology for the GHz era. IBM J RES & DEV, 2002, 46: 2

- [10] Balestra F, Benachir M, Brini J, et al. Analytical models of subthreshold swing and threshold voltage for thin and ultrathin-film SOI MOSFETs. IEEE Trans Electron Devices, 1990, 37: 2303

- [11] Jurczak M, Skotnicki T, Paoli M, et al. Silicon-on-nothing (SON)—an innovative process for advanced CMOS. IEEE Trans Electron Devices, 2000, 47(11): 2179

- [12] Sato T, Nii H, Hatano M, et al. Fabrication of SON (silicon on nothing)-MOSFET and its ULSI applications. IEIC Technical Report, 2002, 102(178): 99

- [13] Kilchytska V, Chung T M, Olbrechts B, et al. Electrical characterization of true silicon-on-nothing MOSFETs fabricated by Si layer transfer over a pre-etched cavity. Solid-State Electron, 2007, 51: 1238

- [14] Monfray S, Skotnicki T, Beranger C F, et al. Emerging silicon-onnothing (SON) devices technology. Solid-State Electron, 2004, 48: 887

- [15] Monfray S, Boeuf F, Coronel P, et al. Silicon-on-nothing (SON) applications for low power technologies. IEEE International Conference on Integrated Circuit Design and Technology and Tutorial, 2008: 1

- [16] Young K K. Short-channel effect in fully depleted SOI MOS-FET's. IEEE Trans Electron Devices, 1989, 36(2): 399

- [17] Yeh P C, Fossum J G. Physical subthreshold MOSFET modeling applied to viable design of deep-submicrometer fully depleted SOI low-voltage CMOS technology. IEEE Trans Electron Devices, 1995, 42(99): 1605

- [18] Reddy G V, Jagadesh K M. A new dual-material double-gate (DMDG) nanoscale SOI MOSFET-two-dimensional analytical modeling and simulation. IEEE Trans Electron Devices, 2005, 4(2): 260

- [19] Liu Z H, Hu C, Huang J H, et al. Threshold voltage model for deep-submicrometer MOSFET's. IEEE Trans Electron Devices, 1993, 40(1): 86

- [20] Dhanaselvam P S, Balamurugan N B, Vanitha P, et al. Two dimensional analytical modeling of a nanoscale dual material gate MOSFETs. International Journal of Advanced Science and Technology, 2010, 18: 49

- [21] Pretet J, Monfray S, Cristoloveanu S, et al. Silicon-on-nothing MOSFETs: performance, short-channel effects and backgate coupling. IEEE Trans Electron Devices, 2004, 51(2): 240

- [22] Majumdar A, Ren Z, Koester S J, et al. Undoped-body extremely thin SOI MOSFETs with back gates. IEEE Trans Electron Devices, 2009, 56(10): 2270

- [23] Suzuki K, Pidin S. Short-channel single-gate SOI MOSFET model. IEEE Trans Electron Devices, 2003, 50(5): 1297

- [24] Zhang G, Shao Z, Zhou K. Threshold voltage model of shortchannel FD-SOI MOSFETs with vertical Gaussian profile. IEEE Trans Electron Devices, 2008, 55(3): 803