# Effect of a gate buffer layer on the performance of a 4H-SiC Schottky barrier field-effect transistor\*

Zhang Xianjun(张现军)<sup>†</sup>, Yang Yintang(杨银堂), Chai Changchun(柴常春), Duan Baoxing(段宝兴), Song Kun(宋坤), and Chen Bin(陈斌)

Key Laboratory of Wide Band-Gap Semiconductor Materials and Devices of the Ministry of Education, School of Microelectronics, Xidian University, Xi'an 710071, China

Abstract: A lower doped layer is inserted between the gate and channel layer and its effect on the performance of a 4H-SiC Schottky barrier field-effect transistor (MESFET) is investigated. The dependences of the drain current and small signal parameters on this inserted gate-buffer layer are obtained by solving one-dimensional (1-D) and two-dimensional (2-D) Poisson's equations. The drain current and small signal parameters of the 4H-SiC MESFET with a gate-buffer layer thickness of 0.15  $\mu$ m are calculated and the breakdown characteristics are simulated. The results show that the current is increased by increasing the thickness of the gate-buffer layer; the breakdown voltage is 160 V, compared with 125 V for the conventional 4H-SiC MESFET; the cutoff frequency is 27 GHz, which is higher than 20 GHz of the conventional structure due to the lower doped gate-buffer layer.

Key words:4H-SiC;Schottky barrier field-effect transistor;Poisson's equationDOI:10.1088/1674-4926/33/7/074003PACC:7330;7340C;7340L

## 1. Introduction

Silicon carbide (SiC) MESFETs are very attractive for high power microwave devices due to the combination of the high electron velocity, high breakdown strength, and high thermal conductivity of SiC<sup>[1]</sup>. With the recent progress in SiC epitaxial material and device processes, several improved SiC MESFET structures have been reported<sup>[2-4]</sup>. However, the improvement of the power density of the above mentioned structures is very limited because there is a potential tradeoff between the further increment of drain current and breakdown voltage: a large drain current requires a large channel doping product and thickness; nevertheless, this will reduce breakdown voltage. Similarly, to increase the operation frequency, the gate length should be reduced; however, this will also degrade the performance of the devices and circuits<sup>[5, 6]</sup>.

In this paper, the performance of 4H-SiC MESFETs are improved by inserting a lower doped gate-buffer layer between the gate and the channel layer, instead of increasing the doping concentration of the channel layer and decreasing the gate length. The analytical models that describe the effect of the inserted gate-buffer layer on the performance of the device are obtained by solving one-dimensional (1-D) and twodimensional (2-D) Poisson's equations. Based on the analytical models, the drain current and small signal parameters are calculated and analyzed for a 4H-SiC MESFET with a gate-buffer layer of 0.15  $\mu$ m. Meanwhile, the breakdown characteristics for a 4H-SiC MESFET of the same size are simulated. The results show that not only power but also frequency performance are improved compared with the conventional structure due to the inserted lower doped gate-buffer layer.

# 2. Analytical models

In order to describe the device operation, the channel current in the channel can be expressed as

$$I_{\rm C} = qWn(x)\mu(E)E(x)[a-h(x)],\tag{1}$$

where q is the magnitude of the electronic charge, W the channel width, a the channel layer thickness, E(x) the lateral electric field strength, and n(x) the electron concentration, x away from the source. n(x) is equal to  $N_D$ , the doping concentration of the channel. h(x) is the thickness of the depletion layer in the channel layer and obtained by solving the 1-D Poisson's equation.

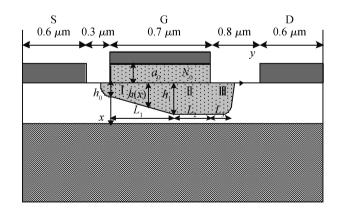

Fig. 1. Schematic diagram of the SiC MESFET with a buffer layer for the saturation regime.

<sup>\*</sup> Project supported by the Pre-Research Foundation from the National Ministries and Commissions of China (No. 51308030201).

<sup>†</sup> Corresponding author. Email: xianjun\_zhang@yahoo.com.cn

Received 13 December 2011, revised manuscript received 29 February 2012

$$h(x) = a_0 \left( 1 - \frac{N_0}{N_D} + \frac{V(x) + V_G + V_{bi}}{\frac{qN_D}{2\varepsilon}a_0^2} \right)^{1/2} - a_0, \quad (2)$$

where  $N_0$  is the uniform doping concentration of the gatebuffer layer, which is smaller than that of the channel  $N_D$ .  $a_0$ is the gate-buffer layer thickness, and  $\varepsilon$  the dielectric constant. V(x) is the potential at the point x away from the source,  $V_G$ the gate bias, and  $V_{bi}$  the build-in voltage.

When the drain voltage is low, the electric field in the channel is less than the saturation field  $E_s$  and only region I exists. Based on the integration over the channel length L, the channel current is obtained as

$$I_{\rm C}(V_{\rm G}, V_{\rm D}) = I_{\rm P} \times \frac{3(u_{\rm d}^2 - u_0^2) - 2(u_{\rm d}^3 - u_0^3) - \frac{3a_0}{a}[(u_{\rm d}^2 - u_0^2) - 2(u_{\rm d} - u_0)]}{1 + Z(u_{\rm d}^2 - u_0^2) + Z\frac{2a_0}{a}(u_{\rm d} - u_0)},$$

(3)

where  $u_0(u_d)$  is the depletion layer width  $h_0(h_d)$  at the source (drain) end of the channel normalized to the epilayer channel layer thickness *a*.  $I_P$  and *Z* are constants.

With the drain bias increasing gradually, the lateral electric field increases and the electron velocity rises toward its saturation value. At enough high drain bias, the channel is in a saturated state, and can be divided into three regions, as shown in Fig. 1. In region I, with its length of  $L_1$  and nearer to the source under the gate, the electric field is low and the electron velocity is less than the saturation velocity  $(v_s)$ . The saturation region below the gate and the saturation region between the gate and the drain are labeled as regions II and III, respectively. The saturation channel current is

$$I_{\rm csat} = q N_{\rm D} W a v_{\rm s} (1 - u_1), \tag{4}$$

where  $u_1$  is the normalized depletion layer thickness at the point where the electron reaches saturation velocity.

$$u_{1}(V_{\rm G}, V_{\rm D}) = \frac{h_{1}}{a}$$

$$= \sqrt{\left(1 - \frac{N_{0}}{N_{\rm D}}\right)\frac{a_{0}^{2}}{a^{2}} + \frac{V(L_{1}) + V_{\rm G} + V_{\rm bi}}{V_{\rm p}} - \frac{a_{0}}{a},$$

(5)

where  $h_1$  is the depletion layer thickness at the point where the electron reaches saturation velocity,  $V(L_1)$  is the potential difference between the source and the point at  $x = L_1$ , where saturation velocity  $v(L_1) = v_s$ .  $V_P$  is a constant.

To obtain the saturation current in the channel, other equations involving  $u_1$  or  $L_1$  are required, which can be found by solving the 2-D Poisson's equation.

The potential drop across regions II and III achieved by solving the 2-D Poisson's equation is

$$V(L + L_3) - V(L_1) = \left[\frac{2(au_1 + a_0)}{\pi} + \frac{L_3}{3}\right] E_s$$

$$\times \sinh \frac{\pi L_2}{2(au_1 + a_0)} \exp \frac{-\pi L_3}{2(au_1 + a_0)}$$

$$+ \frac{E_s L_3}{3} \left[2 \exp \frac{\pi L_2}{2(au_1 + a_0)} + 1\right].$$

(6)

The equation involving  $L_3$  is

$$L_{3}^{2} \Biggl\{ \frac{q N_{D} a u_{1}}{\varepsilon} - E_{s} \exp \frac{\pi L_{2}}{2(a u_{1} + a_{0})} + \frac{E_{s}}{\eta} \sinh \frac{\pi L_{2}}{2(a u_{1} + a_{0})} \left[ 1 + \tan \frac{\pi a_{0}}{2(a u_{1} + a_{0})} \right] \Biggr\}$$

$$= (a u_{1})^{2} E_{s} \Biggl[ \exp \frac{\pi L_{2}}{2(a u_{1} + a_{0})} - 1 - \sinh \frac{\pi L_{2}}{2(a u_{1} + a_{0})} \exp \frac{-\pi L_{3}}{2(a u_{1} + a_{0})} \Biggr], \quad (7)$$

where

$$\eta = \tan \frac{\pi a_0}{2(au_1 + a_0)} \cos \frac{\pi a u_1}{2(au_1 + a_0)} + \sin \frac{\pi a u_1}{2(au_1 + a_0)},$$

$$V(L+L_3)=V_{\rm D}-I_{\rm C}R_{\rm D}.$$

From the analysis above, the drain current can be achieved when the structure parameters  $(L, W, a, a_0, N_D, N_0)$  and bias voltage  $(V_D, V_G)$  are given.

To evaluate the high frequency performance conveniently, it is important to describe the small signal parameters analytically.

Based on Eq. (4), the drain conductance for the saturation regime is obtained as

$$g_{\rm ds} = -\frac{3\gamma I_{\rm P}}{2Zm_{L_1}V_{\rm P}}f,\tag{8}$$

where

f

$$\begin{aligned} & -^{-1} = 1 + \frac{1}{2m_{L_1}V_{\rm P}} \left[ \frac{2E_{\rm S}a}{\pi} \sinh \frac{\pi \left(L - L_1\right)}{2\left(au_1 + a_0\right)} \right. \\ & \left. - \frac{E_{\rm S}a\left(L - L_1\right)}{\left(au_1 + a_0\right)} \cosh \frac{\pi \left(L - L_1\right)}{2\left(au_1 + a_0\right)} \right] \\ & \left. - \frac{E_{\rm S}LZ}{2m_{L_1}V_{\rm P}} \cosh \frac{\pi \left(L - L_1\right)}{2\left(au_1 + a_0\right)} \right. \\ & \times \left\{ \left[ \frac{2u_1(1 - \gamma)}{\gamma} + \frac{\left(u_1^2 - u_0^2\right) - \frac{2}{3}\left(u_1^3 - u_0^3\right)}{\gamma(1 - u_1)^2} \right] \right. \\ & \left. - \frac{a_0}{\gamma a} \left[ \frac{\left(u_1^2 - u_0^2\right) - \left(u_1 - u_0\right)}{\left(1 - u_1\right)^2} - 2\left(1 - \gamma\right) \right] \right\}, \end{aligned}$$

$$m_{L_1}=u_1+\frac{a_0}{a}.$$

The expression of transconductance for the saturation regime is

$$g_{\rm ms} = -\frac{3\gamma I_{\rm P}}{2Zm_{L_1}V_{\rm P}}(k+1),$$

(9)

where

$$\begin{split} h &= -\frac{1}{2m_{L_1}V_{\rm P}} \left[ \frac{2E_{\rm S}a}{\pi} \sinh \frac{\pi \left(L - L_1\right)}{2\left(au_1 + a_0\right)} - \frac{E_{\rm S}a \left(L - L_1\right)}{au_1 + a_0} \right] \\ &\times \cosh \frac{\pi \left(L - L_1\right)}{2\left(au_1 + a_0\right)} \right] + \frac{E_{\rm S}LZ}{2m_{L_1}V_{\rm P}} \cosh \frac{\pi \left(L - L_1\right)}{2\left(au_1 + a_0\right)} \\ &\times \left\{ \left[ \frac{2u_1(1 - \gamma)}{\gamma} + \frac{\left(u_1^2 - u_0^2\right) - \frac{2}{3}\left(u_1^3 - u_0^3\right)}{\gamma\left(1 - u_1\right)^2} \right] \right] \\ &- \frac{a_0}{\gamma a} \left[ \frac{\left(u_1^2 - u_0^2\right) - \left(u_1 - u_0\right)}{\left(1 - u_1\right)^2} - 2\left(1 - \gamma\right) \right] \right\} \\ &- \frac{u_0 E_{\rm S}LZ}{m_0 V_{\rm P}} \cosh \frac{\pi \left(L - L_1\right)}{2\left(au_1 + a_0\right)} \\ &\times \left[ \frac{1 - u_0}{\gamma\left(1 - u_1\right)} - 1 \right] \left( 1 + \frac{a_0}{au_0} \right), \\ &k = fh. \end{split}$$

To find the gate–source capacitance, the magnitude of the charge in the depletion layer under the gate is needed. This can be derived from the potential distribution in the depletion layer. So, the expression of the gate–source capacitance is given as

$$C_{\rm gs} = C_{\rm g1} + C_{\rm g2} + C_{\rm g3}, \tag{10}$$

where

$$C_{\rm g1} = \frac{4\varepsilon W L V_{\rm P} I_{\rm P}}{a I D} \left( C_{\rm g11} + C_{\rm g12} \right),$$

$$C_{g11} = -\frac{g_{m}}{I_{D}} \left[ \left( 1 - \frac{a_{0}}{a} \right) \left( u_{1}^{3} - u_{0}^{3} \right) - \frac{3}{4} \left( u_{1}^{4} - u_{0}^{4} \right) + \frac{3a_{0}}{a} \left( u_{1}^{2} - u_{0}^{2} \right) \right],$$

$$C_{g12} = \frac{3u_1}{2m_{L_1}V_P} \left(u_1 + \frac{a_0}{a}\right) \left(1 - u_1 - \frac{ZI_D}{3I_P}\right) (k+1) - \frac{3u_0}{2m_0V_P} \left(u_0 + \frac{a_0}{a}\right) \left(1 - u_0 - \frac{ZI_D}{3I_P}\right),$$

$$C_{g2} = \frac{2\varepsilon WLZu_1}{a} \left\{ \frac{g}{2Zm_{L_1}u_1} \left(k+1\right) + \frac{u_0}{m_0} \right. \\ \left. \times \left[ \frac{u_1 - u_0}{\gamma \left(1 - u_1\right)} + \frac{1 - \gamma}{\gamma} \right] \left(1 + \frac{a_0}{au_0}\right) \right\}$$

$$C_{\rm g3} = -\varepsilon E_{\rm s} Wa \left( C_{\rm g31} + C_{\rm g32} \right)$$

$$C_{g31} = \frac{k+1}{2m_{L_1}V_P} \left\{ 1 - \cosh\frac{\pi \left(L - L_1\right)}{2\left(au_1 + a_0\right)} - \frac{\pi \left(1 - u_1\right)}{2\left(au_1 + a_0\right)} \right. \\ \times \sinh\frac{\pi \left(L - L_1\right)}{2\left(au_1 + a_0\right)} \left[ \frac{a\left(L - L_1\right)}{au_1 + a_0} - \frac{Lg - L + L_1}{u_1} \right] \right\},$$

$$C_{g32} = \frac{\pi u_0 LZ \left(1 - u_1\right)}{2m_0 V_P \left(au_1 + a_0\right)} \sinh\frac{\pi \left(L - L_1\right)}{2\left(au_1 + a_0\right)} \\ \times \left[ \frac{1 - u_0}{\gamma \left(1 - u_1\right)} - 1 \right] \left( 1 + \frac{a_0}{au_0} \right),$$

$$= 1 - \frac{L_1}{L}$$

$$- Zu_1 \left\{ \left[ \frac{2u_1(1-\gamma)}{\gamma} + \frac{(u_1^2 - u_0^2) - \frac{2}{3}(u_1^3 - u_0^3)}{\gamma(1-u_1)^2} \right] - \frac{a_0}{\gamma a} \left[ \frac{(u_1^2 - u_0^2) - (u_1 - u_0)}{(1-u_1)^2} - 2(1-\gamma) \right] \right\}.$$

So, the cutoff frequency can be obtained by

$$f_{\rm T} = \frac{g_{\rm m}}{2\pi C_{\rm g}}.\tag{11}$$

#### 3. Results and discussion

g

In our proposed SiC MESFET structure, the gate length is 0.7  $\mu$ m. Meanwhile, the thickness and doping concentration are 0.26  $\mu$ m and 1.7 × 10<sup>17</sup> cm<sup>-3</sup> for the channel layer, and 0.15  $\mu$ m and 1 × 10<sup>15</sup> cm<sup>-3</sup> for the gate-buffer layer between the gate and channel layer.

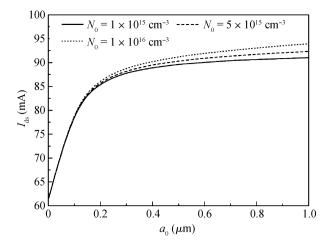

Figure 2 shows the effect of the gate-buffer layer on the current in the channel. It reveals that the thicker the gate-buffer layer is, the larger the drain current is. This is because the channel width is increased owing to the decrease of the depletion layer thickness in the channel when the gate-buffer layer doping concentration and thickness is increased. It is also shown in Fig. 2 that when the gate-buffer layer is increased sufficiently, the drain currents increase slowly. In fact, when the gate-buffer layer in the channel layer thickness of the depleted layer in the channel layer decreases more and more slowly. So, the thickness of the conduction channel and the drain currents increase more and more slowly with increasing the thickness of the gate-buffer layer.

It is one of the most important applications to act as an amplifier for the power microwave 4H-SiC MESFET. If the maximum output drain currents are not large enough, when an alternating-current (AC) large signal is input, the modulation range of the input AC large signal will be limited and thus nonlinear distortion occurs, i.e., cutoff distortion or saturation distortion. Because our proposed structure has larger maximum

Fig. 2. Dependence of the drain current on the gate-buffer layer for  $N_0 = 1 \times 10^{15} \text{ cm}^{-3}$ ,  $N_0 = 5 \times 10^{15} \text{ cm}^{-3}$  and  $N_0 = 1 \times 10^{16} \text{ cm}^{-3}$ .  $V_{gs} = 0 \text{ V}$ ,  $V_{ds} = 5 \text{ V}$ .

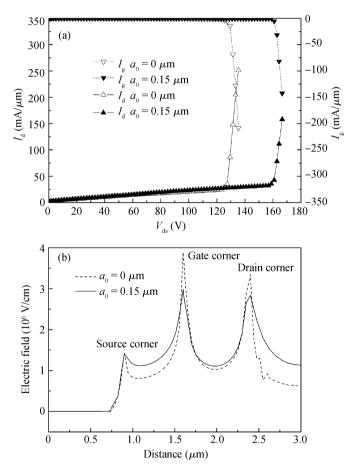

Fig. 3. The simulated breakdown characteristics. (a) Drain current and gate leakage current for  $a_0 = 0 \ \mu m$  (open) and  $a_0 = 0.15 \ \mu m$  (filled). (b) Electric field for  $a_0 = 0 \ \mu m$  (dash) and  $a_0 = 0.15 \ \mu m$  (solid).

output drain currents than that of the conventional structure, it is more applicable for the AC large signal application.

Figure 3 is the simulated breakdown characteristics for the two structures using the ISE simulator<sup>[7]</sup>. It can be seen that the breakdown voltage ( $V_b$ ) for  $a_0 = 0.15 \,\mu\text{m}$  is 160 V, which is higher than 125 V for  $a_0 = 0 \,\mu\text{m}$ . Figure 3(b) plots the corresponding electric field distribution. It shows that the break-

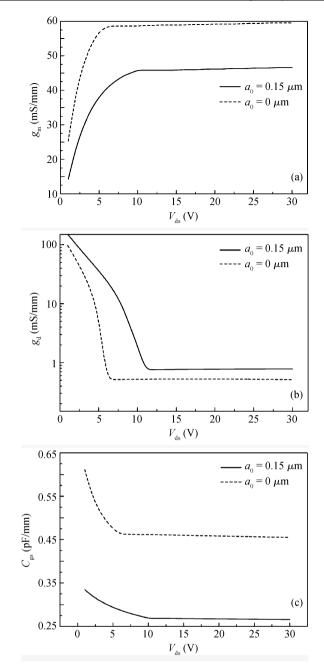

Fig. 4. Transconductance, output conductance, and gate–source capacitance versus drain voltage at  $V_{gs} = 0$  V for  $a_0 = 0 \ \mu m$  (dash) and  $a_0 = 0.15 \ \mu m$  (solid).

down happened at the gate corner near to the drain side due to the electric field crowding here in both structures. However, the electric field peak is significantly lowered at the gate corner while raised at the drain corner, i.e., the surface electric field is more uniform, owing to the inserted lower doped gate-buffer layer, when compared with that of the conventional SiC MES-FET. The reason for the suppression of the electric field at the gate corner is similar to that for the weakened surface electric field caused by the lightly doped drain (LDD) in a MOSFET<sup>[8]</sup>.

For simplicity, the gate-source and gate-drain region channel resistances, as well as the depletion region III between the gate and drain are omitted during the calculation of small signal parameters. Figure 4 shows the transconductance, out-

| Table 1. The calculated small signal parameters at $V_{gs} = 0$ V and $V_{ds} = 10$ V. |                     |                     |                            |                   |

|----------------------------------------------------------------------------------------|---------------------|---------------------|----------------------------|-------------------|

| Parameter                                                                              | $g_{\rm m}$ (mS/mm) | $g_{\rm d}$ (mS/mm) | $C_{\rm gs}~({\rm pF/mm})$ | $f_{\rm T}$ (GHz) |

| $a_0 = 0 \ \mu \mathrm{m}$                                                             | 58.58               | 0.52                | 0.46                       | 20                |

| $a_0 = 0.15 \ \mu m$                                                                   | 45.78               | 1.92                | 0.27                       | 27                |

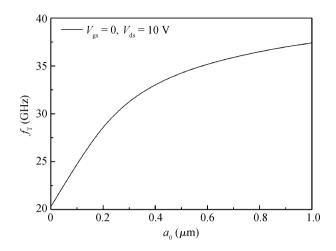

Fig. 5. Variation of the cutoff frequency  $f_{\rm T}$  with the gate-buffer layer thickness  $a_0$ .

put conductance, and gate-source capacitance as a function of the drain voltage at  $V_{gs} = 0$  V. It can be seen that they are independent of the drain voltage in the saturation region. At the same drain voltage, compared with the conventional structure ( $a_0 = 0 \ \mu m$ ), the transconductance ( $g_m$ ) and gate–source capacitance  $(C_{gs})$  are decreased, while the drain conductance  $(g_d)$  is increased because there is a lower doped gate-buffer layer and the total depletion layer thickness under the gate is increased but the part in the channel is decreased. Figure 5 plots the effect of the gate-buffer layer thickness  $a_0$  on the cutoff frequency  $(f_{\rm T})$ . It reveals that the cutoff frequency is increased with increasing the gate-buffer layer thickness. However, when the thickness of the buffer layer is large enough, the cutoff frequency rises more and more slowly. In view of the degradation of the transconductance, the gate-buffer layer thickness should not be too large. Table 1 lists the calculated small signal parameters at  $V_{\rm gs} = 0$  V and  $V_{\rm ds} = 10$  V. When the gate-buffer layer thickness  $a_0$  is 0.15  $\mu$ m, the calculated cutoff frequency is 27 GHz, which is higher than 20 GHz for the conventional structure because the gate-source capacitance is more significantly decreased than the transconductance, as can be seen in Table 1.

#### 4. Conclusion

In summary, a lower doped gate-buffer layer is inserted between the gate and the active channel layer and its effects on the direct-current (DC) and AC characteristics of the 4H-SiC MESFET are investigated. The analytical models which describe the dependence of the drain current and small signal parameters on this gate-buffer layer are derived by solving 1-D and 2-D Poisson's equations. The DC and AC parameters of the 4H-SiC MESFET with a buffer-layer thickness of 0.15  $\mu$ m are calculated or simulated. The results reveal that the drain current, breakdown voltage, and cutoff frequency are all improved when compared with those of the conventional structure due to the lower doped gate-buffer layer. The results achieved in this paper will be helpful for research on power microwave semiconductor devices.

### References

- Sriram S, Hagleitner H, Namishia D, et al. High-gain SiC MES-FETs using source-connected field plates. IEEE Electron Device Lett, 2009, 30(9): 952

- [2] Chen G, Qin Y, Bai S, et al. Microwave power and simulation of S-band SiC MESFETs. Solid-State Electron, 2010, 54(4): 353

- [3] Zhang J, Yi Y, Zhou C, et al. High breakdown voltage 4H-SiC MESFETs with floating metal strips. Microelectron Eng, 2008, 85(1): 89

- [4] Zhang J, Luo X, Li Z, et al. Improved double-recessed 4H-SiC MESFETs structure with recessed source/drain drift region. Microelectron Eng, 2007, 84(12): 2888

- [5] Zhu C L, Rusli, Tin C C, et al. Improved performance of SiC MESFETs using double-recessed structure. Microelectron Eng, 2006, 83(1): 92

- [6] Zhu C L, Rusli, Almira J, et al. Physical simulation of draininduced barrier lowering effect in SiC MESFETs. Mater Sci Forum, 2005, 483–485: 849

- [7] Integrated Systems Engineering, manual for DESSIS, ISE TCAD Release 10.0, 2004

- [8] Sze S M. Physics of semiconductor devices. New York: Wiley, 1981

- Zhu C L, Rusli, Tin C C, et al. A three-region analytical model for short-channel SiC MESFETs. Microelectron Eng, 2006, 83(1): 96