2003年5月

#### CHINESE JOURNAL OF SEMICONDUCTORS

# 亚 100nm 多栅 MOSFET 的三维模拟\*

## 夏志良 刘晓彦 刘恩峰 韩汝琦

(北京大学微电子所,北京 100871)

摘要:使用三维模拟软件对具有 FINFET 的多栅结构(主要是双栅和三栅)进行了模拟.对比了双栅和三栅的 I-V 特性.发现三栅的特性要优于双栅;减小 FIN 宽度(即两个侧栅之间的距离),双栅和三栅结构特性之间的差距变小.

关键词:双栅 MOSFET; 阈值电压; FINFET; 三维模拟; 短沟效应

**EEACC:** 2530F

中图分类号: TN322+.8

文献标识码: A

文章编号: 0253-4177(2003)S0-0140-04

#### 1 引言

在过去二十多年中,为了提高集成度和电路的 性能, MOS 晶体管的尺寸迅速缩小. 目前 MOS 器 件尺寸已经缩小到超深亚微米,而研究水平则已进 入亚 100nm,对于超深亚微米的 MOSFET 短沟效 应越来越显著,阈值电压下降[1],泄漏电流增大,静 态功耗增加,这些都将严重影响器件的性能,双栅及 三栅 FINFET 新结构器件[2],增强了栅控能力,可 以有效抑制短沟效应,由于增加了栅的数目,加强了 栅对沟道的控制,晶体管的驱动电流相应增大.对于 FINFET 双栅结构,随着栅电压的增大,源漏之间开 始有较小的漏电流,当栅电压进一步增大,达到器件 的阈值电压时,沟道区两侧硅表面形成反型层,即器 件在沟道两侧都形成反型沟道,源漏导通,器件工 作[3], 在 FIN 厚度很薄以致全耗尽状况下, 增加很 小的栅压就会使表面势急剧增加,在反型层中聚集 的载流子增加,使得器件能获得近平理想的亚阈值 特性[4]. 同时,由于工作时存在两个导电沟道(FIN 薄时两者都有所影响),使得源漏电流远远大于普通 体硅 MOSFET, 因此具有较好的驱动能力[5].

本文对 FINFET 中的双栅和三栅结构进行三维模拟,通过对比两者的特性,分析了栅的数量对器

件特性的影响.

## 2 器件结构及模拟方法

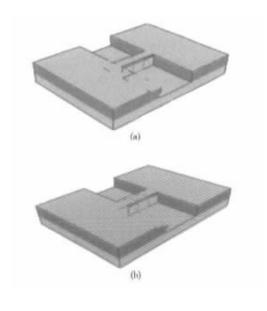

图 1(a)和(b)分别是模拟中采用的双栅和三栅 FINFET 结构,该结构两边大的部分为源漏,深色区

图 1 (a)双栅结构简图;(b)三栅结构简图 Fig. 1 (a) DGs structure diagram;(b) TGs structure diagram

<sup>\*</sup> 国家重点基础研究专项经费资助(No. G20000356)

夏志良 男,1980年出生,硕士研究生,主要从事器件的模型与模拟,

为硅膜, 硅膜高度为  $T_{\rm SiO_2}$ ,中间条形区分为三部分,条形区中间部分为实际的沟道区,而两端则为源漏的延伸. 从图中可以看到,条形区两侧矩形为栅所在位置,FINFET 双栅结构,栅分别在条形区两侧,而顶部没有栅电极,两栅之间的距离为  $T_{\rm body}$ ,沟道长度  $L_{\rm gate}=25{\rm nm}$ . FINFET 三栅与双栅惟一的不同就在于多了一层顶栅,其参数与双栅结构相同. 在模拟时,源漏掺杂均为  $10^{20}{\rm \,cm}^{-3}$ ,沟道掺杂为  $10^{16}{\rm \,cm}^{-3}$ , $T_{\rm SiO_2}$ 为  $25{\rm nm}$ , $T_{\rm SiO_2}$ 为  $25{\rm nm}$ , $T_{\rm SiO_2}$ 为  $25{\rm nm}$ ,有效从  $20{\rm nm}$ ,其它参数依模拟的需要分别在图中给出. 模拟采用 ISE 软件中的三维模拟部分.

#### 3 模拟结果与讨论

为了对比不同数目栅的 FINFET 结构特性上的差异,分别模拟了不同侧栅间距下双栅和三栅结构的器件特性.

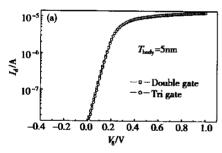

图 2(a)和(b)分别是  $T_{\rm body}$ 等于  $5{\rm nm}$  和  $20{\rm nm}$  时的双栅和三栅的  $I_{\rm d}$ - $V_{\rm g}$  曲线. 从图中可以看出,在  $T_{\rm body}$ 比较小的时候,双栅和三栅之间的差异较小,但是当  $T_{\rm body}$ 增大到和  ${\rm FIN}$  的高度相近的时候,两者之

图 2 (a)  $T_{\rm body}{=}5{\rm nm}$  时的  $I_{\rm d}{-}V_{\rm g}$  曲线; (b)  $T_{\rm body}{=}2{\rm 0nm}$  时的  $I_{\rm d}{-}V_{\rm g}$  曲线

Fig. 2 — (a)  $I_{\rm d}$ – $V_{\rm g}$  characteristics with  $T_{\rm body}$  of 5nm; (b)  $I_{\rm d}$ – $V_{\rm g}$  characteristics with  $T_{\rm body}$  of 20nm

间的差异才变得明显起来. 这主要是由于在  $T_{\text{body}}$ 小的情况下,顶栅的面积相对两个侧栅来说很小,而  $T_{\text{body}}$ 增大后,顶栅的面积已经和侧栅很相近了,所以 这时三栅的控制能力明显要比双栅的好.

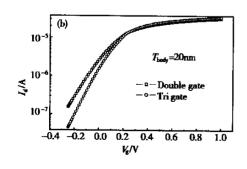

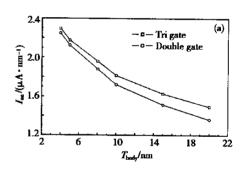

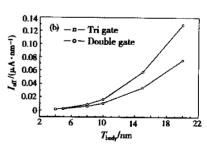

图 3(a)和(b)对比了两者平均  $T_{body}$ 下的  $I_{on}$ 和  $I_{off}$ . 结果表明,三栅的  $I_{on}$ 要比双栅的大,且随着  $T_{body}$ 的变化也较平缓.  $T_{body}$ 增大,各个栅之间的影响减小  $(T_{body}$ 足够大时,两个侧栅形成独立的导电反型层),总电流增大,但由于  $T_{body}$ 变大了,相应的平均电流反而减小.  $I_{on}$ 增大,有利于提高器件的驱动能力. 三栅的  $I_{off}$ 要比双栅小,而且随  $T_{body}$ 的变化也较缓慢, $T_{body}$ 增大,三栅的顶栅对沟道的控制所占的比例也随之增大,故  $I_{off}$ 的增大应该比双栅来得缓慢. 综合考虑  $I_{on}$ 和  $I_{off}$ ,我们可以选取合适的  $T_{body}$ ,使器件既具有良好的驱动能力,又能很好的减小泄漏电流,优化器件的性能.

图 3 (a)双栅和三栅  $I_{\text{on}}$ 的比较;(b)双栅和三栅  $I_{\text{off}}$ 的比较 Fig. 3 (a) Comparison of  $I_{\text{on}}$  of DG and TG;(b) Comparison of  $I_{\text{off}}$  of DG and TG MOSFET

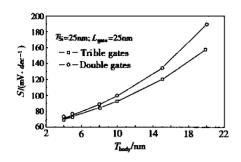

图 4 是对不同  $T_{\text{body}}$ 下的双栅和三栅的亚阈值 斜率做了对比. 从图中我们可以看出,在  $T_{\text{body}}$ 比较小的时候,双栅和三栅的亚阈值特性都很好,亚阈值 斜率 S 一般在 70 左右,而且两者的差距也很小.  $T_{\text{body}}$ 增大,两者的 S 都增大,不过,很明显,三栅要比 双栅来得缓慢. 原因主要是随着  $T_{\text{body}}$ 增大,顶栅对

沟道的控制所占的比例也越来越大,所以栅控能力 更强,从而比双栅具有更好的亚阈值特性.

图 4 双栅和三栅亚阈值斜率的比较

Fig. 4 Comparison of sub threshold slope of DG and TG MOSFET

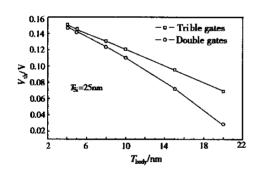

图 5 比较了双栅和三栅的阈值电压.  $T_{\rm body}$ 增大,栅极控制的耗尽层电荷减小,使阈值电压  $V_{\rm th}$ 下降,不过,三栅要比双栅下降得缓慢. 在  $T_{\rm body}$ 相同时,三栅控制的耗尽层电荷要比双栅多,所以三栅的  $V_{\rm th}$ 要比同样  $T_{\rm body}$ 下的双栅来得大些.

图 5 双栅和三栅阈值电压的比较

Fig. 5 Comparison of threshold voltage of DG and TG MOSFET

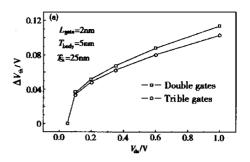

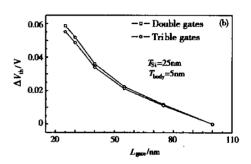

图 6(a)和(b)对双栅和三栅的短沟效应做了对比. 在图 6(a)中,纵坐标  $\Delta V_{\rm th} = V_{\rm th(V_{ds}=0.05V)} - V_{\rm th(V_{ds})}$ ,由图可知,两者的 DIBL 效应都不是很明显, $V_{\rm ds}$ 从 0.05V 增大到 1V,阈值电压只减小了不到 0.1V. 在图 6(b)中,纵坐标  $\Delta V_{\rm th} = V_{\rm th(L_{gate}=100nm)} - V_{\rm th(L_{gate})}$ ,随着  $L_{\rm gate}$ 的减小,阈值电压  $V_{\rm th}$ 减小, $\Delta V_{\rm th}$ 增大, $L_{\rm gate}$ 从 100nm 减小到 25nm,阈值电压也只减小了 0.06V. 这说明双栅和三栅结构可有效抑制器件的短沟效应,而且,两者之间的差距很小.

图 6 (a)阈值漂移随  $V_{\rm ds}$ 的比较;(b)阈值漂移随  $L_{\rm gate}$ 的比较

Fig. 6 (a) Comparison of threshold voltage rolloff for  $V_{\rm ds}$  from 0.05V to 1.0V; (b) Comparison of threshold voltage rolloff for  $L_{\rm gate}$  from 25nm to 100nm

## 4 结论

在器件进入超深亚微米以后,短沟效应变得越来越显著,采用多栅结构,短沟效应可以得到很好的抑制,关态电流变小,亚阈值特性变好,静态功耗减小,这些都很好的改善了器件的性能,为器件尺寸的进一步缩小奠定了基础. 三维模拟结果表明,只要控制  $T_{body}$ 足够小,FINFET 双栅性能可以和三栅相媲美,所以 FINFET 双栅结构现在已经成为多栅结构的主流.

#### 参考文献

- [1] Gan Xuewen, Wang Xushe, Zhang Xing. Analysis of threshold voltage decreasing for double-gate and surround-gate MOSFET's. Chinese Journal of Semiconductors, 2001, 21 (12):1581[甘学温, 王旭社,张兴. 双栅和环栅 MOSFET 中 短沟效应引起的阈值电压下降.半导体学报,2001,21(12):

- [2] Hisamoto D, Lee Wen-Chin, et al. FinFET-a self-aligned double-gate MOSFET scalable to 20nm. IEEE Trans

Electron Devices, 2000, 47(12): 2320

- [3] Shen Yinhua, Li Weihua. Research advances of double-gate MOSFET's Mioroelectronics,2000,30(5):290[沈寅华,李伟华. 双栅 MOSFET 的研究和发展. 微电子学,2000,30(5):290]

- [4] Colinge J P. Subthreshold slope of thin-film SOI MOSFET's.

IEEE Electon Device Lett, 1986, 7(4): 244

- [5] Venkatesan S, Neudeck G W, Pierrer R F. Dual-gate operation and volume inversion in n-channel SOI MOSFET's. IEEE Electron Device Lett, 1992, 13(1):410

#### 3D Simulation of Mutil-Gate MOSFET with Sub-100nm\*

Xia Zhiliang, Liu Xiaoyan, Liu Enfeng and Han Ruqi

(Institute of Microelectronics, Peking University, Beijing 100871, China)

**Abstract**: The characteristics of mutil-gate MOSFET (double gates and trible gates FINFET) are simulated systemically by using 3D simulation program ISE. The *I-V* characteristics are investigated. The results show that the performances of Tri gate MOSFET are generally superior to ones of double gate's. However, with the decreasing of the FIN's width, double gate's performances trend to Tri gatre's.

Key words: double gates MOSFET; threshold voltage; FINFET; 3D simulation; short-channel effect

**EEACC:** 2530F

Article ID: 0253-4177(2003)S0-0140-04

<sup>\*</sup> Project supported by the Special Funds for Major State Basic Research Projects (No. G20000356)

Xia Zhiliang male, was born in 1980. His research interests focus on modelling and simulation of devices.